フリースケール セミコンダクター インコーポレイテッドにより出願された特許

771 - 780 / 806

絶縁ワイヤのワイヤボンディング及びワイヤボンディングに用いるキャピラリ

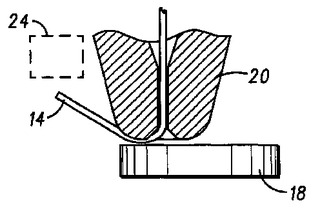

一端が第1ボンディングパッド(16)に接続される絶縁ワイヤ(14)を第2ボンディングパッド(18)にボンディングする改良型方法であって、この方法では、ボンディングワイヤ(14)を保持するキャピラリ(20)の先端を第2ボンディングパッド(18)の表面の上を移動させて、ボンディングワイヤ(14)をキャピラリ先端(20)と第2ボンディングパッド(18)との間で擦ってボンディングワイヤの絶縁を破り、ワイヤ(14)の金属コアの少なくとも一部が第2ボンディングパッド(18)に接触するようにする。次に、ワイヤ(14)を第2ボンディングパッド(18)に熱圧着ボンディングを使用して接着させる。キャピラリ(20)の先端を粗くしてボンディングワイヤの絶縁が破れ易くなるようにする。  (もっと読む)

(もっと読む)

回路電圧調整

調整された出力電圧を供給するための電圧調整回路(130)。電圧調整回路は、遠隔電圧の表示を比較して、制御信号(295)を供給するための電圧検出回路(205)を含む。電圧調整回路は、更に、制御信号に応答して出力電圧VDDを修正する調整器(270)を含む。  (もっと読む)

(もっと読む)

多状態磁気ランダムアクセスメモリセル

ワードライン(14)とディジットライン(16)の間に、2つのビット(18)と(20)が挟まれており、様々な時間に電流波形(104)と(106)をワードラインとディジットラインに加え、磁界束HWとHDによって、装置(12)の有効磁気モーメントベクトル(86)と(94)を略180度回転させることができるように作られている磁気抵抗メモリ装置(12)を提供する段階を含む、スケーラブル磁気抵抗メモリセルを切り替える方法が開示されている。各ビットは、非強磁性的に結合されているN個の強磁性層(32)、(34、42)、(44、60)及び(62、72、74)を含んでいる。Nの個数は、ビットの磁気切り替え量を変えるために調整することができる。一方又は両方のビットは、ワード及び/又はディジットラインの電流を調整することによってプログラムすることができる。 (もっと読む)

デバッグ回路のセキュリティを確保する方法及び装置

本発明はデバッグ回路(20)に関し、特にデバッグ回路(20)のセキュリティを確保する方法及び装置に関する。一の実施形態では、複数の不揮発性素子(38)を使用して、デバッグ回路(20)の少なくとも一部を選択的にディスエーブルにし、そして再イネーブルする。認証も使用することができる。本発明は、IEEEが規定するJTAGデバッグインターフェースのような標準デバッグインターフェースを含むどのようなデバッグインターフェースも使用することができる。  (もっと読む)

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

検査パッド構造を有する集積回路および検査方法

半導体装置(10)は、ワイヤボンディングのために周囲に多数のボンド・パッド(24)を有する。半導体装置(10)は、モジュール(12)およびその他の回路を有するが、モジュール(12)は検査のために他の回路よりも遥かに長い時間を必要とする。比較的少数のボンド・パッド(20)、モジュール・ボンド・パッド(20)が、少なくとも部分的に、内蔵自己検査(BIST)(16)回路を有する半導体装置によるモジュール検査のために必要である。これらのモジュール・ボンド・パッド(22)の機能性は、半導体装置(10)の上面上および内部に二重化されており、モジュール検査パッド(22)は周辺のボンド・パッド(24)よりも遥かに大きい。検査のために大きなパッド(22)を有することにより、プローブ・ニードルを長くすることができ、したがって並行検査機能が向上する。機能性の二重化は、モジュール・ボンド・パッド(20)およびモジュール検査パッド(22)が互いに短絡しなくてよいように、検査パッド・インターフェースを介して達成する。  (もっと読む)

(もっと読む)

単式プルーフマス、三軸微小電気機械式トランスデューサ

本明細書にて提供されるトランスデューサは不釣合いのプルーフマス(51)を備え、それは、互いに直交する少なくとも2方向の加速を感知するように構成されている。プルーフマス(51)は、互いに対向する第1側部(65)及び第2側部(67)を備えており、それらは異なる重量をそれぞれ有している。  (もっと読む)

(もっと読む)

分散システムにおいて処理ノードを接続する装置及び方法

故障で制御不能の処理ノードを含む分散システムにおいて処理ノードを接続する装置であって、信号を分散システムの別の処理ノードから受信する受信機手段と当該受信機手段に結合されたノード・ガーディアン手段とを備え、当該ノード・ガーディアン手段が、複数の一方向の入力信号を受信するスイッチ手段を含む。上記装置が更に、スイッチ手段に結合されて、複数の受信された入力信号を所定の論理関数に従って組み合わせる論理手段と、当該スイッチ手段に結合されて、複数の受信された入力信号の論理手段への印加を制御して、その場所での信号の受信を、分散システムの別の処理ノードからの制御不能の送信の処理ノードによる受信を低減するように制御する制御手段とを備える。  (もっと読む)

(もっと読む)

スペース効率の良い低電力循環型A/D変換器

アナログ変換器(60)用に提供される方法及び装置。この装置は第1の冗長符号桁(RSD)段(62)と構成可能ブロック(61)とを備える。構成可能ブロック(61)は、シングルエンドアナログ信号をサンプリングするためのサンプル/ホールド回路に変更される。サンプリング信号は、その後、差動信号にスケーリング及び変換され、第1のRSD段(62)に供給される。第1のRSD段(62)はデジタル信号の大きさに対応したビット値を出力する。次の半クロックサイクルで、第1のRSD段(62)は構成可能ブロック(61)に供給する残留電圧を算出する。構成可能ブロック(61)は第2の冗長符号桁段に変更され、第1のRSD段より供給された残留電圧の大きさに対応したビット値を発生する。第1及び第2のRSD段は、所望のビット分解能に達するまで、各々半クロックサイクルで論理値の発生を交互に繰り返す。構成可能ブロック(61)は、その後、次の変換処理を開始するためにサンプル/ホールド回路に再変更される。  (もっと読む)

(もっと読む)

歪み解放バンプ設計による半導体装置

半導体装置(51)が提供される。装置(51)は、コンタクトパッド(61)を上部に有するダイ(53)と、コンタクトパッド(61)に電気的に接続されるベース部(64)及び横方向延在部(63)を有する再分配導電体(59)と、再分配導電体(59)に電気的に接続されるバンプコンタクト(65)と、再分配導電体(59)の横方向延在部(63)及びダイ(53)の間に配置されるパッシベーション層(57)とを備える。好ましくは、再分配導電体(59)は、渦巻形状を有し、十分な応力下で、パッシベーション層(57)から剥離、即ち層間剥離して、パッシベーション層(57)及びベース部(64)に対して移動することにより、基板(69)とダイ(53)との間の機械的な応力を解放するように構成される。不具合を生じることなく、小さいCTE差による歪みに対処するバンプ及びコイル状の再分配導電体(59)によって、アンダフィルを用いずに、又は追加のアセンブリ工程を経ることなく、DCAフリップチップの信頼性を高くすることができる。  (もっと読む)

(もっと読む)

771 - 780 / 806

[ Back to top ]