フリースケール セミコンダクター インコーポレイテッドにより出願された特許

791 - 800 / 806

動的プリフェッチ・バッファ構成および置換のための方法および装置

異なるバーストをサポートする複数のバス・マスタ(12,14,16)と、異なる特性を有する複数のメモリとの間でインタフェース接続するために、動的にプリフェッチ・バッファ(30)を構成するメモリ制御装置(32)およびその方法。プリフェッチ・バッファ(30)の少なくとも一部のライン・サイズが、バス・マスタ(12,14,16)のうちの1つからの読出し要求を受信するメモリ制御装置に基づいて修正される。プリフェッチ・バッファ・ラインを最適に置換するための適応方法は、どのバッファ・ラインを置換するべきかを決定するために、優先順位順の状態(状態)フィールド情報を使用する。  (もっと読む)

(もっと読む)

光ディスク・ドライブの光ピックアップ・ユニットに対する作用抑制技術

本発明は、光ディスク・ドライブの性能を改善するための低コストの技術を提供する。アルゴリズムを使用して、電気機械式アクチュエータを作用抑制し、アクチュエータ(308,310)の制御の際の誤差を補償する。位置センサ(316)を作用抑制するために類似の方法を使用することができる。従来技術の方法は、焦点制御ループ、トラッキング制御ループおよびスレッド制御ループの間の相互作用をノイズとして処理したために、システムの帯域幅が広くなり、光ディスク・ドライブのコストが増大した。本発明は、光ディスク・ドライブの性能を改善するために、ソフトウェア・アルゴリズムを使用して制御ループを能動的に作用抑制する。アクチュエータを作用抑制するために、相互作用効果が測定され、作用抑制マトリックスが決定され、制御系の出力が修正される。  (もっと読む)

(もっと読む)

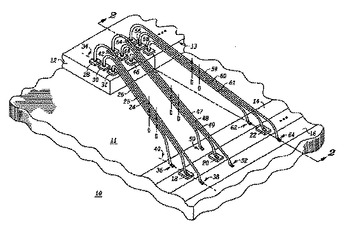

ワイヤ・ボンドの位置付けを最適化した半導体パッケージ

密接配置したボンディング・ワイヤを種々の異なるパッケージング用途に用いると、電気的性能の向上を図ることができる。一実施形態では、ワイヤ群内にある2本の隣接するボンディング・ワイヤが密接配置されているのは、2本の隣接するワイヤのうちの短い方の長さの少なくとも50パーセントで、これら2本の隣接するワイヤ間において分離距離Dが満たされる場合である。一実施形態では、分離距離Dは、2本の隣接するワイヤのうちの直径が大きい方のワイヤの直径の多くとも2倍である。別の実施形態では、分離距離Dは、2本の隣接するワイヤ間のワイヤ間ピッチの多くとも3倍である。各ワイヤ群は、2本以上の密接配置ワイヤを含むことができる。密接配置ボンディング・ワイヤのワイヤ群を用いると、例えば、電力−信号−接地の三重組、信号−接地対、信号−電力対、あるいは差動信号対または三重組を形成することができる。  (もっと読む)

(もっと読む)

高インピーダンス無線周波数出力プラスチックパッケージ

本明細書の開示はRF出力半導体デバイスに関する。本明細書に開示の一実施形態において、RF出力プラスチック半導体デバイス(10)は、半導体(RF)デバイス(12)、RFデバイスに電気的に接続されている低温同時焼成セラミックス(LTCC)インピーダンスマッチング構造体(14)、並びにRFデバイス及びインピーダンスマッチング構造体の上方に形成されているプラスチックパッケージ本体(22)を備える。LTCCインピーダンスマッチング構造体は、インピーダンスマッチング構造体の主要本体部分の上方に位置する金属化層(28,36)と、金属化層上のパッシベーション層(44)からなる。パッシベーション層により、金属化層に対するプラスチックパッケージ本体の金型成形コンパウンドの結合強度が増大する。LTCCインピーダンスマッチング構造体とRFデバイスとの間に電気的な相互接続部が形成されるように、金属化層のうちの一部はパッシベーション層を通じて露出される。好適には、本明細書に開示の実施形態によるRF出力プラスチックパッケージは、従来のRF出力プラスチックパッケージの終端インピーダンスの約2倍以上の終端インピーダンスを示す。  (もっと読む)

(もっと読む)

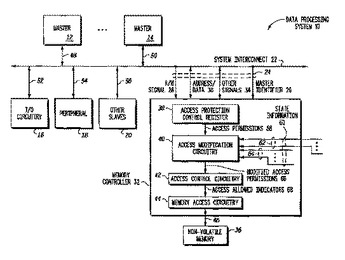

アクセス許可を決定するための方法および装置

複数のマスタ(12,14)に対応する複数のアクセス要求(84)を受信するステップと、アクセス許可(86)を決定するステップと、状態情報(60)を提供するステップと、アクセス要求(84)に基づいてアクセス許可(86)を決定ステップと、状態情報(90)に基づいてアクセス許可を選択的に修正するステップと、を含むアクセス保護(96)を決定するための方法および装置。状態情報(60)は、デバッグ動作、非セキュアまたは検証されていないメモリからの動作、メモリ・プログラミング、ダイレクト・メモリ・アクセス動作、ブート動作、ソフトウェア・セキュリティ検査、セキュリティ・レベル、セキュリティ監視動作、動作モード、障害監視装置、外部バス・インタフェース等(88)と関連することができる。  (もっと読む)

(もっと読む)

キャッシュに適用可能な読み込みアクセス及び記憶回路の読み込み割り当て

読み込みアクセスについて読み込み割り当てが実行されるかどうかを選択的に決定する為に、読み込み割り当て標識(例えば、読み込み割り当て信号30)が記憶回路(例えば、キャッシュ22)に供給される。読み込み割り当てには、キャッシュ(22)の情報の内容の修正及び/又はキャッシュ(22)で読み込み割り当て回路(70)により実施される読み込み交換アルゴリズムの状態の修正が組み込まれている。デバッグ操作の特定のタイプについては、読み込みアクセス中に記憶回路に望ましくない修正がなされないことを確実にする読み込み割り当て標識を供給することが非常に有用である。デバッグ操作の更なる他のタイプでは、読み込みアクセスが起きたときには記憶回路が標準的なやり方で修正されることが望まれる。  (もっと読む)

(もっと読む)

電荷蓄積場所を有するメモリ

メモリは、チャネル領域(1725)を含む半導体構造(1105)の対向する側壁に隣接するゲート構造と、ゲート構造と対向する側壁との間にある複数の電荷蓄積場所(1713、1715、1709及び1711)とを有する。チャネル領域は、2つの電流端子領域間に配置され、それらの電流端子領域は一例ではソース/ドレイン領域としての役割を果たす。メモリセルは、メモリセルのアレイ(1801)内に実装することができ、一方のゲート構造が1つのワード線に結合され、他方のゲート構造が別のワード線に結合される。一例では、各セルは、それぞれが1ビットのデータを記憶する、4つの電荷蓄積場所を含む。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

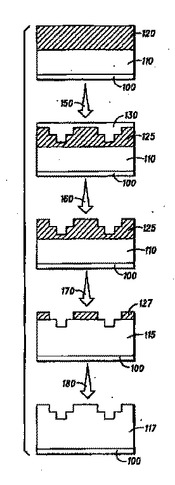

インプリント・リソグラフィによる単一デュアルダマシン製法

インプリント・リソグラフィと共に多段構造を有するテンプレートを用いるデュアルダマシン構造の製造方法の一例は、多段構造を有するリソグラフィ用テンプレート(130)をレジスト層(120)と接触するように配置するステップ(ステップ150)と、テンプレート(130)に圧力を加えることによりレジスト材料(120)がテンプレート(130)のレリーフパターン内に流れ込み、パターン化されたレジスト層(125)が形成されるステップと、そのパターン化されたレジスト層(125)を必要に応じて硬化するステップと、テンプレート(130)をパターン化されたレジスト層(125)から取り外すステップ(ステップ160)と、及びパターニング層(117)にビアやトレンチを作製するためパターン化されたレジスト層(125)をエッチングするステップ(ステップ170,180)とからなる。開示された特徴や仕様は、デュアルダマシン構造や他の多段構造の作製を改良したり、他の方法で最適化したりするため、様々に制御したり、設定したり、適合させたり、他の方法で部分的に変更したりしてもよい。  (もっと読む)

(もっと読む)

周辺装置アクセス保護付きデータ処理システム

データ処理システム(10)には、相互接続(22)が含まれ、第1相互接続マスタ(12)及び第2相互接続マスタ(14)が、その相互接続に接続される。共有記憶装置(35)は、その相互接続に接続され、第1相互接続マスタ及び第2相互接続マスタによって用いられる。また、このデータ処理システムには、第1相互接続マスタに対応する第1制御記憶回路(60,64)と、第2相互接続マスタに対応する第2制御記憶回路(62,66)とが含まれる。一実施形態において、プリフェッチ回路(40)は、第1制御記憶回路及び第2制御記憶回路に接続され、第1相互接続マスタ及び第2相互接続マスタのうちのどちらが、共有記憶装置へのアクセスを要求しているかに基づき、第1制御記憶装置及び第2制御記憶回路のうちの一方を選択する。次いで、プリフェッチ回路は、選択した制御記憶回路を用いて、共有記憶装置へのアクセスによってトリガされるプリフェッチ動作を決定する。  (もっと読む)

(もっと読む)

791 - 800 / 806

[ Back to top ]