フリースケール セミコンダクター インコーポレイテッドにより出願された特許

781 - 790 / 806

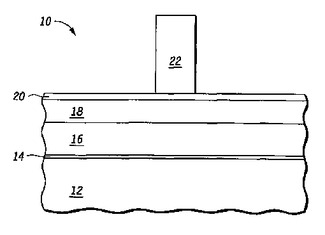

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

不揮発性メモリおよびその製造方法

トランジスタの制御ゲート(28)およびウェル領域(12)に、それぞれ、第1および第2の電圧を印加するステップを含む不揮発性メモリのトランジスタ(10)の電荷蓄積場所から放電するための方法。第1の電圧はトランジスタの制御ゲートに印加され、制御ゲートは、トランジスタの選択ゲート(18)に隣接して位置する一部を少なくとも有する。トランジスタは、制御ゲートの下に位置するトランジスタの構造の誘電体(22,26)内に配置されたナノクラスタ(24)を有する電荷蓄積場所を含む。最後に、第2の電圧が、制御ゲートの下に位置するウェル領域(12)に印加される。第1の電圧および第2の電圧の印加により、電荷蓄積場所のナノクラスタから電子を放出するために前記構造の両端に電圧差が発生する。  (もっと読む)

(もっと読む)

ネットワーク・ノード

第1のネットワーク(11)のための第1のネットワーク・タイミング情報を第2のネットワーク(12)のための第2のネットワーク・タイミング情報と比較し、且つ前記第1のネットワーク・タイミング情報と前記第2のネットワーク・タイミング情報との差の符号を前記第1のネットワーク(11)に通信して、前記第1のネットワーク(11)が前記差の符号を用いてそのネットワーク・タイミング情報を変えるのを可能にして、前記第1のネットワーク(11)と第2のネットワーク(12)との間のネットワーク・タイミング差を低減するのを可能にする同期化装置(21)を備えるコンピュータ・ノード(16)である。  (もっと読む)

(もっと読む)

スペース効率の良い低電力循環型A/D変換器

アナログ変換器(60)用に提供される方法及び装置。この装置は第1の冗長符号桁(RSD)段(62)と構成可能ブロック(61)とを備える。構成可能ブロック(61)は、シングルエンドアナログ信号をサンプリングするためのサンプル/ホールド回路に変更される。サンプリング信号は、その後、差動信号にスケーリング及び変換され、第1のRSD段(62)に供給される。第1のRSD段(62)はデジタル信号の大きさに対応したビット値を出力する。次の半クロックサイクルで、第1のRSD段(62)は構成可能ブロック(61)に供給する残留電圧を算出する。構成可能ブロック(61)は第2の冗長符号桁段に変更され、第1のRSD段より供給された残留電圧の大きさに対応したビット値を発生する。第1及び第2のRSD段は、所望のビット分解能に達するまで、各々半クロックサイクルで論理値の発生を交互に繰り返す。構成可能ブロック(61)は、その後、次の変換処理を開始するためにサンプル/ホールド回路に再変更される。  (もっと読む)

(もっと読む)

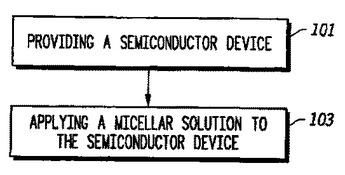

エッチング後の残渣のためのミセル技術

半導体デバイスを洗浄するための方法。この方法によれば、半導体デバイスが提供され(101)、ミセル溶液が前記半導体デバイスに塗布される(103)。この方法は、銅およびシリコン面を洗浄する際に、またバイアまたはトレンチの表面から加工残渣を除去する際に特に役に立つ。  (もっと読む)

(もっと読む)

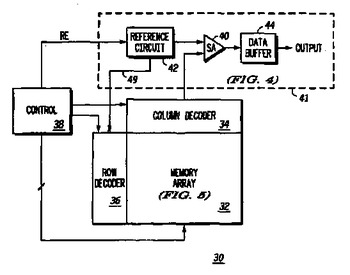

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

ワイヤレス・ネットワーク上におけるデータ・ストリームの同期

ワイヤレス・チャネルを通じてホスト・データを送信する送信機(500)が提供される。送信機(500)は、一連の増加する自走タイミング値を供給する自走タイマ(560)と、内部ホスト回路からホスト・データを、かつ一連の増加する自走タイミング値から第1自走タイミング値を受け取るホスト・インターフェース回路(510)と、大域同期イベントを検出するとともに、一連の増加する自走タイミング値から第2自走タイミング値を受け、ホスト・データおよび第1自走タイミング値をホスト・インターフェース・パケットに収容する検出回路(530)と、第2自走タイミング値および大域同期イベントの識別子をホスト・インターフェース・パケットに追加してエア・リンク・フレームを形成するとともに、ワイヤレス・チャネルを通じてエア・リンク・フレームを遠隔ワイヤレス装置に送信するワイヤレス送受信機(530)とを含む。  (もっと読む)

(もっと読む)

MRAMセルのための磁気異方性を誘導するための斜め堆積

表面を有する基板を提供するステップと、前記基板上に合成磁気モーメントベクトルを有する第1磁気領域(17)を堆積するステップと、前記第1磁気領域上に電気絶縁材料(16)を堆積するステップと、前記電気絶縁材料上に第2磁気領域(115)を堆積するステップを備えた磁気抵抗トンネル接合セルを製造する方法であって、前記第1磁気領域および第2磁気領域の一方の少なくとも一部分が、前記基板の表面に直交する方向に対して非ゼロの堆積角で該領域を堆積することによって形成されて誘導異方性を作る方法。  (もっと読む)

(もっと読む)

複合磁気フリー層を有する磁気エレクトロニクス情報デバイス

磁気エレクトロニクス情報デバイス(12)は、2つの多層構造(24,26)及び該2つの多層構造の間に配置されたスペーサ層(28)を備えている。各多層構造は、2つの磁気副層(38,40及び44,46)と、該2つの磁気副層の間に配置されたスペーサ層(42,48)とを有している。2つの磁気副層の間に配置されたスペーサ層は、飽和領域によって定量化される反強磁性交換結合を提供する。2つの多層構造の間に配置されたスペーサ層は、前記第1飽和領域よりも小さい他の飽和領域によって定量化される第2反強磁性交換結合を提供する。  (もっと読む)

(もっと読む)

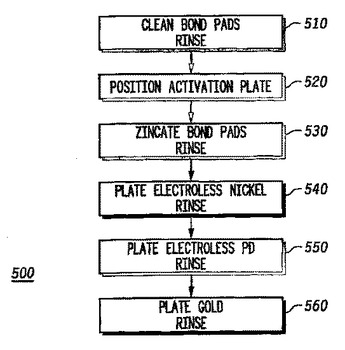

活性化プレートを用いる集積回路の無電解及び浸漬メッキ

本発明は、集積回路のメッキ方法を提供する。活性化プレートが、少なくとも一つの集積回路に隣接して配置される。集積回路は、接着パッド金属からなる複数の接着パッドを備え、また、活性化プレートも前記接着パッド金属からなる。無電解ニッケル層は、接着パッド及び活性化プレート上にメッキされ、金層は、接着パッド及び活性化プレート上の無電解ニッケル層を覆うようにメッキされる。活性化プレートを用いてメッキされた接着パッドを有する集積回路、ならびに集積回路をメッキするシステムについても開示されている。  (もっと読む)

(もっと読む)

781 - 790 / 806

[ Back to top ]