フリースケール セミコンダクター インコーポレイテッドにより出願された特許

761 - 770 / 806

テンプレート層構成

ひずみ半導体層を形成するためのプロセス。かかるプロセスは、ウェハを加熱しながら、当該ウェハの上にわたって塩素ベアリングガス(例えば、塩化水素、塩素、四塩化炭層、及び、トリクロロエタン)を流すことを含む。ある実施例では、ひずみ半導体層(例えば、ひずみシリコン)を形成するためのテンプレート層として使用される半導体層に圧縮プロセスをする間、塩素ベアリングガスが流される。他の実施例では、圧縮操作の後、前記ウェハのポストベーク中、塩素ベアリングガスが流される。

(もっと読む)

(もっと読む)

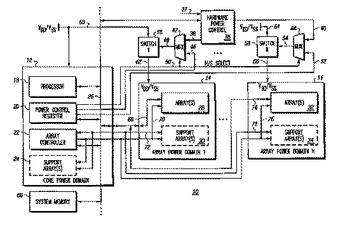

回路アレイの漏れ電流を低減するための集積回路電力管理及びそのための方法

漏れ電流は、メモリ・アレイ(28)とインターフェースするプロセッサ(18)を有する処理システム(12)の低電力モードの間に当該メモリ・アレイの中で排除される。2つの電力プレーンが生成されるので、プロセッサ(18)は、アレイがパワーダウンされるときメモリ・アレイ(28)をバイパスしながら、システム・メモリ(80)を用いて命令を実行し続け得る。スイッチ(56)が、命令の実行から、又はプロセッサ以外のどこかのシステムで発生するソースから結果として生じるプロセッサにより開始された制御に応答して電圧供給端子に対する電気接続を選択的に取り去る。メモリ(28)への電力が回復すると直ぐに、データは、メモリ・アレイに対する2つの電力プレーン・サポート・アレイのうちのどちらが配置されるかに依存して使用不能として印をされることが必要であっても、又はなくてもよい。所定の判定基準を用いて、電力の回復のタイミングを制御し得る。多重アレイが、漏れ電流を独立に低減するため実行され得る。  (もっと読む)

(もっと読む)

分離領域を有する半導体デバイスを形成するための方法

分離構造を有する半導体デバイス(10)を形成するための方法が漏れ電流を低減する。チャネル分離構造(32、30、34)がチャネル構造の中の漏れ電流を低減する。さらに、電流電極領域の下に電流電極誘電体分離構造(36)が形成され、電流電極(40)間の漏れを防ぐ。  (もっと読む)

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

集積回路内の複数の供給電圧でのデジタル信号の多重化

集積回路(10)は異なる供給電圧レベルで供給される複数のデジタル信号を多重化する多電圧デジタルマルチプレクサ回路(30)を含む。一例では、マルチプレクサ(30)はデジタル信号を受け取るアナログマルチプレクサ(32)と、アナログマルチプレクサ(32)の出力に結合されたレベルシフタ(40)と、多重化される信号に応じてIC上で用いられる種々の供給電圧の1つを供給する供給電圧マルチプレクサ(34)とを含む。アナログマルチプレクサ(32)の入力選択を制御するとともに、レベルシフタ(40)に正確な供給電圧を供給する供給電圧マルチプレクサ(34)の入力選択を制御するのに制御回路(38、39)が用いられる。この構成はIC上の単一のパッド(10)上に異なる電圧レベルのデジタル信号を多重化する機能を可能にする。  (もっと読む)

(もっと読む)

磁気抵抗型メモリ用書き込みドライバ

書き込みドライバ(36)は、ドライバ回路(114)に対して電圧により反映される基準電流(102)を用いる。ドライバ回路(114)を通る電流が基準電流(102)の所定の倍数であるように電圧を与えるデバイス(104)に関連して当該ドライバ回路(114)の大きさが決められる。この電圧は、ドライバ回路(114)にスイッチ(110)を介して結合される。スイッチ(110)は、書き込み線(42)がアドレスに応答してデコーダ(22)により決定されるように書き込み線を流れる書き込み電流を有することになるときドライバ回路(114)が電圧を受け取るのみであるように制御される。ドライバ回路(114)は、書き込み線(52)がそれを通る電流を有しないようにするとき積極的に使用不能にされる。高い電流に起因したグラウンド・バウンスを克服するための増強として、ドライバ回路に対する入力が、そのようなバウンスに遭遇する接地端子に容量結合されることができる。追加の増強が、増幅及びエッジ・レートの制御の利点を与える。  (もっと読む)

(もっと読む)

SIMDオペレーションを実行するデータ処理システム及び方法

様々なロード及び格納命令を用いて、多重ベクトル・エレメントをレジスタ・ファイル(構成要素34)内のレジスタとメモリ(構成要素12)との間で転送する。cntパラメータを用いて、メモリへ又はそれから転送されるべきエレメントの合計数を指示し得て、そしてrcntパラメータを用いて、レジスタ・ファイル内の単一のレジスタへ又はそれから転送され得るベクトル・エレメントの最大数を指示し得る。また、命令は、様々な異なるアドレッシング・モードを用い得る。メモリ・エレメント・サイズをレジスタ・エレメント・サイズから独立して指定し得て、それによりソース・サイズ及びデスティナーション・サイズが、命令内で異なり得る。幾つかの命令を用いて、ベクトル・ストリームが、開始され、そして条件付きでエンキューされるか又はデキューされ得る。切り捨てフィールド又は丸めフィールドを設け、それによりソース・データ・エレメントを転送するときそれらソース・データ・エレメントを切り捨て又は丸め得る。また、ソース・データ・エレメントは、転送されるとき、符号付きに又は符号無しに拡張され得る。  (もっと読む)

(もっと読む)

回路電圧調整

調整された出力電圧を供給するための電圧調整回路(130)。電圧調整回路は、遠隔電圧の表示を比較して、制御信号(295)を供給するための電圧検出回路(205)を含む。電圧調整回路は、更に、制御信号に応答して出力電圧VDDを修正する調整器(270)を含む。  (もっと読む)

(もっと読む)

多状態磁気ランダムアクセスメモリセル

ワードライン(14)とディジットライン(16)の間に、2つのビット(18)と(20)が挟まれており、様々な時間に電流波形(104)と(106)をワードラインとディジットラインに加え、磁界束HWとHDによって、装置(12)の有効磁気モーメントベクトル(86)と(94)を略180度回転させることができるように作られている磁気抵抗メモリ装置(12)を提供する段階を含む、スケーラブル磁気抵抗メモリセルを切り替える方法が開示されている。各ビットは、非強磁性的に結合されているN個の強磁性層(32)、(34、42)、(44、60)及び(62、72、74)を含んでいる。Nの個数は、ビットの磁気切り替え量を変えるために調整することができる。一方又は両方のビットは、ワード及び/又はディジットラインの電流を調整することによってプログラムすることができる。 (もっと読む)

半導体部品および半導体部品の製造方法

半導体部品は、半導体基板(110)と、半導体基板の上方のエピタキシャル半導体層(120)と、エピタキシャル半導体層内のバイポーラトランジスタ(770、870)と、エピタキシャル半導体層内の電界効果トランジスタ(780、880)とを含む。エピタキシャル半導体層の一部によって、バイポーラトランジスタのベースと電界効果トランジスタのゲートとが形成され、エピタキシャル半導体層のその一部は実質的に均一なドーピング濃度を有する。同じまたは他の実施形態においては、エピタキシャル半導体層の異なる部分によって、バイポーラトランジスタのエミッタと電界効果トランジスタのチャネルとが形成され、エピタキシャル半導体層のその異なる部分はエピタキシャル半導体層の一部の実質的に均一なドーピング濃度と同じかまたは異なる実質的に均一なドーピング濃度を有する。  (もっと読む)

(もっと読む)

761 - 770 / 806

[ Back to top ]