アトメル・コーポレイションにより出願された特許

11 - 20 / 57

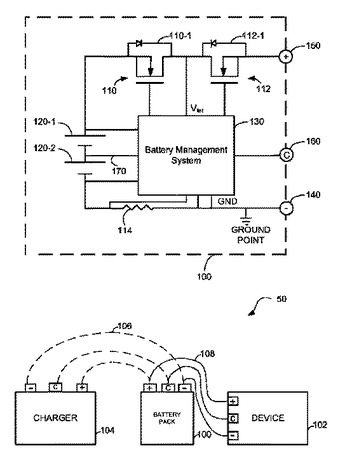

バッテリパックのためのゲートドライバ

バッテリ管理のための装置、方法、およびコンピュータプログラム製品が提供される。一実装では、方法が提供される。該方法は、充電器がバッテリシステムに結合されているかどうかの判断をイネーブルすることを含む。バッテリシステムは、1つ以上のセルと、充電可能トランジスタとを含む。また、該方法は、セルの電位よりも実質的に大きい電位で充電可能トランジスタゲート端子を駆動することを含む、充電可能トランジスタを実質的に完全にイネーブルすることを含む。  (もっと読む)

(もっと読む)

暗号化保護方法

キー混合および置換(Sボックス)演算を採用する暗号アルゴリズムのための決定論的結合方法は、真のマスク(マスク[0])およびあらゆる可能なSボックス入力に対応する複数のダミーマスクで構成されるマスキング表(マスク[0]からマスク[63])を使用する。各マスクは、キー混合演算(例えば、ビット単位のXOR)において、暗号キー(K)またはラウンドサブキー(K1からK16)に適用され、暗号アルゴリズム全体内または個別暗号ラウンド内のデータブロック(DATA)に適用される真およびダミーキーまたはサブキーを生成する。マスク値は、サイドチャネル統計的分析が、ダミーキーまたはサブキーから真のキーを判定することを阻止する。真のマスクは、外部観察者によってではなく、暗号に識別可能である。  (もっと読む)

(もっと読む)

マイクロコントローラベースのフラッシュメモリデジタルコントローラのためのファームウェアで拡張可能なコマンド

メモリコントローラのコマンドセットを拡張するためのシステムおよび方法が提供される。一実現例では、当該方法は、コマンドデコーディング状態マシンを通じて第1の複数のコマンドをデコードするステップと、コマンドデコーディング状態マシンが拡張されたコマンドをデコードすることに応答して、マイクロコントローラを立上げ、第1の複数のコマンドの中のコマンド以外の付加的なコマンドを処理するステップとを含む。拡張されたコマンドは、処理されることになる付加的なコマンドをマイクロコントローラに知らせるコマンドである。  (もっと読む)

(もっと読む)

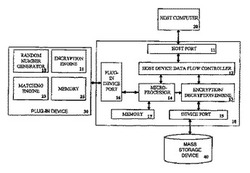

実時間鍵生成を含むデータ・セキュリティ

【課題】 よりロバストなデータ保護方法を提供する。

【解決手段】 データ・セキュリティを与える方法を提供する。セキュリティ・デバイス(10)及びプラグイン・デバイス(30)は、データの暗号化及び復号を可能にするように連動して働く。シークレットは、セキュリティ・デバイス(10)またはプラグイン・デバイス(30)のいずれか一方によって格納される。シークレットは鍵を作成することが求められるが、鍵はシークレットのみから作成されることができない。許可されていないデバイスまたはユーザは、それによって鍵へのアクセスが阻止される。

(もっと読む)

マイクロプロセッサにおけるパックされた加減演算

パックされたハーフワード加算および減算演算が、レジスタファイル(19)の指定されたソースレジスタ(REGA,REGB)の指定された上部(_T)または下部(_B)ハーフワード位置から得られるハーフワードオペランドに対して並行して行なわれる。このような演算の和および差の結果は、指定された宛先レジスタ(DST_REG)の上部および下部ハーフワード位置のそれぞれへとパックされる。マイクロプロセッサは、加算演算または減算演算のいずれかを選択されたハーフワードオペランド(OP B T,OP_A_T,OP_B_B,OP_AB)に対して行なうよう独立して選択可能な(ADDSUB_CTL_T,ADDSUB CTL B)別個のハーフワード加算器(13,15)に選択的に分割され得る加算器回路網を有する算術論理ユニット(ALU11)を含む。ALUのハーフワード加算器は、上部および下部ハーフワード位置の中から選択を行なうマルチプレクサ(21−26)の組を介してソースレジスタからオペランドにアクセスする。和および差の結果に対する2等分および飽和修正を伴う演算も与えられ得る。  (もっと読む)

(もっと読む)

ADIP情報を識別するシステム及び方法

【課題】 ADIP情報を正確に検出して識別し、光ディスクへの書き込みを制御する。

【解決手段】 光ディスク上に符号化されたADIP情報を復号化する方法、装置及びシステムが提供される。1つの方法は、ウォブル信号及びウォブルクロックを受信するステップと、ウォブルクロックを用いてウォブル信号の連続ビットを評価するステップと、評価に基づいてウォブル信号内のADIP情報の識別をトリガするステップとを含む。  (もっと読む)

(もっと読む)

選択されていないセルの妨害を防止するための書き込み操作中のリカバリトランジスタの使用

選択されたビットラインと選択されていないビットラインの間の寄生結合を排除し、選択されていないビットラインのメモリセルを保護するメモリアレイ内の書き込み操作を実行するためのメモリアレイおよび方法。メモリアレイ(100)は、複数のメモリセル(148、150、152、154)を有し、それぞれ固有のアレイビットライン(104、106、108、110)に結合する。固有のリカバリトランジスタ(138、140、142、144)は、それぞれのアレイビットライン(104、106、108、110)に結合する。奇数のビットライン(140、144)のリカバリトランジスタ(140、144)は、第1および第2の電圧(128、144)に結合し、偶数のビットラインのリカバリトランジスタは、第1および第3の電圧(128、126)に結合する。書き込み操作中、選択されていないビットラインに結合したそれぞれのリカバリトランジスタは、書き込み操作およびリカバリ操作中にアクティブになり、選択されたビットラインに結合したそれぞれのリカバリトランジスタは、リカバリ操作中にアクティブになる。第1の電圧(128)は、書き込み操作中の選択されたビットラインと選択されていないビットラインの間の寄生結合を防止するには十分である。  (もっと読む)

(もっと読む)

フラッシュまたはEEアレイをプログラミングするための、アレイソース線(AVSS)制御高電圧調節

フラッシュメモリアレイをプログラミングするための方法は、電流源(410)および電位源のうちの少なくとも1つを、フラッシュメモリアレイのうちの少なくとも1つの選択されたビットライン(BL)に結合するステップと、コンパレータ(430)を使用してアレイVSS線(AVSS)の電位VAVSSを監視するステップと、電位VAVSSが基準電位Vrefとほぼ等しくなるまで、アレイVSS線(AVSS)を、電気的に浮遊させるステップと、電流源(430)および電位源のうちの少なくとも1つを切り離すことによりプログラミングを終了するステップと、を含む。  (もっと読む)

(もっと読む)

マイクロコントローラに基づくフラッシュメモリデジタルコントローラシステムのためのコマンドデコーダ

マイクロコントローラに基づフラッシュメモリデジタルコントローラシステムくのために使用されるコマンドデコーダは、ユーザからのコマンドを解釈し、コマンドの優先順位およびコマンドモードを管理するための主要ユーザインターフェースとして機能するコマンドデコーダ等、複数のサブシステムを含む。また、コマンドデコーダは、プログラムバッファ、バースト読み込みモジュール、レジスタクロック、マイクロコントローラ等の他のサブシステムによって使用されるアドレス、データ、オペコード、および種々のフラグレジスタを含む重要な情報を格納する。さらに、コマンドデコーダは、クロック同期論理を含み、マイクロコントローラのスリープ機能を制御し、テストモードコントローラとして機能する。  (もっと読む)

(もっと読む)

マイクロコントローラによるフラッシュメモリデジタルコントローラシステム

タイムドイベンツに対処するためのマイクロコントローラと、ユーザコマンドを解釈するためのコマンドデコーダと、フラッシュメモリのバースト読み取りに対処するための個別バーストコントローラと、前記フラッシュメモリへのページ書き込みに対処するためのプログラムバッファと、フラッシュコアから前記プログラムバッファへのデータ転送、ならびに前記プログラムバッファから前記フラッシュメモリへのページ書き込みのためのアドレス制御に対処するためのページ転送コントローラと、メモリ管理およびメモリ試験モード信号を格納および調整するためのメモリ管理レジスタブロックと、前記フラッシュメモリ内へアドレスを多重化し、プログラム、消去、および復旧検証を加速するためのメモリプレーンインターフェースと、システムからデータを多重化するためのI/O Muxモジュールと、試験およびデバッグで使用するために前記マイクロコントローラによって読み取りおよび書き込みすることができる汎用I/Oポート(GPIO)と、を含むデジタル制御システム。 (もっと読む)

11 - 20 / 57

[ Back to top ]