アルテラ コーポレイションにより出願された特許

81 - 90 / 163

プロセッサでの条件付き実行をサポートする装置及びその方法

【課題】SIMDアレイプロセッサの各処理要素(PE)中で条件付き実行をサポートさせる。

【解決手段】汎用フラグ(ACF)(571又は561)は、階層1,2または3ビットエンコーディングを使用して定義され、エンコードされる。加えられた各ビットは、前の機能性のスーパーセットを提供する。ACFの生成(578又は568)は、プログラマによって指定することができる。プログラマが、条件を転送するための処理要素の間の通信インターフェースを使用して、異なるプロセッサ中で生成された条件に基づいて1つのプロセッサ中の条件付き実行を指定することを可能にして、多数のPEは、条件情報を同時に生成することができる。多数のプロセッサアレイ中の各プロセッサは、異なるユニットをそれらのACFに基づいて条件付きで独立に動作させることができる。

(もっと読む)

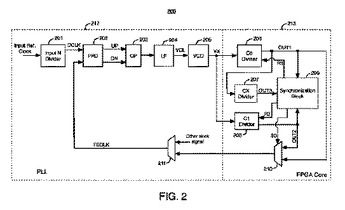

分数クロック信号を生成するための技術

回路は、位相検出回路と、クロック信号生成回路と、第1の分周器と、第2の分周器とを含む。位相検出回路は、入力クロック信号をフィードバック信号と比較して、制御信号を生成する。クロック信号生成回路は、制御信号に応答して、周期的出力信号を生成する。第1の分周器は、周期的出力信号の周波数を第1の値によって分割して、第1の分周信号を生成する。第2の分周器は、周期的出力信号の周波数を第2の値によって分割して、第2の分周信号を生成する。第1および第2の分周信号は、異なる時間間隔の間に、フィードバック信号として位相検出回路に経路指定される。  (もっと読む)

(もっと読む)

動的プログラム可能なモード切換えディバイスドライバアーキテクチャ

【課題】動的プログラム可能なモード切替えディバイスドライバアーキテクチャの提供。

【解決手段】

ディバイスドライバは、オペレーティングシステムインタフェースオブジェクトと、コンピュータインタフェースオブジェクトと、オペレーティングシステムインタフェースオブジェクトの各々によってコール可能な処理ルーチンのディバイスドライバライブラリとを有する。ディバイスドライバライブラリはプログラミング値の生成とコンピュータインタフェースへの適用を定義する実行コンテキストの選択を作動可能化する。ハードウェアインタフェースの状態は、個別のコンテキストにおいて仮想化および維持され、実質的にディバイスドライバ専用のコンテキスト切換えを介して、選択されたオペレーティングシステム事象に応答してハードウェアインタフェースの状態のアプリケーション特有の動的変更を可能にする。

(もっと読む)

回路における周波数性能を最適化する入力/出力モジュールのための装置および方法

回路は、回路と少なくとも1つの外部デバイスとの間で信号を送るように構成可能である信号パッドを有する、モジュールを含むことができる。モジュールはまた、信号パッド間に交互配置される、未使用パッドも有することができる。回路は、回路と少なくとも1つの外部デバイスとの間で可変信号を送るように構成可能である信号パッドを有する、モジュールを含むことができる。モジュールはまた、少なくとも1つの外部デバイスと回路との間で、実質的に一定の電圧を送るように構成可能である電圧パッドも有することができる。信号パッドは、電圧パッド間に交互配置することができる。これらの特徴の1つ以上を伴うモジュールは、ワイヤボンドパッケージおよびフリップチップパッケージの両方において、モジュール内での異なる入力/出力利用率の設定の融通性を伴って、理想的な性能を達成することができる。  (もっと読む)

(もっと読む)

プロセッサ装置、デュアルプロセッサを動作させる方法及びアレイプロセッサの動作方法

【課題】PEとコントローラSPとを組み合わせて単一のデバイスにし、1組の実行ユニットを共用できるようにして実現コストを削減する。

【解決手段】高度並列データ処理システムは、n個の処理要素[ユニットPE0、PE1、PE2]及びコントローラシーケンスプロセッサ(SP)[ユニット150]を含み、少なくとも1つのPEがコントローラSPと組み合わされ、2つの動作モードを支援する動的併合プロセッサ(DP)を形成する。その第1動作モードにおいて、DPは、アレイ中のPEの1つとして動作し、単一命令複数データ(SIMD)命令の実行に加わる。第2動作モードにおいて、DPは、PEのアレイに対する制御要素として動作し、非アレイ命令を実行する。これらの2つの動作モードを支援するために、DPは、複数の実行ユニット及び2つの汎用レジスタファイルを含む。

(もっと読む)

待ち時間不確実性を減少したトランシーバシステム

【課題】待ち時間不確実性を減少したトランシーバシステムを提供すること。

【解決手段】トランシーバシステムは、ワードアライナを備え、0のワードアライナ待ち時間不確実性を有し、ワードアライナに結合されるビットスリッパをさらに備えている。該トランシーバーシステムは、ワードアライナによるワード整列およびビットスリッパによるビットスリップに起因する全遅延が回復クロックのすべての位相に対して一定であるように、ビットスリッパがビットをスリップさせる、トランシーバシステムである。

(もっと読む)

高速シリアルデータ信号送信器ドライバ回路網

【課題】高速シリアルデジタルデータ信号送信器ドライバ回路網を提供すること。

【解決手段】約10Gbpsの範囲のシリアルビットレートを有する高速シリアルデータ信号を出力するための送信器ドライバ回路網であって、メインドライバステージとポストタップドライバステージとだけを有するHツリードライバ回路網を備えている、回路網であって、該Hツリードライバ回路網の一部分を形成する少なくとも1つのトランジスタが、さらに、該回路網に対する静電放電保護を提供する、回路網。

(もっと読む)

高速シリアルデータ信号のレシーバ回路網

【課題】高速シリアルデータ形式からパラレルデータ形式への良好かつ効率的なデータ変換、およびその逆のプロセスを提供すること。

【解決手段】約10Gbpsの範囲におけるシリアルビットレートを有する高速シリアルデータ信号を受信するためのレシーバ回路網であって、2ステージ、連続時間、線形の等化器であって、直列に接続された2つのステージのみを有する、等化器を備える、回路網であって、該ステージのそれぞれは、変更可能なDCゲインのパラメータ、ならびに周波数に関して位置が変更可能な極および/または零点を有し、各ステージの該DCゲインのパラメータ、ならびに該極および/または零点の位置は、プログラムによって変更可能である、回路網。

(もっと読む)

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

改良された論理セル機能性の複合論理ブロックを有するプログラマブルロジックデバイス

【課題】好適なPLDを提供する。

【解決手段】PLDと論理セルの中の一個とから成る装置であって、PLDはアレイの行と列とに配列された複数のCLBとアレイのCLBを互いに接続する複数のCLB間ラインを含み、複数のCLBの各々は論理セルの第一スライスと論理セルの第二スライスを有し、アレイに於ける一つの行のCLBの論理セルの第一スライスと論理セルの第二スライスは夫々第一搬送チエインと第二搬送チェインによって互いに接続されて居り、上記論理セルのなかの一個は、上記一個の論理セルに与えられる入力のセットに論理機能を移植するための一個以上のルックアップテーブルと、搬入信号を受信し、第一搬送チェインの一部を成す搬出信号を生成するように構成された算術論理回路と、第一出力レジスタと、第二出力レジスタとを含み、論理セルによって生成される出力のセットは第一出力レジスタと第二出力レジスタの間に分割される、装置。

(もっと読む)

81 - 90 / 163

[ Back to top ]