アルテラ コーポレイションにより出願された特許

61 - 70 / 163

ソフトエラーアップセット不感性を有する揮発性記憶素子

高エネルギーの原子粒子衝突に曝される際に、ソフトエラーアップセット事象に対して不感性を呈する記憶素子が提供される。記憶素子はそれぞれ、2つのアドレストランジスタと、双安定要素を形成するように相互接続される4つのトランジスタの対とを含む、10個のトランジスタを有してもよい。トゥルーおよびコンプリメントクリアライン等のクリアラインは、あるトランジスタの対と関連している正の電源端子および接地電源端子にルーティングされてもよい。クリア操作の際、トランジスタの対の一部または全部は、選択的にクリアラインを使用して、電力供給を停止することが可能である。これは、論理0値が、アドレストランジスタを介して駆動されるクリア操作を促進し、クロスバー電流サージを低減させる。  (もっと読む)

(もっと読む)

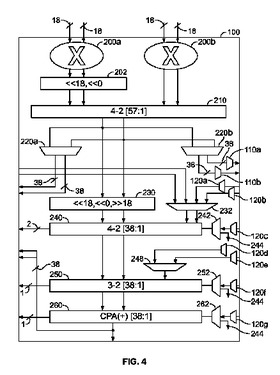

冗長および二方向データ経路を有するデジタル信号処理回路

所望の場合に、より大きな(例えば、より複雑および/またはより演算上正確な)DSP演算を行うように、より簡単に連動することができるデジタル信号処理(「DSP」)回路ブロックを提供する。これらのDSPブロックはまた、いくつかのブロックを使用できないにもかかわらず(例えば、回路欠陥のため)、複数のそのようなブロックをつなぎ合わせることを促進する冗長回路を含んでもよい。例えば、そのようなDSPブロックは、各ブロックのいずれかの側にある他のDSPブロックへ、信号を任意にまたは選択的にルーティングするルーティング回路を含んでもよい。  (もっと読む)

(もっと読む)

回路のモジュール間に選択的に使用可能な専用連結を有するモジュール式デジタル信号処理回路

所望の場合に、より大きな(例えば、より複雑および/またはより演算上正確な)DSP演算を行うように、より簡単に連動することができるデジタル信号処理(「DSP」)回路ブロックを提供する。これらのDSPブロックはまた、あるブロックを使用できないにもかかわらず(例えば、回路欠陥のために)、複数のそのようなブロックをつなぎ合わせることを容易にする冗長回路を含んでもよい。シストリックレジスタが、シストリック型の有限インパルス応答(「FIR」)デジタルフィルタを実装するよう、ブロックの使用を容易にするために、DSPブロックの中の種々のポイントに含まれてもよい。  (もっと読む)

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

【課題】プログラム可能なロジックデバイスをプログラムする方法を提供すること。

【解決手段】マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

【課題】プログラム可能なロジックデバイスをプログラムする方法を提供すること。

【解決手段】マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。

(もっと読む)

プロセス変動に対してスルーレートを補償するためのプリドライバを有する出力バッファ

【課題】補償回路とプリドライバを組み込んでおり、プロセス変動に対して補償されるスルーレートを有する出力バッファを提供する。

【解決手段】補償回路370は、演算増幅器250と、増幅器の出力に結合されたゲートを有する第2のNFET240、第3のNFET371、及び実行抵抗381から構成される。出力バッファ300は、ICチップのコア150がプリドライバ310に制御信号をアサートする。これに応答して、プリドライバ310は、第1のNFET320にバッファリングされた制御信号をアサートし、第1のNFET320をオンにし、VSSレベルの出力信号をパット230にアサートする。

(もっと読む)

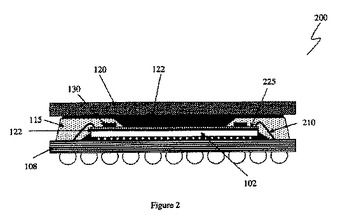

挿入層上に配置されたコンデンサーを有するICパッケージ

ダイの表面上に設置された複数のチップコンデンサーを有する集積回路(IC)パッケージが、開示される。チップコンデンサーは、挿入基板層を有するダイの最上部上に設置され得る。ダイの最上部上にチップコンデンサーを設置することは、必要とされるパッケージング基板の大きさを低減し得る。一つ以上のワイヤーが、挿入層上のチップコンデンサーをパッケージング基板に接続するために使用され得る。ICパッケージは、蓋とダイの最上部上に設置された熱インタフェイス材料(TIM)とを含み得る。蓋は、蓋の突出部がTIMを介してダイに直接接触するように形成されることにより、熱放散を改善し得る。  (もっと読む)

(もっと読む)

プログラマブルロジックデバイス回路に結合されるクロックデータリカバリ回路

【課題】プログラマブルロジックデバイス上またはこれと結合して設けられるクロックデータリカバリ回路を提供すること。

【解決手段】プログラマブルロジックデバイス(“PLD”)が多数のCDRシグナリングプロトコルのうちの任意のものによって交信することを可能にするため、このPLDにプログラマブルクロックデータ復元(“CDR”)回路を装備する。CDR回路は、PLD内に内蔵するか、完全あるいは部分的に独立した集積回路とすることができる。この回路は、CDR入力、CDR出力、またはそれらの両方を行うことができる。CDR機能は、例えば非CDR低電圧作動シグナリング(“LVDS”)等のその他の非CDRシグナリング機能と組合わせて提供することができる。この回路は、大規模なシステムの一部とすることができる。

(もっと読む)

再構成可能なプログラマブルロジックデバイスコンピュータシステム

【課題】プログラマブルロジックに基づいた再構成可能なコンピュータシステムを提供する。

【解決手段】アプリケーションを作成するためにシステム設計言語を使用する。アプリケーションは、ソフトウェア要素とプログラマブルロジックリソース要素とに自動的に分割される。システムリソースをスケジューリングおよび配分するために仮想コンピュータオペレーティングシステムが使用される仮想コンピュータオペレーティングシステムは、システム内のプログラマブルロジックリソースの能力を増加させるための仮想ロジックマネージャを含んでいる。

(もっと読む)

相変化メモリデバイスを有する分圧器を含む不揮発性メモリ回路

第一相変化メモリ(PCM)デバイス、および第一PCMデバイスに結合された第二PCMデバイスを有する分圧器を含むメモリ回路を記述する。1つの実施形態では、第一PCMデバイスはセット抵抗の状態にあり、第二PCMデバイスはリセット抵抗の状態にある。また、1つの実施形態では、分圧器は、更に、第一PCMデバイスに接合された第一スイッチ、ならびに第一スイッチおよび第二PCMデバイスに結合された第二スイッチを含む。1つの実施形態では、メモリ回路は、更に、分圧器に結合されたハーフラッチ、ならびにハーフラッチおよび分圧器に結合されたカスケードトランジスタを含む。  (もっと読む)

(もっと読む)

61 - 70 / 163

[ Back to top ]