アルテラ コーポレイションにより出願された特許

71 - 80 / 163

プログラム可能高速入出力インターフェース

【課題】高速と低速の両方で柔軟な入出力を実現する方法および装置を提供すること。

【解決手段】高速入力、高速出力、中低速の入力、中低速の出力を有する入出力構造が提供される。入力回路と出力回路の一方が選択され、もう一方が選択解除される。高速入出力回路は、例えば制御ライン入力に対してクリア信号のみを有して比較的単純であり、集積回路のコア内部の低速回路構成にインターフェースすることができる。中低速入力および出力回路は、例えば制御ライン入力としてプリセット、イネーブルおよびクリアを有してより柔軟であり、JTAGバウンダリ・テストを支援することができる。これらの並列の高速回路および低速回路はユーザによって選択可能であり、したがって、アプリケーションの要件によって、入出力構造は速度と機能の間で最適化される。

(もっと読む)

静電気放電保護構造を有するフォトリソグラフィレクチル

静電気放電保護特徴を有するフォトリソグラフィレクチルを提供する。フォトリソグラフィレクチルは、溶融シリカ等の透明基材上のクロム構造等の金属構造から形成され得る。レクチル上の金属構造のうちのいくつかは、反復焼き付けリソグラフィツールでレクチルを使用する時に製作される、集積回路上のトランジスタおよび他の電子デバイスに対応する。これらの金属デバイス構造は、レクチルの取り扱い中の静電荷蓄積による損傷の影響を受けやすい場合がある。損傷を防止するために、ダミーリング構造が、デバイス構造の付近に形成される。ダミーリング構造は、静電気放電の場合において、損傷が、重要ではないレクチルの部分に限定されるように、デバイス構造よりも静電気放電に対して敏感に構築され得る。  (もっと読む)

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

【課題】プログラム可能なロジックデバイスをプログラムする方法を提供すること。

【解決手段】マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。

(もっと読む)

診断のためにダイナミックなアナログテストマルチプレクサーを利用するシステムのアナログ信号をデジタル化するための方法

アナログブロック内のアナログ電圧をモニターすることを可能にする集積回路が示される。集積回路は、アナログテストマルチプレクサー(mux)を有し、その入力が、アナログブロック内の関心のアナログ電圧に接続される。アナログテストマルチプレクサーは、アナログブロックからの選択されたアナログ電圧をアナログテストmuxの出力に指示する。集積回路は、選択ビットをアナログブロック内のアナログ電圧へのランダムアクセスを可能にするアナログテストマルチプレクサーに提供するアナログモニターステイトマシンをさらに含む。集積回路は、アナログテストマルチプレクサーからの選択されたアナログ電圧をデジタル表示に変換するためのアナログ−デジタルコンバーターも含む。  (もっと読む)

(もっと読む)

信号調節受信器回路網

【課題】通信経路から受信されるデジタル信号を調節するための技術を提供すること。

【解決手段】通信経路から受信される信号を調節するためのシステムおよび方法が開示される。受信器は、信号の周波数成分の少なくとも一部を減衰する通信経路から信号を受信できる。受信器は、受信される信号の周波数コンテンツの少なくとも一部を調節する等化ブロック、正規化された信号振幅および/または正規化されたエッジスロープを提供する信号正規化ブロック、および制御ブロックを含み得る。一実施形態においては、制御ブロックは、高周波数に対する等化ブロックにおける周波数調節を制御するが、低周波数に対しては制御しない。低周波数調節に対して、制御ブロックは、信号正規化ブロック内の正規化された信号振幅を制御する。このようにして、低周波数コンテンツに対する制御された調節は、信号正規化ブロックにおいて実行される。

(もっと読む)

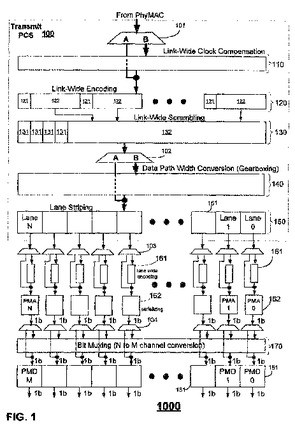

集積回路中のマルチプロトコルチャネル統合された構成可能送受信機

本開示の実施形態は、受信および/または送信回路の構成可能配列を含むマルチプロトコル送受信機を含む。例示的送受信機は、複数の高速通信プロトコルのうちの選択された1つに相当するデータ通信を効果的に送信および/または受信に相当するように選択的に構成可能である。開示される別の実施形態は、リンクワイドクロック補償、エンコーディング/デコーディング、およびスクランブリング/デスクランブリング回路と、レーンストライピング/デストライピング回路とを含む、リンクワイド物理符号化副層(「PCS」)回路を通る構成可能データパスを含み、さらに、クロック補償、エンコーディング/デコーディング、受信ブロック同期、および物理媒体アクセス副層(「PMA」)回路と、を含む、レーンワイド回路を含み、さらに、物理的媒体依存(「PMD」)副層回路に連結される、ビットマルチプレクシング/デマルチプレクシング回路を含む。  (もっと読む)

(もっと読む)

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

発振回路は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ、コンデンサ、およびオプションコンダクタも含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。  (もっと読む)

(もっと読む)

単一のプロセスを用いて高性能ロジックおよびアナログ回路をイネーブルするプロセス/設計方法論

順方向バイアスおよび修正された混合信号プロセスを用いた回路設計を用いて、アナログ回路性能を向上させる方法が提示される。複数のNMOSトランジスタおよびPMOSトランジスタを含む回路が規定される。NMOSトランジスタのボディ端子は、第1の電圧ソースに連結され、PMOSトランジスタのボディ端子は、第2の電圧ソースに連結される。回路内のトランジスタは、各選択されたNMOSトランジスタのボディ端子に該第1の電圧ソースを適用することと、各選択されたPMOSトランジスタのボディ端子に該第2の電圧ソースを適用することとによって、選択的にバイアスされる。一実施形態において、第1の電圧ソースおよび第2の電圧ソースは、順方向バイアスおよび逆方向バイアスをトランジスタのボディ端子に提供するように修正可能である。  (もっと読む)

(もっと読む)

高速シリアルインターフェイス受信器回路における自動較正

シリアルデータ信号(例えば、高速シリアルデータ信号)を受け取る回路が、シリアルデータ信号のイコライゼーションされたバージョンを発生させる調節可能なイコライザ回路を含む。イコライザ回路は制御可能に可変なDC利得および制御可能に可変なAC利得を含み得る。回路はイコライゼーションされたバージョンのアイの高さ、幅を示す第一出力信号、第二出力信号をそれぞれ発生させるアイ高さモニター回路、アイ幅モニター回路をさらに含み得る。第一出力信号はイコライザ回路のDC利得の制御において用いられ得る。第二出力信号はイコライザ回路のAC利得の制御において用いられ得る。  (もっと読む)

(もっと読む)

プロセッサアレイ及びその形成方法

【課題】プロセッサの並列アレイ内の処理エレメント間に高度の接続性を提供し、同時に、処理エレメントを相互接続するために必要な配線を最小限化し、かつPE間通信が遭遇する通信待ち時間を最小限化する。

【解決手段】マニフォルドアレイトポロジは、クラスタ52内に配列された処理エレメント、ノード、メモリ等を含む。クラスタは、処理エレメントを物理的に再配列することなく、組織の有利な変更を可能にするクラスタスイッチ配置構成986Aによって接続される。既存アレイ用の相互接続部の一般的な個数をかなり減少させることも達成される。容易なスケーラビリティの追加利益を伴い、高速、効率的、かつコストの点でも効果的な処理および通信が得られる。

(もっと読む)

71 - 80 / 163

[ Back to top ]