アルテラ コーポレイションにより出願された特許

41 - 50 / 163

直列接続のインダクターを有する集積回路

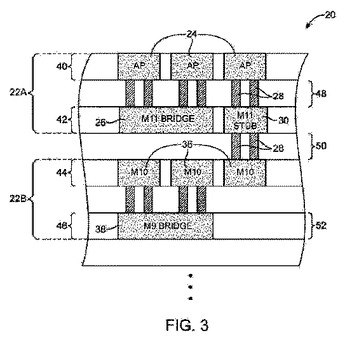

集積回路インダクターは、直列に接続されている上部ループ形状のライン部分と下部ループ形状のライン部分とを有し得る。上部部分および下部部分は、45°曲がりを有し得、6角形または8角形のループを形成する。各ループ部分は、1つ以上のターンを有し得る。金属ルーティング層の介在する金属フリー領域が、容量性カップリングを低減させるために、2つの層の間に形成され得る。各ループ部分は、ビアによって並列にショートされた2つ以上の金属ラインのセットを有し得る。上部ループおよび下部ループは、容量性カップリングを低減させるために、横にオフセットされ、または入れ子にされ得る。  (もっと読む)

(もっと読む)

離間された放熱板を有するパッケージ

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

集積回路デバイスにおける離散フーリエ変換

離散フーリエ変換を行う回路。回路は、固定論理デバイス内に提供することができる、またはプログラム可能論理デバイス等のプログラム可能集積回路デバイス内に構成することができる。回路は、離散フーリエ変換演算の入力値の仮数を加算するための浮動小数点加算段と、浮動小数点加算段の出力を回転因子で乗算するための固定小数点段と、を含む。固定小数点段は、複数のセットの回転因子を記憶するためのメモリを含み、それらのセットはそれぞれ、異なる量だけシフトされた個別の回転因子のコピーと、浮動小数点段の出力の指数間の差分を判定し、その差分をセットのそれぞれ内のその個別の回転因子のそれらのコピーから選択するためのインデックスとして使用するための回路と、を含む。  (もっと読む)

(もっと読む)

集積回路における修復可能IO

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

プログラマブル論理集積回路

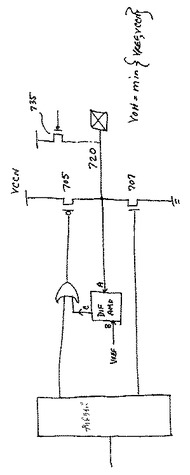

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

プログラム可能高速入出力インターフェース

【課題】高速と低速の両方で柔軟な入出力を実現する方法および装置を提供すること。

【解決手段】高速入力、高速出力、中低速の入力、中低速の出力を有する入出力構造が提供される。入力回路と出力回路の一方が選択され、もう一方が選択解除される。高速入出力回路は、例えば制御ライン入力に対してクリア信号のみを有して比較的単純であり、集積回路のコア内部の低速回路構成にインターフェースすることができる。中低速入力および出力回路は、例えば制御ライン入力としてプリセット、イネーブルおよびクリアを有してより柔軟であり、JTAGバウンダリ・テストを支援することができる。これらの並列の高速回路および低速回路はユーザによって選択可能であり、したがって、アプリケーションの要件によって、入出力構造は速度と機能の間で最適化される。

(もっと読む)

デバイスのための複数プロトコル、多重データ転送速度、自動速度交渉アーキテクチャ

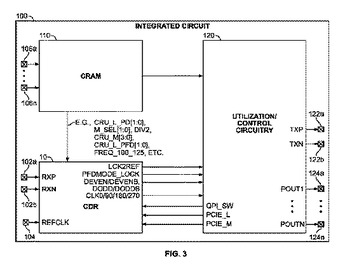

ローカルデバイスにおいて使用するためのインターフェースは、少なくとも3つのデータ転送速度にプログラマブルに構成可能な送信機部分と、少なくとも3つのデータ転送速度にプログラマブルに構成可能な受信機部分と、少なくとも3つのデータ転送速度のうちの最も可用性のある1つである単一のデータ転送速度において、遠隔デバイスと通信するために、送信機部分および受信機部分を構成するように、送信機部分および受信機部分に動作可能に接続されている自動速度交渉モジュールとを含む。データ転送速度は、送信機データパス幅および受信機データパス幅を調節し、送信機データパスおよび受信機データパスの周波数を調節し、オーバーサンプリングすることによって、調節することができる。  (もっと読む)

(もっと読む)

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

効率的プロセッサおよび関連する方法

装置は、プロセッサを含む。プロセッサは、2つのメモリを含む。第1のメモリは、一式の命令を格納する。第2のメモリは、第1のメモリにおける一式の命令より長い別の一式の命令を格納する。第1のメモリおける一式の命令おける命令は、第2のメモリおける一式の命令おける対応する命令に対するポインタとして使用される。一実施形態において、集積回路(IC)は、プロセッサを含み、プロセッサは、第2の一式の命令をアドレス指定する第1の一式の命令を格納する第1のメモリと、第2の一式の命令を格納する第2のメモリとを含み、第2のメモリは、経時的に、命令のスケジューリングを可能にするために、サイクルオフセットを含む。  (もっと読む)

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

41 - 50 / 163

[ Back to top ]