アルテラ コーポレイションにより出願された特許

11 - 20 / 163

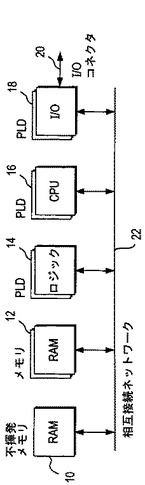

再構成可能なプログラマブルロジックデバイスコンピュータシステム

【課題】プログラマブルロジックに基づいた再構成可能なコンピュータシステムを提供す

る。

【解決手段】アプリケーションを作成するためにシステム設計言語を使用する。アプリケ

ーションは、ソフトウェア要素とプログラマブルロジックリソース要素とに自動的に分割

される。システムリソースをスケジューリングおよび配分するために仮想コンピュータオ

ペレーティングシステムが使用される仮想コンピュータオペレーティングシステムは、シ

ステム内のプログラマブルロジックリソースの能力を増加させるための仮想ロジックマネ

ージャを含んでいる。

(もっと読む)

動的ポート優先割当能力を有しているメモリコントローラー

【課題】動的ポート優先割当能力を有しているメモリコントローラーを提供すること。

【解決手段】メモリにアクセスするように動作可能な集積回路であって、該集積回路は、メモリアクセスリクエストを生成するように動作可能なプログラマブルマスター回路と、メモリコントローラーであって、該メモリコントローラーは、該メモリアクセスリクエストを該プログラマブルマスター回路から第1および第2のポートにおいて受信するように動作可能であり、該メモリーコントローラーは、該メモリアクセスリクエストを実行するために、該メモリにアクセスするように動作可能であり、該メモリコントローラーは、該メモリアクセスリクエストを順番に実行するように動作可能である、メモリコントローラーと、該メモリコントローラーが該メモリアクセスリクエストを実行する順番を制御するように動作可能である制御回路とを含む、集積回路。

(もっと読む)

プログラマブルロジックデバイスのための大きな乗算器

【課題】プログラマブルロジックデバイス(PLD)のための特殊処理ブロックで、単一のブロック内で実行され得るよりも大きな乗算の実行を容易にして、PLDの汎用プログラマブルリソースへの依存を低減または排除するロジックを備えるものを提供すること。

【解決手段】乗算器と、これらの乗算器の結果を加算する加算器のための回路網とを含むPLD内の複数の特殊処理ブロックは、加算する前に乗算器の結果をシフトするための選択可能な回路網を、該特殊処理ブロックに追加することによって、より大きな乗算器として構成され得る。一つの実施形態において、このことは、最終的な加算を除く全てが、特殊処理ブロック内で行われ、該最終的な加算は、プログラマブルロジック内で行われることを可能にする。別の実施形態において、追加の圧縮および加算の回路網は、最終的な加算でさえも、特殊処理ブロック内で行われることを可能にする。

(もっと読む)

埋込み浮動小数点構造を有するDSPブロック

【課題】浮動小数点機能を特殊処理ブロックの外に構築する必要性を減少させる、特殊処理ブロックを提供すること。

【解決手段】プログラマブル集積回路デバイス上の特殊処理ブロックであって該特殊処理ブロックは、第一の浮動小数点算術演算子段と、第二の浮動小数点算術演算子段と、該特殊処理ブロック内の構成可能インターコネクトであって、該構成可能インターコネクトは、該第一および第二の浮動小数点算術演算子段の各々に信号をルート付け、各々の外に該信号をルート付ける、構成可能インターコネクトとを含む、特殊処理ブロック。

(もっと読む)

プリエンファシス電圧ジッターを減少させる装置および方法

【課題】データ送信における電圧ジッターを減少させる送信器回路を提供すること。

【解決手段】第一の電流源と、該第一の電流源と第一のノードとの間に結合されている第一のフィルタと、該第一の電流源と第二のノードとの間に結合されている第二のフィルタと、第二の電流源と、該第二の電流源と第三のノードとの間に結合されている第三のフィルタと、該第二の電流源と第四のノードとの間に結合されている第四のフィルタと、該第一のノード、該第二のノード、該第三のノードおよび該第四のノードに結合されているドライバースイッチ回路などを含む、送信器回路。

(もっと読む)

プログラマブル論理の特定用途向け集積回路等価物および関連の方法

【課題】FPGAのASIC等価物をより効率的、経済的に提供すること。

【解決手段】FPGAのASIC等価物の提供は、複数のいわゆるハイブリッド論理素子(HLE)を含むASICアーキテクチャを使用することによって、促進され、より効率的、経済的に実行される。各HLEは、FPGA論理素子(LE)の完全機能の一部を提供可能である。ユーザの論理設計を実装する各FPGA LEの機能は、ユーザの論理を再合成することなく単一または複数のHLEへとマッピング可能である。必要な数のHLEだけが、各LEの関数を実行するために使用される。LE間および(1)単一のHLEまたは(2)HLE群間の1対1の等価性によって、FPGA設計とASIC設計との間のいずれの方向においてもマッピングが(再合成することなく)促進される。

(もっと読む)

プログラマブルデバイスを過電圧攻撃から守るためのシステムおよび方法

【課題】レジスタ、過電圧検出回路およびロジック回路を有しているプログラマブル集積回路デバイスを提供すること。

【解決手段】少なくとも1ビットの値を格納するように構成されているレジスタであって、該レジスタは、印加された電圧源に結合されている、レジスタと、過電圧検出回路であって、該過電圧検出回路は、該印加された電圧源によって発生された電圧を検出することと、検出された電圧がトリガー電圧よりも高いか、または等しい場合に、過電圧信号を生成することとを行うように構成されている、過電圧検出回路と、ロジック回路であって、該ロジック回路は、該生成された過電圧信号に応答して、該レジスタをクリアにするように構成されている、ロジック回路とを含む、プログラマブル集積回路デバイス。

(もっと読む)

波長ルータ

【課題】スペクトルバンドを入力ポート(12)と出力ポート(15)との間に選択的に方向付ける波長ルータを提供する。

【解決手段】上記ルータは、上記入力ポートと上記出力ポートとの間に配置された自由空間光学縦列と、経路設定メカニズム(30)とを含む。上記自由空間光学縦列は、エアスペースエレメント(20、25)を含み得るか、または、モノリシック構成であり得る。上記光学縦列は、回折格子などの分散エレメント(25)を含み、該入力ポートからの光が該分散エレメントと2回当たった後に上記出力ポートに到達するような構成にされる。上記経路設定メカニズム(30)は、ルーティングエレメントを1つ以上含み、上記光学縦列中の残りのエレメント(37)と協働して、上記スペクトルバンドのサブセットを所望の出力ポートに結合させる光路を提供する。

(もっと読む)

低電圧参照回路

【課題】低電圧で動作する参照回路を提供すること。

【解決手段】低電圧参照回路は、一対の半導体装置を有し得る。各半導体装置は、n型半導体領域と、n型半導体領域におけるn+領域と、メタルゲートと、ゲート絶縁体とを有し得る。ゲート絶縁体は、メタルゲートとn型半導体領域との間に挿入され、メタルゲートとn型半導体領域とを通りキャリアはトンネリングする。メタルゲートは、p型ポリシリコンの仕事関数と整合する仕事関数を有し得る。ゲート絶縁体は、約25オングストロームより薄い厚さを有し得る。メタルゲートは、第一の端子を半導体装置に対して形成し得る。n+領域およびn型半導体領域は、第二の端子を半導体装置に対して形成し得る。第二の端子は、接地に結合され得る。バイアス回路は、異なる電流を半導体装置に供給するために第一の端子を用い得、対応する参照出力電圧を1ボルト未満の値で提供し得る。

(もっと読む)

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

11 - 20 / 163

[ Back to top ]