Fターム[2C162AH75]の内容

電磁気プリンタ及び光プリンタ (19,948) | 共通の構成(電極、駆動素子関係) (948) | 駆動素子 (416) | 種類 (189) | トランジスタ (172) | FET(電界効果トランジスタ) (44)

Fターム[2C162AH75]に分類される特許

1 - 20 / 44

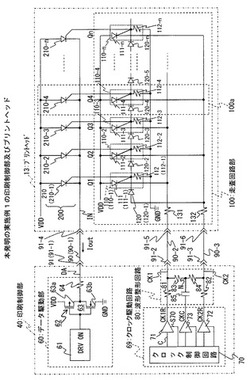

駆動装置、プリントヘッド及び画像形成装置

【課題】クロック駆動回路の出力端子数の削減により、回路規模を削減する。

【解決手段】発光サイリスタ210のカソードがLレベルにされると、アノード・カソード間には電圧が印加される。一方、走査回路部100における各走査サイリスタ111のゲートと、発光サイリスタ210の各ゲートとがそれぞれ接続されているため、走査サイリスタ111のゲート・カソード間にも電圧が印加される。この時、走査回路部100により発光指令されている発光サイリスタ210のゲートのみを選択的にHレベルとすることで、発光指令されている発光サイリスタ210がターンオンする。特に、クロック駆動回路69の3つの出力クロックパルスCK1R,CK2R,CKCを波形整形回路80で波形整形した2相のクロックCK1,CK2により、走査回路部100を駆動しているので、クロック駆動回路69の出力端子数を削減できる。

(もっと読む)

駆動回路、駆動装置、プリントヘッド及び画像形成装置

【課題】多数の発光サイリスタが並列接続されていることに起因して生じる駆動波形の遷移時間の増大を軽減する。

【解決手段】プリントヘッド13は、走査回路部100及び主発光部200を有し、これらがデータ駆動部60及びクロック駆動回路70に接続されている。主発光部200は、複数段の発光サイリスタ210により構成されている。走査回路部100は、クロック駆動回路70から供給される2相の第1、第2クロックC1,C2により駆動され、主発光部200にトリガ電流を流してオン/オフ動作させる。非発光時におけるデータ端子DAの電位を分圧抵抗64,65で分圧することにより、多数の発光サイリスタ210−1〜210−nが並列接続されていることに起因して生じる駆動波形の遷移時間の増大を軽減することが可能となる。

(もっと読む)

演算増幅器、駆動回路、駆動装置、および画像形成装置

【課題】演算増幅器(回路)には発振防止等の特性改善のために位相補償用のコンデンサを備える。MOS集積回路ではMOS容量を用いることが一般的であるが、特性が不安定、かつ大きな静電容量値がとれないという問題があった。もしくはこれを回避するためにコストアップをもたらす濃いイオン打ち込みの新たな製造工程を必要とした。

【解決手段】MOSトランジスタ、ダイオードでバイアス電圧を発生させ、コンデンサの両端にMOS容量がMOSトランジスタとしてみた場合に常時オンしている状態に相当する電位を与えて、MOS容量直下における空乏層の発生をおさえることにより、広い動作電圧範囲において、大きな容量値と安定した特性をコスト増加なしに実現する。

(もっと読む)

駆動回路、光プリントヘッド、画像形成装置及び表示装置

【課題】LED駆動電流の立ち上がり時間やその変動、それによる露光エネルギー量のばらつきといった問題を解消する。

【解決手段】LED210の駆動オンのために、入力端子Sから入力される駆動オン/オフ制御信号DRV−ON−Pが“L”レベルから“H”レベルに遷移すると、NAND回路300の出力信号が“H”レベル(=電源電圧VDD)から“L”レベル(=0V)へ遷移する。これにより、PMOS320のゲートに付随するゲート容量には、充電電流I1が流れるが、この充電電流I1は、NAND回路300の出力端子からこのNAND回路300中を経由してグランド側に流れる。即ち、充電電流I1は、マルチプレクサ171、分圧回路162、及びオペアンプ161の出力端子には流れない。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】クロック駆動回路の出力端子数の削減により、回路規模を削減する。

【解決手段】クロック駆動回路70内のオープンドレーン形インバータ80とスリーステート形出力バッファ90とにより、走査回路部100を駆動するための2相の第1及び第2クロックを生成している。発光サイリスタ210のカソードがLレベルにされると、アノード・カソード間には電圧が印加される。一方、抵抗130を介して供給される第2クロックによりシフト動作を開始する走査回路部100における各走査サイリスタ110のゲートと、発光サイリスタ210の各ゲートとがそれぞれ接続されているため、走査サイリスタ110のゲート・カソード間にも電圧が印加される。この時、走査回路部100により発光指令されている発光サイリスタ210のゲートのみを選択的にHレベルとすることで、発光指令されている発光サイリスタ210がターンオンする。

(もっと読む)

発光装置および電子機器、発光装置の駆動方法

【課題】多重露光方式を採用した発光装置において発光制御信号の転送レートの増大を防止する。

【解決手段】制御回路20は、書込期間TWにおいては、第1駆動トランジスタTd1のゲートと第2駆動トランジスタTd2のゲートとを非導通状態にしたうえで、データ電位Vd[1]を第1駆動トランジスタTd1のゲートに供給し、その後の転送期間においては、第1駆動トランジスタTd1のゲートと第2駆動トランジスタTd2のゲートとを導通させて、第1保持容量C1に保持されているデータ電位Vd[1]を第2保持容量C2へ転送する。すなわち、制御回路20は、各単位期間(T1〜T3)において、データ線23[1]に対するデータ電位Vd[1]の供給を1回行うだけで、第1の発光素子E11および第2の発光素子E21の各々の発光を制御することができる。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】発光サイリスタを駆動するための駆動回路の発振を防止する。

【解決手段】オン/オフ指令信号DRVON−PがHレベルの場合、PMOS43及びNMOS44からなるCMOSインバータ42の出力側のデータ端子DAがLレベルとなる。この結果、プリントヘッド13側の共通端子INも0Vとなり、各発光サイリスタ210のアノード・カソード間に電源電圧VDDが印加される。この際、発光サイリスタ210−1〜210−nの内、発光指令されている発光サイリスタ210のゲートのみを、シフトレジスタ110によって選択的にHレベルとすることで、発光指令されているサイリスタ210がターンオンする。NMOS44のチャネル形成予定領域に、サブストレート領域と同極性の不純物が注入されているので、NMOS44の閾値電圧が増加し、駆動回路41の発振を防止できる。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】発光サイリスタを駆動するための駆動回路の発振等を防止する。

【解決手段】オン/オフ指令信号DRVON−Nが“L”レベルの場合、CMOSインバータ42の出力側のデータ端子DAが“H”レベルとなる。この結果、プリントヘッド13側の共通端子INも“H”レベルとなり、各発光サイリスタ210のアノード・カソード間に電源電圧VDDが印加される。この際、発光サイリスタ210−1〜210−nの内、発光指令されている発光サイリスタ210のゲートのみを、シフトレジスタ110によって選択的に“L”レベルとすることで、発光指令されているサイリスタ210がターンオンする。PMOS43のソースにVDD電源が接続され、サブストレート端子に、VDD電源よりも高いVDD5電源が接続されているので、PMOS43の閾値電圧が増加し、駆動回路41の発振を防止できる。

(もっと読む)

駆動回路、駆動装置及び画像形成装置

【課題】駆動電流の信号反射による駆動波形の歪みを防止する。

【解決手段】発光素子アレイ200を構成する複数の発光サイリスタ210(=210−1〜210−n)は、VDD端子と共通端子INとの間に並列に接続されている。共通端子INは、接続ケーブル70を介して定電流源回路42に接続されている。更に、発光サイリスタ210のアノード・カソード間には、スイッチ回路230が接続されている。発光サイリスタ210−1〜210−nは、シフトレジスタ110から順次出力されるトリガ信号により、順に点灯する。この際、スイッチ回路230は、オン/オフ指令信号DRVON−Pに基づき、発光サイリスタ210の消灯時には、オン状態になって発光サイリスタ210のアノード・カソード間を短絡し、発光サイリスタ210の点灯時には、オフ状態になる。これにより、接続ケーブル70に流れる駆動電流Ioutが略一定となって、信号反射もなくなる

(もっと読む)

駆動回路、駆動装置及び画像形成装置

【課題】発光サイリスタ等の被駆動素子の破壊を防止して信頼性の向上を図る。

【解決手段】ドライバICは、第1端子と、第2端子と、前記第1端子及び前記第2端子間の導通状態を制御する制御端子と、を有する被駆動素子が複数配列された被駆動素子アレイを時分割駆動する回路である。被駆動素子アレイは、隣接配置された被駆動素子毎に被駆動素子群が形成され、各被駆動素子群における第1端子群、第2端子群、及び制御端子群の内、各第2端子群がグランドにそれぞれ接続され、各制御端子群が共通母線にそれぞれ接続されている。ドライバICは、各共通母線をそれぞれ駆動する複数のゲート駆動用バッファ162を備えている。各バッファ162は、電源VDDと共通母線OUTとの間に直列に接続されたスイッチ用PMOS403及び降圧用PMOS406と、共通母線OUTとグランドGNDとの間に接続されたスイッチ用PMOS404とを有している。

(もっと読む)

光プリントヘッドおよび画像形成装置

【課題】パワーMOSトランジスタの搭載を不要とし、光プリントヘッドの小型化、低コスト化を図る発光素子アレイ、駆動装置、画像形成装置を提供する。

【解決手段】本発明の光プリントヘッドは、第1端子と、第2端子と、前記第1端子と前記第2端子との間の導通を制御するための制御端子とを各々有し、前記第1端子と前記第2端子との間に電流が流れることにより発光する複数の発光素子と、前記複数の発光素子の各々に対応して設けられ、前記発光素子の前記第1端子と前記第2端子との間に電流を流すことにより発光させる駆動回路と、前記複数の発光素子の各々に対応して設けられ、前記発光素子の前記制御端子と一端が接続され、双方向に電圧降下を発生させる双方向電圧降下発生回路と、複数の前記双方向電圧降下発生回路の他端を共通に接続する共通母線と、前記共通母線に対して、前記発光素子の制御端子に与える制御信号を出力するバッファ回路とを備えたことを特徴とするものである。

(もっと読む)

露光装置及び露光装置の光量補正方法並びに画像形成装置

【課題】有機EL素子の経時劣化の進行を抑制しながら、輝度ムラの発生を低減する。

【解決手段】各点灯回路51(i)(i=1〜m)は複数の画素からなり、各画素は、複数の有機EL素子を備える。露光装置は、例えば、電源投入後や、印刷前後の印字をしていない状態で、定期的に各有機EL素子を一定の値の駆動信号で発光させて、光センサ回路52(i)(i=1〜m)により、有機EL素子の発光光量を計測する。センサドライバ45は、計測した発光光量に対応するセンサ出力信号をヘッドコントローラに出力する。ヘッドコントローラは、計測された発光光量と設定された基準光量との差分に基づいて、画像データに応じた階調信号を補正し、設定された目標基準光量と設定された基準光量との差分に基づいて各有機EL素子を発光させるためのアノード時間を補正する。

(もっと読む)

電気光学装置、電子機器及び電気光学装置の製造方法

【課題】従来の電気光学装置では、電気光学素子の特性を電気光学素子間でそろえることが困難である。

【解決手段】基板と、前記基板の第1面一部の領域を複数の素子領域91に区画する隔壁と、複数の発光素子67と、を含み、発光素子67は、発光機能を発揮する機能層を有し、発光機能は、前記基板のY方向における分解能が、複数の発光素子67のY方向における間隔Pに対応しており、複数の発光素子67は、F方向に連続して一列に並ぶ複数の発光素子67を1組の素子群241とする複数組の素子群241に区分されており、素子領域91は、少なくとも1組の素子群241を包含しており、素子領域91の長手方向は、F方向に延在しており、F方向は、X方向から傾いており、複数組の素子群241は、F方向と交差し、且つY方向から傾いている方向に並んでいる、ことを特徴とする電気光学装置。

(もっと読む)

電気光学装置、電子機器及び電気光学装置の製造方法

【課題】従来の電気光学装置では、電気光学素子の特性を電気光学素子間でそろえることが困難である。

【解決手段】基板と、前記基板の第1面の一部の領域を複数の素子領域91に区画する隔壁と、複数の発光素子67と、を含み、発光素子67は、発光機能を発揮する機能層を有し、発光機能は、前記基板のY方向における分解能が、複数の発光素子67のY方向における間隔Pに対応しており、複数の発光素子67は、F方向に連続して一列に並ぶ複数の発光素子67を1組の素子群とする複数組の前記素子群に区分されており、素子領域91は、少なくとも1組の前記素子群を包含しており、素子領域91の長手方向は、F方向に延在している、ことを特徴とする電気光学装置。

(もっと読む)

ドライバ回路

【課題】インクジェットプリンター等のドライバ回路において、出力回路の貫通電流を抑制して、低消費電力化を図る。

【解決手段】セパレーション回路SPは、印字データData2をPMOSトランジスタMP側とNMOSトランジスタMN側にそれぞれ分離して印加する回路であり、印字データData2に基づいて、PMOSトランジスタMP側にゲート信号PC、NMOSトランジスタMN側にゲート信号NCを出力する。そして、セパレーション回路SPは、PMOSトランジスタMPとNMOSトランジスタMNが同時にオンしないように、ゲート信号PC、NCの電圧変化が生じるタイミングをずらすように構成されている。ゲート信号PC、NCの変化のずれ量は、制御データ保持回路3に保持された2ビットの制御データ(S1,S2)に応じて調節可能に構成されている。

(もっと読む)

ドライバ回路

【課題】ドライバ回路のドライブ能力をプリンター装置の特性に合わせて適切に設定する。

【解決手段】ドライバ回路は、シフトレジスタ1、印字データ保持回路2、制御データ保持回路3、出力回路4から形成されている。印字データ保持回路2で保持された印字データData2、制御データ保持回路3に保持された制御データData1は、それぞれ出力回路4に印加される。そして、出力回路4は、制御データ保持回路3に保持された印字データData2に応じた出力電圧を出力する。この時、出力回路4のドライブ能力(出力電圧の立ち上がり時間/立ち下がり時間)は、制御データ保持回路3に保持された制御データData1に応じて可変制御されるように構成されている。

(もっと読む)

駆動回路、光プリントヘッド及び画像形成装置

【課題】複数のLED駆動回路間での駆動電流のばらつきを改善し、印刷濃度のむらを解消して印刷品位の向上を図る。

【解決手段】LEDプリントヘッドに搭載されるドライバIC中の複数のLED駆動回路110において、駆動トランジスタであるPMOS118〜122のゲート118G〜121G,122−1G〜122−4GをLEDアレイ方向(X軸方向)に並列に配置して、PMOSのチャネルがLEDアレイ方向に対して直交する方向(Y軸方向)となるように配置し、ドレイン電流をY軸方向に流す構成にしている。そのため、低温雰囲気中であってもドライバIC端部とドライバIC中心部との駆動電流の差が小さくなり、ドライバIC内での駆動電流のばらつきを改善できる。これにより、画像形成装置における印刷濃度のむらを解消できて印刷品位を向上できる。

(もっと読む)

発光素子アレイ、駆動装置および画像形成装置

【課題】パワーMOSトランジスタの搭載を不要とし、光プリントヘッドの小型化、低コスト化を図る発光素子アレイ、駆動装置、画像形成装置を提供する。

【解決手段】本発明の発光素子アレイは、複数配列された発光素子を駆動回路により発光させる発光素子アレイにおいて、前記発光素子は、第1端子が前記駆動回路に接続され、第2端子がグランドに接続され、第3端子が共通母線に接続される三端子スイッチ素子であり、前記第3端子が接続される前記共通母線はプッシュプル駆動バッファ回路により駆動されることを特徴とするものである。

(もっと読む)

半導体集積回路及び電子回路装置

【課題】半導体集積回路に応力が加わった場合において、その応力による半導体集積回路内のMOSトランジスタの電気的特性の変動を抑える。

【解決手段】出力MOSトランジスタ1Tのゲート電極13Aは、半導体基板10の長辺方向D1(即ち長辺に平行な方向)に沿って延びている。このゲート電極13Aの両側には、ソース領域、ドレイン領域(共に不図示)が配置され、それらの間にチャネル領域(不図示)が形成されている。また、各制御回路1Lに含まれる各制御MOSトランジスタ(不図示)についても、ゲート電極13Bを半導体基板10の長辺方向D1に沿って延びるように構成してもよい。

(もっと読む)

発光装置、光プリントヘッドおよび画像形成装置

【課題】発光サイリスタのゲート端子電位を過剰に低下させることなく、無効なゲート電流を削減して発光出力の増加を図る。

【解決手段】発光サイリスタd1を駆動するバッファ回路101に、PMOSトランジスタ112、113を設ける。サイリスタd1を発光させる場合、PMOSトランジスタ112はオフ、PMOSトランジスタ113はオンとなって、発光サイリスタd1のゲート端子Gの電位はPMOSトランジスタの閾値電圧Vtに略等しい電位になる。これにより、オン状態にあるサイリスタd1のアノード端子から供給される駆動電流は、NPNトランジスタ62のコレクタやPNPトランジスタ61のコレクタ側に流れる電流Ik2、Ik1となって、ゲート端子からバッファ回路101を介してグランドへ至る電流Igは生じない。

(もっと読む)

1 - 20 / 44

[ Back to top ]