Fターム[2G132AB06]の内容

電子回路の試験 (32,879) | 試験内容 (2,602) | 限界試験、寿命試験、信頼性試験 (453) | 動作マージン (263) | 電圧マージン (58)

Fターム[2G132AB06]に分類される特許

1 - 20 / 58

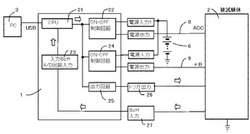

電源瞬断試験装置

【課題】電源電圧の瞬断、瞬オンに対する自動車用電子機器の動作限界を定量的に調査する手段を提供する。

【解決手段】被試験機に印加する通常の電源電圧である+Bおよび被試験機のメモリーホールドなどのための常時印加の電圧であるAccの瞬断について、様々なパターンを再現するために当該時間、電圧についてもプログラムを用いて少しつづ徐々に変化させて被試験機に印加し、これに基づく被試験機の応答を監視して別に定めた短い時間ごとに出力論理の正否を確認することにより、自動車用に最近多く用いられるデジタル機器独特のプログラムによる思いも寄らない誤動作の発生を確認でき、さらに誤動作発生時の誤動作モードをきちんと捕らえて適切な設計対応を取ることができる。

(もっと読む)

半導体集積回路のテストボード

【課題】半導体集積回路のテスト時に発生する電源ノイズは、多種多様である。そのため、テスト時に生じる多様な電源ノイズを低減させる半導体集積回路のテストボードが、望まれる。

【解決手段】半導体集積回路のテストボードは、被検査デバイスに供給する電流値を被検査デバイスに供給されるクロックに同期させて変化させる電源電流制御回路を備えている。電源電流制御回路は、被検査デバイスに供給されるクロックに同期させて、被検査デバイスに供給される電流値を変化させる。

(もっと読む)

半導体装置

【課題】テスト時間の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】このチャージポンプ回路12では、通常動作時は、ポンプキャパシタC0,C2の一方電極にポンプクロック信号φPを与えるとともにポンプキャパシタC1,C3の一方電極にポンプクロック信号φPの相補信号を与え、ポンプキャパシタC0〜C3の欠陥を検出するテストモード時は、ポンプキャパシタC0〜C3の各々の電極間に外部電源電圧VCCを静的に印加する。したがって、MOSトランジスタのオン耐圧を超える高電圧をポンプキャパシタC0〜C3に印加できるので、テスト時間を短縮化できる。

(もっと読む)

半導体集積回路

【課題】テスト時の消費電力を低減することができる半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路100は、フリップフロップFF、制御回路10及び排他的論理和ブロックを有する。フリップフロップFFは、テスト入力Tにテストデータ信号TINが入力する。排他的論理和ブロック20は、一方の入力がフリップフロップFFのテスト入力Tと接続され、他方の入力がフリップフロップFFの出力Qと接続される。制御回路10は、排他的論理和ブロック20の出力XORとクロック信号CLKとが入力し、排他的論理和ブロックの出力XORの値に応じてフリップフロップFFへのクロック信号CLKの出力を制御する。

(もっと読む)

半導体集積回路テスト方法

【課題】複数のメモリを備えた半導体集積回路において、IRドロップによる誤動作を回避しつつ、効率の良いメモリテストを実現すること。

【解決手段】半導体集積回路に含まれる複数のメモリのそれぞれを単体でテストした場合に消費される電流を参照し、該複数のメモリから同時にテストすべき複数のメモリを被テストメモリとして選択する工程と、前記複数の被テストメモリを同時にテストした場合に消費される総消費電流をシミュレーションにより生成する工程と、前記総消費電流および前記半導体集積回路のレイアウト情報に基づいて、前記半導体集積回路におけるIRドロップを算出する工程と、算出した電圧降下が所定の許容値以内であるか否かを判定する工程と、前記電圧降下が前記所定の許容値を超えた場合には、前記複数のメモリから同時にテストすべきメモリを再度選択し直す工程と、を含む。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

半導体集積回路およびその設計方法

【課題】IRドロップ問題を緩和することのできる半導体集積回路およびその設計方法を提供する。

【解決手段】本発明の一実施形態による半導体集積回路は、データをシリアルに転送するシリアル動作を行う直列接続された複数のフリップフロップを分割して構成された複数のF/Fグループと、前記F/Fグループに含まれるフリップフロップの出力が一致する場合に第1の信号を出力し、そうでない場合に第2の信号を出力する連続信号判定回路とを備えるとともに、前記F/Fグループの先頭以外のフリップフロップに対し、前記第1の信号を受信する場合にはクロック信号を供給せず、前記第2の信号を受信する場合にはクロック信号を供給するクロックゲーティング回路を備える。

(もっと読む)

電子装置

【課題】電力損失を最小限にすることが可能な複数の電源を含む電子装置を提供する。

【解決手段】パワーアンプ40は、入力電圧Viに基づいた出力電圧の電力を被試験体DUTに供給する。検出回路43は、パワーアンプ40の動作電源であるスイッチング電源22から、パワーアンプ40に電流が流れたことを検出する。選択回路51は、電流が流れない場合には、スイッチング電源22の電圧値を所定値に設定し、電流が流れた場合には、スイッチング電源22の電圧値を入力電圧Viより予め定められた値αだけ大きい値に設定する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】従来の半導体装置では、電源電圧変動を抑制するために回路規模が大きくなる問題があった。

【解決手段】本発明の半導体装置は、テスト対象回路11〜13と、スキャンモード制御信号SMCと、ノイズ制御信号CNTと、クロック信号CLKと、テストパターンSINとが入力され、テスト対象回路12に対するテストを行うテスト回路20と、を有し、テスト回路20は、ノイズ制御信号CNTがイネーブルであるダミーノイズ生成期間にテスト回路20において保持されているテストパターンSINに基づくテスト値を維持し、ダミーノイズ生成期間にクロック信号CLKの周期に応じて変動するダミー電源ノイズを生成し、ダミーノイズ生成期間の終了後にテストパターンによりテスト対象回路12をテストする。

(もっと読む)

半導体装置

【課題】テストパターンの内容、あるいは回路規模によらず、動作試験が短時間且つ高効率で行える半導体装置の実現。

【解決手段】フリップフロップ回路37と、試験モード時に、フリップフロップ回路に所定の値を設定すると共にフリップフロップ回路の保持する値を読み出すスキャンチェーンと、通常モード時に非動作で、試験モード時には、フリップフロップ回路の値が変化する場合に動作状態となり、前記フリップフロップ回路の値が変化するタイミングで非動作状態になる電流消費回路37A,37Bと、を有する半導体装置。

(もっと読む)

半導体集積回路および電源供給方法

【課題】チップ内でデバイス特性にバラツキがあっても、消費電力を低減させることのできる半導体集積回路および電源供給方法を提供する。

【解決手段】実施形態の半導体集積回路1は、それぞれの領域に半導体デバイスが配置された領域1および領域2を有し、電源供給手段である電源端子T1、T2が、領域1、領域2それぞれに個別に電源を供給する。領域1にはデバイス特性測定回路ROSC1が配置され、領域2にはデバイス特性測定回路ROSC2が配置されている。

(もっと読む)

半導体集積回路及び電源電圧適応制御システム

【課題】フリップフロップを備える半導体集積回路において、エラーフリップフロップを効率的に検出する。

【解決手段】半導体集積回路は、冗長フリップフロップを含む複数のフリップフロップと、セレクタ部と、エラー検出部とを備える。セレクタ部は、再構成情報に応じて選択フリップフロップを選択し、入力端子に入力されたデータが選択フリップフロップのそれぞれによって出力端子に出力されるようにデータの流れを切り替える。テストモード時、フリップフロップはスキャンチェーンを構成し、そのスキャンチェーンにはスキャンデータが入力される。そして、エラー検出部は、それぞれのフリップフロップの入出力に基づいてエラーフリップフロップを検出し、当該エラーフリップフロップが選択フリップフロップから除外されるように再構成情報を作成する。

(もっと読む)

試験装置

【課題】被試験デバイスへ過剰な電流が流入することを防ぐ。

【解決手段】被試験デバイスを試験する試験装置であって、前記被試験デバイスに供給する電源電圧を発生する電源部と、前記電源部から前記被試験デバイスに至る経路上に設けられた誘導負荷部と、前記誘導負荷部に対して前記被試験デバイスと並列に接続された第1半導体スイッチと、前記被試験デバイスに対する電源電圧の供給を遮断する場合に、前記第1半導体スイッチをオンとする制御部とを備える試験装置を提供する。

(もっと読む)

半導体装置

【課題】テスト信号毎の専用配線を不要とし、配線領域を削減できるテスト回路を備えた半導体装置を提供する。

【解決手段】外部から供給されるテスト情報をデコーディングし、複数の信号を生成するDFTデコーダ202と、互いに従属接続した複数のDFTレジスタDFTr0〜DFTrnと、複数のDFTレジスタにそれぞれ対応する複数の制御回路(制御回路CKT0〜CKTn)と、複数のレジスタのうちの第1のレジスタ(DFTレジスタDFTr0)に複数の信号(シフトデータTSCANDATA)を供給するセレクタ(セレクタ113)と、セレクタのセレクティング回数を規定するカウンタ(9bitカウンタ112)と、複数の制御回路の数に対応するクロック周期の回数を、複数のレジスタ及びカウンタに供給するシフトクロック生成回路(シフトCK制御回路111)と、を備える。

(もっと読む)

試験装置

【課題】電源電圧の変動を抑制する。

【解決手段】電源補償回路20は、スイッチ素子SW1、SW2のオン、オフに応じて補償パルス電流ISRC、ISINKを生成する。パターン発生器PGは、ドライバDR1〜DR4が出力すべき試験信号STESTを記述するテストパターンSPTN1〜SPTN4と、ドライバDR5、DR6が出力すべき制御信号SCNTb、SCNTaを記述する制御パターンSPTN_CMPb、SPTN_CMPaを生成する。電流調節部30は、温度に応じて補償パルス電流ISRC、ISINKを調節する。

(もっと読む)

試験装置

【課題】安定した電源電圧を供給する。

【解決手段】メイン電源10は、DUT1の電源端子P1に電力を供給する。電源補償回路20は、メイン電源10からDUT1に流れる電源電流IDDから、補償電流ICMP’をDUT1とは別経路に引きこむ。補償電流ICMP’は、それとDUT1の電源端子P1に流れ込む動作電流IOPとの和が実質的に一定となるように生成される。電源補償回路20は、試験状態においてDUT1と熱的に結合されるように配置される。

(もっと読む)

半導体装置

【課題】テスト信号を誤動作なく発生するテスト回路を備えた半導体装置を提供する。

【解決手段】動作指定コマンドがテスト動作モードの設定を示すときに、コマンド信号CMD1及びコマンド信号CMD2に応じて、第1のテスト信号(テスト信号DFT1〜DFTn)のうち所定の信号を活性化するコマンドデコーダ106と、動作指定コマンドがテスト動作モードの設定を示すときに第1のテスト信号を受け取り、第2のテスト信号(制御用テスト信号DFTF1〜DFTFn)として並列に出力し、テスト動作モードの設定以外の動作を指定するときに、スキャンチェーン接続され、第1のテスト信号を第3のテスト信号としてスキャン出力端子TSOUTへ直列に出力するレジスタ部107と、テスト動作モードの設定を示すときに、第2のテスト信号に応じてメモリセルアレイの動作を制御する読み出し及び書き込み制御部104と、を備える。

(もっと読む)

電源装置および試験装置

【課題】簡便な構成により電源電圧を一定に保つことが可能な試験装置を提供する。

【解決手段】半導体デバイスに電源電圧を供給する電源装置が提供される。メイン電源10は、半導体デバイスの電源端子P1に電力を供給する。電源補償回路12のソーススイッチ12bは、電源端子P1と接地端子の間に設けられる。電源補償回路12は、ソーススイッチ12bをノーマリオンとして電流IDCを発生させ、スイッチングによってソーススイッチ12bをオフしたときの電流の変化量を、ソース補償電流ISRCとして半導体デバイスの電源端子P1に注入する。

(もっと読む)

試験装置

【課題】プローブ検査においても、理想の電源環境を提供する。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

(もっと読む)

1 - 20 / 58

[ Back to top ]