Fターム[2G132AB07]の内容

電子回路の試験 (32,879) | 試験内容 (2,602) | 限界試験、寿命試験、信頼性試験 (453) | 動作マージン (263) | タイミングマージン (118)

Fターム[2G132AB07]に分類される特許

1 - 20 / 118

半導体集積回路

半導体集積回路,および,半導体集積回路の試験方法

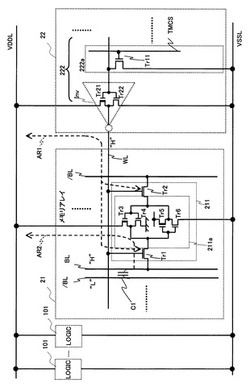

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

半導体集積回路検査装置,および,半導体集積回路の検査方法

【課題】テスト時間をより短縮するテストパターンを作成する半導体集積回路検査装置,および,半導体集積回路の検査方法を提供する。

【解決手段】半導体集積回路検査装置20は,テストパターンを複数の区間に分割した分割テストパターン毎に,分割テストパターンに対する論理演算を異なる周期のクロック信号に基づき半導体集積回路に実行させることにより得られた半導体集積回路31の故障判定結果に基づき,分割テストパターン毎の最適クロック周期を算出する最適周期算出部213と,テストパターンと,テストパターンに係る分割テストパターン毎の最適クロック周期を有するテストパターンファイルを生成する新テストパターンファイル生成部214を有する。

(もっと読む)

遅延スキャンテスト方法、半導体装置及び半導体装置の設計方法

【課題】従来のスキャンテスト方法では、電源電圧変動を抑制しながら動作クロックの周波数の高い半導体装置をテストできない問題があった。

【解決手段】本発明のスキャンテスト方法は、クロック信号SCLKをスキャンフリップフロップ21〜2nに入力して第1のテストパターンをスキャンフリップフロップ21〜2nに設定し、クロック信号SCLKよりも周波数の高いクロック信号RCLKをスキャンフリップフロップ21〜2nに入力すると共に、スキャンフリップフロップ21〜2nをクロック信号RCLKによらず保持する値を維持するホールドモードに制御し、ホールドモードを解除すると共にスキャンフリップフロップ21〜2nをテスト対象回路の出力に応じて保持する値を更新するテスト結果取得モードに制御し、テスト結果取得モードにおいてクロック信号RCLKを2パルス用いてスキャンフリップフロップ21〜2nに保持されている値を更新する。

(もっと読む)

半導体装置の検査方法、検査プログラム及び半導体装置の検査装置

【課題】短時間で半導体装置の検査を行うことができる半導体装置の検査方法、検査プログラム及び半導体装置の検査装置を提供すること。

【解決手段】本発明は、記憶部2から半導体装置SD1の特性データDAT1を読み込む。次いで、ストローブ演算式212にNMOSトランジスタの閾値Vt1を代入することにより、半導体装置SD1に対するストローブ値STB1する。次いで、半導体装置SD1にテスト入力信号Dinを出力する。そして、ストローブ値STB1で指定されるタイミングで、半導体装置SD1から出力されるテスト出力信号Doutのパターンが期待値パターンEPと一致するかを判定する。

(もっと読む)

半導体集積回路のテスト方法とシステムとプログラム

【課題】ロット全体のテスト時間の短縮を図り、良品を不良と誤判定することを回避する方法、システム、プログラムの提供。

【解決手段】同一構成のLSI(被試験デバイス)のロットをテストするにあたり、一のLSIのファンクションテストを実行テストレート1で行い、前記ファンクションテストの結果がパスの場合、次のLSIのファンクションテストを実行テストレート1で行い、フェイルの場合、実行テストレート2で再び前記一のLSIの再テストを行い、再テストがパスした場合、実行テストレート1を現在値に加算テストレートを加算した値に更新して次のLSIのファンクションテストを前記更新した実行テストレート1で行い、前記一のLSIの実行テストレート1、2によるファンクションテストがいずれもフェイルの場合、前記一のLSIを不良と判定する。

(もっと読む)

試験装置

【課題】高速多値信号を試験可能な試験装置を提供する。

【解決手段】パターン発生器PGは、I/O端子PIOに入力される被試験信号S1と比較すべきしきい値電圧Vthを指定する制御データS11を発生するとともに、被試験信号S1としきい値電圧Vthの比較結果の期待値を示す期待値データEXP2を発生する。しきい値電圧発生器10は、制御データS11に応じた電圧レベルを有するしきい値電圧Vthを、第1タイミング信号St1が指定する設定タイミングtVごとに生成する。レベルコンパレータCpは、被試験信号S1の電圧レベルをそれと対応するしきい値電圧Vthと比較する。タイミングコンパレータTCは、レベルコンパレータCpの出力S3を、第2タイミング信号St2が指定するストローブタイミングでラッチし、比較信号S4を生成する。タイミング調節部50は第1タイミング信号St1の位相を調節する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】精度の高いディレイテストを行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路1は、クロック信号CLKに同期して動作する複数のレジスタを有する内部回路11と、クロック信号CLKに同期して動作し第1ノードから第2ノードまでの信号伝搬時間を測定する遅延測定回路12と、遅延測定モードの場合に、遅延測定回路12に対してのみクロック信号CLKを供給し、電圧検出モードの場合に、内部回路11及び遅延測定回路12に対してクロック信号CLKを供給するクロック供給回路13と、を備える。

(もっと読む)

解析プログラム,解析装置および解析方法

【課題】スピードパス解析の解析精度を向上させる技術を提供する。

【解決手段】第1の解析部15は,パス遅延情報記憶部120から,テスト対象回路に対するディレイテストの結果から得られるパス遅延の実測値を取得する。第1の解析部15は,予測値記憶部130から,テスト対象回路に対するタイミング解析により得られるパス遅延の予測値を取得する。第1の解析部15は,特徴値記憶部140から,遅延に影響する要因ごとの特徴値を取得する。第1の解析部15は,取得したパス遅延の実測値と,パス遅延の予測値と,要因ごとの特徴値とを用いて,要因ごとの特徴値からパス遅延の実測値と予測値とのずれを算出するずれ算出モデルを求める。このとき,第1の解析部15は,パス遅延の実測値が得られない活性化パスについて,パス遅延の実測値の代わりにディレイテストで測定した最大周波数に対応する遅延の値を用いて,解析を行う。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

テスト装置、テスト方法、プログラム及び記録媒体

【課題】 テストパワー考慮型のテスト生成において、テストパターン安全性を保証することを達成するテスト装置等を提供する。

【解決手段】 論理回路の故障の有無を判定するテスト装置であって、初期テストキューブが与えられ、初期未定値ビットに論理値を割り当てて中間テストパターンを生成する手段と、テストパターンが印加された論理回路に故障がなければ危険ビットが存在しないというテストパターン安全性を判定する手段と、テストパターン安全性を保証することに寄与しうる候補ビットを特定する手段と、初期未定値ビットにも候補ビットにも対応した中間テストパターンの入力ビットを新規未定値ビットとして新規テストキューブを生成する手段と、新規未定値ビットに論理値を割り当てて最終テストパターンを生成する手段と、最終テストパターン安全性を判定する手段と、論理回路テストにおいて危険ビットを使用させないマスク手段とを備える。

(もっと読む)

スキャンフリップフロップ回路、スキャンテスト回路及びその制御方法

【課題】ホールドフリーの小規模なテスト回路であり、且つ実動作周波数でのテスト可能なスキャンフリップフロップを提供する。

【解決手段】PosタイプF/F100は、クロックの立ち上りエッジ同期し、データ又はスキャンテストデータが選択的に入力されるマスタラッチ(Lowレベルラッチ)110と、マスタラッチ110からのデータが入力されるスレーブラッチ(Hiレベルラッチ)111とを有する。そして、スキャンシフト時には、マスタラッチ110は、スキャンシフトデータ入力SINをスキャンシフトクロックSCLK1のLow期間で取り込むと共にスレーブラッチ111へ出力する。スレーブラッチ111はSCLK1とはエッジ位置が異なるスキャンシフトクロックSCLK2のHi期間でマスターラッチ110の出力を取り込むと共にQに出力する。

(もっと読む)

半導体装置及び半導体装置の制御方法

【課題】tRP期間の性能限界試験を実行可能な半導体装置及びその制御方法を提供する。

【解決手段】コマンドデコーダ16は、デバイスのアクティブ動作を認識し保持する第1の取り込み部、第1の取り込み部が出力する第1の出力信号を後段の回路(制御回路18)に出力する第1の出力部、デバイスのインアクティブ動作を認識し保持する第2の取り込み部、第2の取り込み部が出力する第2の出力信号を後段の回路に出力する第2の出力部を含む。第1及び第2の取り込み部は、同期信号(クロック信号CLK)の第1の遷移エッジに対応してCommandを取り込み且つ保持し第1の出力部は、第1の遷移エッジに対応して第1の出力信号(inACT)を出力する。第2の出力部は、テストモード信号が第2の論理であるテストモード動作時に、第1の遷移エッジと逆の遷移エッジである同期信号の第2の遷移エッジに対応して第2の出力信号(inPRE)を出力する。

(もっと読む)

故障解析プログラム,故障解析装置および故障解析方法

【課題】適切な故障候補の組合せを選択できるようにして、故障要因を高い精度で推定する。

【解決手段】生成部11で生成された故障候補組合せのうち、コスト算出部13で得られるコストを最小にする故障候補組合せが選択され、その故障候補組合せに応じた関数(一以上の故障要因と各故障要素の誤差または故障率との相関関係を与える関数)が出力され、この関数に基づき、故障の要因が推定される。

(もっと読む)

信号発生装置および試験装置

【課題】エッジの位相を固定して、信号のデューティ比を変更する。

【解決手段】指定されたデューティ比の出力信号を出力する信号発生装置であって、入力信号と出力信号との位相差を検出する位相検出器と、位相検出器により検出された位相差をフィルタリングして、発振器に供給するループフィルタと、位相差に応じた周波数の発振信号を出力する発振器と、指定値に応じて発振信号のデューティ比を変更して出力信号として出力するとともに位相検出器に供給するデューティ変更部と、を備える信号発生装置を提供する。

(もっと読む)

半導体集積回路および電源供給方法

【課題】チップ内でデバイス特性にバラツキがあっても、消費電力を低減させることのできる半導体集積回路および電源供給方法を提供する。

【解決手段】実施形態の半導体集積回路1は、それぞれの領域に半導体デバイスが配置された領域1および領域2を有し、電源供給手段である電源端子T1、T2が、領域1、領域2それぞれに個別に電源を供給する。領域1にはデバイス特性測定回路ROSC1が配置され、領域2にはデバイス特性測定回路ROSC2が配置されている。

(もっと読む)

半導体試験装置

【課題】半導体試験装置のシステム周波数よりも高い周波数の論理信号を低コストで生成出力することができ、リアルタイムにエッジや周波数を変更でき、高精度のタイミング精度が得られる半導体試験装置を提供すること。

【解決手段】半導体試験装置に内蔵されている信号発生部から出力される複数系統の論理信号を加算する加算器とこの加算器の出力をリタイミングクロックにしたがって取り込むラッチとこのラッチ出力を選択的に出力するスイッチとで構成された複数のパターン信号発生ユニットと、これら複数のパターン信号発生ユニットからスイッチを介して出力される出力信号間のスキューを補正する校正経路が設けられた半導体試験装置において、

前記リタイミングクロックは少なくとも2系統の論理信号を加算することにより生成され、前記校正経路は、前記各パターン信号発生ユニットのスイッチに連動して駆動され択一的に所定の出力信号を選択するロジックゲートを含むことを特徴とするもの。

(もっと読む)

1 - 20 / 118

[ Back to top ]