Fターム[2G132AC15]の内容

電子回路の試験 (32,879) | 試験方法 (2,026) | スキャンイン、アウト、パス、LSSD (632) | バウンダリスキャン(境界走査試験) (123)

Fターム[2G132AC15]の下位に属するFターム

内部スキャンとの併用 (5)

Fターム[2G132AC15]に分類される特許

1 - 20 / 118

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

集積回路及び不揮発性記憶装置書き換え方法

【課題】不揮発性記憶装置内の制御プログラムの書き換え時間を短縮すること。

【解決手段】バウンダリスキャン回路は、不揮発性記憶装置に接続された第1バウンダリスキャンレジスタ装置、及び、不揮発性記憶装置に接続されない第2バウンダリスキャンレジスタ装置を含む回路であって、第1バウンダリスキャンレジスタ装置及び第2バウンダリスキャンレジスタ装置の双方を経由する第1経路と、第1バウンダリスキャンレジスタ装置を経由し第2バウンダリスキャンレジスタ装置を経由しない第2経路とが切り替え可能に接続される。制御信号回路は、TAPコントローラからバウンダリスキャンレジスタ装置に入力される制御信号の入力経路が、第1経路又は第2経路の切り替えに応じて切り替え可能に接続される。

(もっと読む)

最適化されたJTAGインターフェイス

【課題】

集積回路内のJTAGタップドメインにアクセスするのに最適化されたJTAGインターフェイスが使用される。限定はしないが、シリアル通信関連集積回路テスト、エミュレーション、デバッグ、および/またはトレース操作等の多様なシリアル通信操作に対してインターフェイスを使用することができる。

【解決手段】

TDI入力端子、TCK入力端子、TMS入力端子、およびTDO出力端子を有し、TDO出力端子は集積回路の外部アクセス可能なデータ入出力ピンに接続されているIEEE 1149.1タップドメインと、集積回路の外部アクセス可能なデータ入出力ピンに接続されたシリアル入力端子、TDI入力端子に接続された第1のパラレル出力端子、およびTMS入力端子に接続された第2のパラレル出力端子を有するシリアル入力パラレル出力回路とを含む、集積回路。

(もっと読む)

半導体集積回路及びその設計方法

【課題】半導体集積回路の外部端子としてTRSTがなくても、論理シミュレーションの際に、タップコントローラのステートを確定する。

【解決手段】タップコントローラ2は、リセット端子(端子p4)を有し、回路部3は、タップコントローラ2における状態遷移を制御するステート制御信号と、クロック信号を入力し、ステート制御信号とクロック信号に応じて、リセット端子p4にリセット信号を供給することで、タップコントローラ2のステートを確定する。

(もっと読む)

エミュレータ及びデバッグ方法

【課題】JTAG-ICEにおいて、LSIの入出力状態をトリガとするエミュレーションのブレークを実現する「エミュレータ及びデバッグ方法」を提供する。

【解決手段】エミュレーション処理部23は、LSI31のICE制御ブロック314に命令を発行し、所定のプログラムをコアロジック311に実行させ、スキャン処理部24は、LSI31のコアロジック311のプログラムの1ステップ実行毎のスキャン動作を、LSI31のバウンダリスキャン制御ブロック315に行わせ、LSI31の各入出力端子312の状態をスキャンデータメモリ25に格納する。エミュレーション処理部23は、スキャンデータメモリ25からLSI31の各入出力端子312の状態を読み出し、読み出した各入出力端子312の状態が、予めブレーク条件メモリ26に設定されているブレーク条件にマッチするかどうかを調べ、マッチしていればプログラムの実行をブレークする。

(もっと読む)

プリント回路基板上に取り付けられた電子回路装置の電気接続を自動的に測定する方法及び装置

【課題】プリント回路基板(PCB)上に取り付けられた電子回路装置の構成要素及び装置の回路端子又はピン間の電気接続を測定するための単純なツールが必要。

【解決手段】電子処理ユニットは、各バウンダリスキャン対応装置32,33,34,35のバウンダリスキャン特性と、ドライバ及び/又はセンサとして動作可能なバウンダリスキャン・セルを含むリストを取得する。このリストに基づいて、回路端子に接続されたバウンダリスキャン・セルがドライバ、センサとし作動し、バウンダリスキャン・レジスタにラッチする。ドライバ・データとセンサ・データを含むバウンダリスキャン・レジスタからのデータが、記憶装置45に記憶される。記憶されたデータは、プリント回路基板31における回路端子37,38間と40,41間の電気接続を判定するために分析され、分析の結果が提示される。

(もっと読む)

試験アクセス・ポート・スイッチ

【課題】選択されていないTAPの電源がオンまたはオフされているかに関わらず、選択されたTAPへ情報を転送することができる電子システムを提供する。

【解決手段】電子システム10は、それぞれTAPスイッチ12に接続されたTAP20,22,24を有している。TAPスイッチ12は、例えば、命令に追加または事前追加されたコードのように、シリアル命令に含まれる選択コードに応答して、TAPのうちの選択された1つへクロック信号を提供するように構成された第1の回路40を備える。このTAPスイッチは更に、TAPスイッチによって受け取られたシリアル命令を、選択されたTAPへ渡すように構成された命令レジスタ(IR)を備える第2の回路38と、選択コードに応答して、選択されたTAPから受け取ったシリアル命令を、TAPスイッチの出力へと転送するように構成された第3の回路42とを備える。

(もっと読む)

テスト回路およびテスト回路の制御方法

【課題】テスト専用端子の増加を防ぎ、テストの長時間化を防止する。

【解決手段】テストアクセスポートに入力されるテスト信号に応じて、回路ブロックの試験を行うテスト回路であって、第1のTAP制御部及びその制御下にある第2のTAP制御部と、第1のTAP制御部のテスト動作の無効と、記憶情報の書き換えを不可に制御する第1の情報を記憶する第1のレジスタと、第1の情報に応じて記憶情報の書き換えを不可に制御され、第2のTAP制御部のテスト動作の有効・無効の制御する第2の情報を記憶する第2のレジスタと、外部から入力されるTDI信号に応じて前記第1、2のレジスタが書き換え不可状態を解除する制御回路と、を有するテスト回路。

(もっと読む)

半導体装置

【課題】内部回路に電源電位または接地電位を供給するための外部端子に関して、開放および短絡を検出可能にした半導体装置を提供する。

【解決手段】内部回路と、通常動作時に外部から印加される電源電位または接地電位を内部回路に供給するための第1の端子と、テスト結果を出力するための第2の端子と、第1の端子とは異なる端子から供給される電位により生成された所定の基準電圧と第1の端子の電位とを比較する比較部と、比較部からの出力をテスト結果として保持する第1のレジスタと、テスト結果を第1のレジスタから第2の端子に出力するテスト結果出力部とを有する構成である。

(もっと読む)

システムインパッケージ

【課題】サイズやコストを増大させることなく、テスト容易なシステムインパッケージを実現する。

【解決手段】テスト容易化回路内装SIP1bは、少なくともその1つに集積回路チップ2が搭載された複数のコア基板3,4b,5を、絶縁樹脂層7を介して貼り合わせて構成するとともに、コア基板3,5に形成された配線層31,51を、スルーホール6を介して接続して構成される。このうち、コア基板4bには、半導体層が形成されており、コア基板4bには、その半導体層を用いたトランジスタ素子が形成され、さらに、そのトランジスタ素子がコア基板4bに含まれる配線層の配線で接続されることによって、集積回路チップ2のテストを容易化するためのテスト容易化回路が形成されている。

(もっと読む)

プリント基板テスト装置

【課題】疑似接触状態のような導通のある不良や異物等による浮遊容量や誘導結合による不良の検出など、健全性の判定を容易に行えるプリント基板テスト装置を得る。

【解決手段】バウンダリスキャン対応の第1のデバイス12から不良モードに応じてあらかじめ定められた所定のパターンのテスト信号を出力させ、リード部13aを有し当該リード部13a及びプリント配線11aを介して第1のデバイスに接続されたバウンダリスキャン非対応の第2のデバイス13のリード部13aに発生する電圧をプローブ5を介してインサーキットテスト計測部2bにて計測し、協調動作判定部3bにて上記計測した電圧に基づきプリント基板10の第1及び第2のデバイス間の接続不良の有無などを判定する。第1のデバイス12からテスト信号を出力させ、プローブ5にて第2のデバイス13のリード部13aに発生する電圧を計測するので、容易に健全性を判定できる。

(もっと読む)

プリント基板の検査方法及びこれに用いる検査装置

【課題】 プリント基板と半導体集積回路の接続不良を検出すること。

【解決手段】 バウンダリスキャン対応の半導体集積回路が実装されたプリント基板を熱衝撃室2を通過させて熱衝撃を与え、半導体集積回路の入力端子及び出力端子に接続されるプリント基板内配線パターンに対してプローブ37を押し当てる。制御装置4は、入力端子に対応するプローブ37に対してテストデータを与えて、スキャンセルから前記シフト動作により読み出し、前記シフト動作によりデータを出力端子のスキャンセル与えて、当該出力端子から出力させてこれに対応するプローブ37から読み出し、半導体集積回路100に与えたデータと、半導体集積回路101から読み出したデータを比較して、半導体集積回路1001とプリント基板100の接続を判定する。

(もっと読む)

テスト回路

【課題】シリアルパス上のレジスタへの設定、レジスタ値のモニタに必要なシフト数を減らし、テスト時間の短縮が可能なテスト回路を提供する。

【解決手段】本発明のテスト回路は、複数のレジスタがシリアル接続されたシフトレジスタと、バイパス回路71a(71b)と、を備える。シフトレジスタは、回路ユニットに接続される。バイパス回路71a(71b)は、第1のレジスタ711a(711b)の出力が入力される第2のレジスタ712a(712b)と、連続する2つのレジスタ416と425b(415と424b)の間に設けられ、第2のレジスタの出力に応じて、連続する2つのレジスタのうち前段のレジスタの出力、あるいは第1のレジスタの出力、のいずれか一方を選択して、連続する2つのレジスタのうち後段のレジスタに出力する第1のセレクタ713a(713b)と、を備える。

(もっと読む)

積層チップ制御回路および積層半導体装置

【課題】積層チップにおいて、転送データを折り返すエンドチップを自己認識させる。

【解決手段】各半導体チップ(1,2)に共通なSE信号の入力端子(SE)と、SE信号が1つ上のチップで分岐されて戻されたSE2信号の入力端子(SE2)と、SE2信号入力の有無でエンドチップであることを検出するSO制御回路24とを有する。

(もっと読む)

IC端子のための低オーバヘッド・メモリ設計

【課題】出力に安全検査データを設定でき、かつ出力ピンに電圧競合の問題点を有しなく、かつ出力ピンに安定な検査データを維持できる、集積回路のメモリを提供する。

【解決手段】この集積回路は、集積回路の外部からアクセスすることが可能な端子と、前記端子に結合されかつ前記集積回路の外部の信号源により前記端子に加えられる信号を前記端子にラッチするように動作することができる回路とを有する。

(もっと読む)

半導体集積回路および半導体集積回路の試験方法。

【課題】半導体集積回路の外部端子の試験において、より少ない端子で、LSIチップのテストを実現させる。

【解決手段】本発明に係る半導体集積回路のテスト方法は、内部回路と、内部回路と接続される複数の外部端子と、内部回路と複数の外部端子との間に設けられ、複数の外部端子をテストするためのテスト回路とを有する半導体集積回路のテスト方法であって、外部端子に複数の外部出力端子を含む場合に、複数の外部端子を、テスタに接続された1本の共通配線に接続し、テスト回路により、テスタからの制御信号をデコードして選択信号を生成し、当該選択信号により複数の外部出力端子のいずれか1つを選択し、テスタからテスト信号を入力し、選択された一の外部出力端子から当該テスト信号を共通配線に出力し、共通配線を介して出力されるテスト信号を、テスタにて観測することで外部出力端子の導通をテストする半導体集積回路のテスト方法。

(もっと読む)

マルチチップ半導体装置のテストパターン作成方法、作成装置、及び、作成プログラム

【課題】複数の半導体チップを内蔵するマルチチップ半導体装置において、外部端子に接続されるパッドより内部で他の半導体チッブに接続され外部端子には接続されないパッドが多い場合にも効率的にテストパターン作成を行うことができるテストパターン作成方法、作成装置、及び、作成プログラムを提供する。

【解決手段】他の半導体チップのバウンダリスキャンを用いて機能テストの対象とする半導体チップのチップ間接続パッドから入出力されるテストパターンを生成し、外部端子に接続されるパッドから入出力されるテストパターンと合成する。

(もっと読む)

プリント回路基板上の接続をテストする方法および装置

【課題】バウンダリスキャンテストをテスト装置によって自動的に実行する。

【解決手段】PCB31に搭載されたバウンダリスキャン対応デバイス32、33、34、35のバウンダリスキャン対応回路端子を含むリストからデバイス32の第1回路端子37に接続されたバウンダリスキャンセルが、テスト装置42の処理ユニットによってドライバとして作動される。デバイス33の第2回路端子38に接続されたバウンダリスキャンセルが、テスト装置42の処理ユニットによってセンサとして作動される。バウンダリスキャンレジスタから読み出された捕捉データが、ドライバとセンサの間の接続を調べるためにテスト装置42の処理ユニットによって分析される。

(もっと読む)

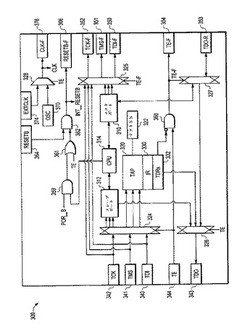

単一のTAP(テストアクセスポート)を介して複数のTAPにアクセスするための方法、および集積回路

【課題】本発明は、単一のTAP(テストアクセスポート)を介して複数のTAPにアクセスする集積回路を提供する。本来は別々のICで使用されるように設計された、種々の再使用可能なICの一部やモジュールの制御およびテストを統合できるようにする。

【解決手段】第1複製状態マシン(26)と第2複製状態マシン(28)をそれぞれ用いることによって、第1状態マシン(20)と第2状態マシン(22)のいずれも修正することなく、第1状態マシン(20)と第2状態マシン(22)を個別にテストする。

(もっと読む)

ASIC及び基板の接続検査方法

【課題】ASICと実装基板間の接続検査を簡単に行う方法を提供する。

【解決手段】集積回路の通常使用されている入出力端子に、並列にドライブ能力の小さいトライステート入出力バッファーを設け、テスト全体を制御するテスト制御回路を設ける。テスト時にはテスト用入力端子から信号を送りテスト制御回路を駆動し、テスト用に設けた入出力トライステート回路の出力側から信号を出力し、その駆動結果を入出力トライステート回路の入力バッファで観測することにより、負荷のプルアップ、プルダウン抵抗があるかどうかをチェックする。

(もっと読む)

1 - 20 / 118

[ Back to top ]