Fターム[2G132AD02]の内容

Fターム[2G132AD02]に分類される特許

1 - 20 / 57

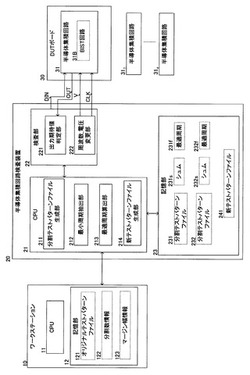

半導体集積回路検査装置,および,半導体集積回路の検査方法

【課題】テスト時間をより短縮するテストパターンを作成する半導体集積回路検査装置,および,半導体集積回路の検査方法を提供する。

【解決手段】半導体集積回路検査装置20は,テストパターンを複数の区間に分割した分割テストパターン毎に,分割テストパターンに対する論理演算を異なる周期のクロック信号に基づき半導体集積回路に実行させることにより得られた半導体集積回路31の故障判定結果に基づき,分割テストパターン毎の最適クロック周期を算出する最適周期算出部213と,テストパターンと,テストパターンに係る分割テストパターン毎の最適クロック周期を有するテストパターンファイルを生成する新テストパターンファイル生成部214を有する。

(もっと読む)

直流電流電圧源および半導体試験装置

【課題】直流の電流および電圧を発生するときに、過剰な消費電力が出力アンプに作用しないように制御することを目的とする。

【解決手段】本発明の直流電流電圧源3は、出力設定部11により設定された設定電圧Vsetを出力する出力アンプ12と、出力アンプ12が出力する出力電圧V1と出力アンプ12に帰還されて入力される入力電圧V2とを入力して、出力アンプ12の消費電力Pampを演算する演算部19と、演算部19により演算された消費電力Pampが予め設定された設定電力Plimを超過しているか否かを比較する比較部20と、消費電力Pampが設定電力Plimを超過しているときには、出力設定部11の設定値を低下させる制御を行う制御部21と、を備えている。

(もっと読む)

段間プローブ用パターン構造、段間測定方法、およびマルチチップモジュール高周波回路

【課題】複数段のトランジスタで構成されるモジュールの段間のSパラメータが測定可能な段間プローブ用パターン構造、段間測定方法、およびマルチチップモジュール高周波回路を提供する。

【解決手段】誘電体基板と、誘電体基板の第1表面上に配置された第1信号伝送線路と、誘電体基板の第1表面上に前記第1信号伝送線路に隣接して配置された一対の第1接地端子電極と、第1接地端子電極の下部に配置された第1VIAホールと、誘電体基板の第1表面と反対側の第2表面に配置され、第1接地端子電極に対して第1VIAホールを介して接続された裏面接地電極とを備える。第1信号伝送線路には高周波プローブの信号端子が接続可能であり、一対の第1接地端子電極には、高周波プローブの一対の接地端子が接続可能である。

(もっと読む)

プローブ検査装置、及びプローブ検査方法

【課題】ナノプロービングにおいてプローブを試料表面に近づける作業を短時間で行う。

【解決手段】プローブ検査装置400は、試料12を載置する試料台10と、試料台10の上方の待機位置に待機するプローブ20と、試料台10をプローブ20の待機位置に向けて移動させる第1の駆動装置160と、試料台10とプローブ20の待機位置の間を通過する方向に第1の荷電粒子線32を照射する第1の荷電粒子銃30と、試料12が第1の荷電粒子線32を遮断したことを示す信号を生成する第1の検出部120と、第1の検出部120が生成した信号により第1の駆動装置160を制御する第1の制御部140を備える。

(もっと読む)

半導体集積回路

【課題】 チップ内の任意の位置のトランジスタの特性をモニタすることが可能な半導体集積回路を提供する。

【解決手段】 テスト回路13-1、13-2は、複数のトランジスタを含む機能ブロック12-1〜12-nの近傍の領域に配置され、第1のフリップフロップ回路13aと、第2のフリップフロップ回路13bと、第1、第2のフリップフロップ回路間に接続された少なくとも1つのインバータ回路21,31,41とを含んでいる。信号生成回路14は、第1のクロックパルスと第2のクロックパルスを含むクロックパルスを生成し、かつ、第1、第2のクロックパルスのパルス間隔を制御可能とされている。テスト時、第1のフリップフロップ回路は、信号生成回路の第1のクロックパルスに同期してデータを出力し、第2のフリップフロップ回路は、信号生成回路の第2のクロックパルスに同期してデータをラッチする。

(もっと読む)

半導体コンポーネントとウエハの製造を評価するための手法

【課題】ウエハの製造を分析するためのアッセンブリを提供する。

【解決手段】ウエハが部分的に製造された状態である時点からでも、ウエハの製造を分析することができる。特定の性能パラメータ値は、ウエハのダイの能動領域の複数の箇所で決定することができる。特定の性能パラメータが、製造の特定の製造プロセスを示すことは周知である。このとき、評価情報は、複数の箇所における性能パラメータ値の変動に基づいて得ることができる。これは、ダイから生成されるチップの有用性に影響を及ぼさずに実施可能である。評価情報は、性能パラメータ値が示した特定の製造プロセスを含む1つ以上のプロセスが実施された方法を評価するために使用することができる。

(もっと読む)

半導体試験装置および半導体試験方法

【課題】演算処理に応じてDSPモジュールを逐次的に実行させるのか、並列的に実行させるかを最適に選択し、演算時間の短縮化を図ることを目的とする。

【解決手段】複数のCPUを備えるDSPモジュール4と演算処理が記述されたテストプログラムに従ってDSPモジュール4の制御を行うテスタコントローラ3とを備える半導体試験装置であって、テスタコントローラ3に備えられ、テストプログラムに記述されている演算処理に基づいて、DSPモジュール4に演算処理を逐次的に実行させるシングルモードと並列的に実行させるマルチモードとのうち何れか一方の動作モードを選択する動作モード選択部15と、DSPモジュール4に備えられ、動作モード選択部15の選択に基づいて1つのCPUを逐次的に動作させるか2つ以上のCPUを並列的に動作させるかの選択を行うCPU制御部24と、を備えている。

(もっと読む)

データ解析のための方法および装置

【課題】データ解析のための方法および装置、特に半導体試験データ解析に適したデータ解析のための方法および装置を提供すること。

【解決手段】本発明の種々の側面にしたがうデータ解析のための方法と装置は、コンポーネントに対する試験データのようなデータ内の統計的外れ値(大きなデータ母集団のサブセット内の外れ値を表す混成外れ値を含む)を識別する。本発明の種々の側面にしたがう方法および装置は、半導体をテストするための自動テスト設備(ATE)のようなテスタを有するテストシステムと協働し得る。外れ値は、データの分布に従って識別および分類することができる。

(もっと読む)

回路入力及び回路状態評価方法並びに評価装置

【課題】回路入力と回路状態との関係を定量的かつ詳細に評価することができる回路入力及び回路状態評価方法並びに評価装置を提供すること。

【解決手段】トランジスタ回路2の入力端子10に入力電圧を印加する入力ステップ(S01)と、各MOSトランジスタM11,M12,M21,M22からの出力電圧(出力信号)に基づき、各MOSトランジスタM11,M12,M21,M22の動作状態を算出する算出ステップ(S02)と、入力電圧の変化量又は印加時間に応じて算出された動作状態を連続的に表示する表示ステップ(S03)と、詳細評価のために表示された動作状態から少なくとも一部の動作状態を一定のアルゴリズムに従って選択する選択ステップ(S04)と、選択された動作状態を変化させる新たな入力信号を生成する生成ステップ(S05)と、を備えている。

(もっと読む)

チップの欠陥検出のために関連度値を判定し、チップ上の位置で欠陥確率を判定する方法及び装置

関連度値(R(i,m))を判定する方法を記載する。各関連度値は、チップ上の欠陥検出において、第1個数(I個)の入力ノードの入力ノード(i)と、第2個数(M個)の測定ノードの測定ノード(m)との組み合わせ((i,m))の関連度を表す。該方法は、第1個数(I個)の入力ノードで第3個数(K個)のテストを適用することと、第2個数(M個)の測定ノードの各測定ノード(m)につき、第3個数(K個)の測定値を得るため、第3個数(K個)のテストの各テスト(k)につき、第2個数(M個)の測定ノードの各測定ノードで信号を測定することと、関連度値(R(i,m))を判定することと、を含み、第3個数(K個)のテストの各テスト(k)は、各入力ノード(i)につき、テスト入力チョイス(U(k,i))を指定し、各測定値(Y(k,m))は、測定を行ったテスト(k)と測定が行われたところの測定ノード(m)に対応付けられ、各関連度値は、各組み合わせの入力ノード(i)に指定された第3個数(K個)のテスト入力チョイス(U(k,i))と、各組み合わせ(i,m)の測定ノード(m)に対応する第3個数(K個)の測定値(Y(k,m))との相関に基づいて計算される。 (もっと読む)

散乱パラメータを決定する測定システム

本発明は、少なくとも1つの測定チャネル(18,20,22,24)と、少なくとも1つの測定チャネル(18,20,22,24)に電気的に接続され、電子回路内の電気測定対象物(40,42,44,46,48)の電気信号線(50)に非接触または接触接続するように設計された少なくとも1の測定プローブ(28)とを有する測定装置(10)を有する、基板(38)上の電気測定対象物(40,42,44,46,48)の散乱パラメータを決定する測定システムに関する。本発明によれば、第1の位置決め装置(30)は、少なくとも1つの測定プローブ(28)を備え、少なくとも1つのセンサ(34)は、少なくとも1つの測定プローブ(28)の位置を検出し、位置信号を出力する。  (もっと読む)

(もっと読む)

半導体回路、及び半導体回路のストレス試験方法、半導体回路

【課題】 半導体回路内のMOSFETに対して、ダメージを与えることなく効率的にストレス印加が可能なストレス試験回路を提供する。

【解決手段】 電源電圧Vccと接地電圧Vssの中間電圧を示す一または複数の中間ノードの何れかとなる半導体回路に対してストレス試験を行う回路であって、中間ノードとならないNMOS11及び12のソースに対してVccとVssの何れか一方を選択的に印加可能な第1電圧線3aと、NMOSのバックゲートに対してVssを印加可能な第2電圧線3bと、中間ノードとならないPMOS21及び22のソースに対してVccとVssの何れか一方を選択的に印加可能な第3電圧線2aと、PMOSのバックゲートに対してVccを印加可能な第4電圧線2bと、中間ノードN1〜N3のそれぞれに対して、Vssを印加するか、Vccを印加するか、もしくは電圧を印加しないかの何れか一を選択的に制御可能な駆動部6とを備える。

(もっと読む)

回路基板検査装置

【課題】検査用治具を移動させるべき移動量を短時間で容易に取得する。

【解決手段】保持部によって短絡板が保持されている状態において、制御部が、保持部に対する接近方向に検査用治具を移動させる第1の処理(ステップ71,74,76)と、測定部を制御して電気的パラメータを測定させる第2の処理(ステップ72,78)とを交互に実行すると共に、第2の処理の実行開始の度に保持部に対して検査用治具が徐々に接近するように第1の処理において検査用治具を移動させ、かつ、第2の処理時において検査用プローブと短絡板との接続を示す電気的パラメータが規定数の検査用プローブ(一例として、すべての検査用プローブ)について測定されたときに(ステップ79)、その第2の処理時における検査用治具の位置に基づいて、検査用治具を待避位置から検査位置まで移動させる移動量を特定可能な移動量情報を取得する。

(もっと読む)

半導体試験装置

【課題】DSPのテストプログラムのデバッグをいつでも必要なときに仮想環境を用いて行うことができる半導体試験装置を実現すること。

【解決手段】DSPでDUTの測定データの演算処理を行うように構成された半導体試験装置において、前記DSPに前記DUTの測定データを収集格納する測定ファイル格納手段を設け、この測定ファイル格納手段に格納された測定データに基づき前記DSPのデバッグを行うことを特徴とするもの。

(もっと読む)

自動試験装置システム用追跡回路及び方法

受信ディジタルデータ信号同期化用のディジタルデータ信号捕獲回路は受信ディジタルデータ信号の状態遷移を検出する遷移検出器を含む。遷移検出器は受信ディジタルデータ信号を第1時刻、第2時刻及び第3時刻でサンプルし、第1時刻と第2時刻の間で状態遷移が発生したかどうか及び第1時刻と第3時刻の間で状態遷移が発生したかどうかを決定し、遷移の位置を示すインクリメント/デクリメント信号を発生する。プローブ調整回路がインクリメント/デクリメント信号に基づいてストローブ信号を発生する。捕獲回路がストローブ信号を用いて受信ディジタルデータ信号を捕獲する。  (もっと読む)

(もっと読む)

半導体評価回路及び半導体評価方法

【課題】大規模な被測定トランジスタの特性を高精度かつ高速に測定する。

【解決手段】n×m個の評価セルと、n本の行選択線と、m本の列選択線と、第1及び第2の共通プリチャージ線と、プリチャージ回路と、第1及び第2のビット線と、第1及び第2の列選択スイッチとを具備し、前記評価セルの各々は、第1及び第2の被測定トランジスタと、自己の行に属する行選択線に供給される行選択信号に応じて、自己の列に属する第1のビット線と第1の被測定トランジスタの出力端子との接続/非接続を切り替えるための第1の行選択スイッチ、及び第2のビット線と第2の被測定トランジスタの出力端子との接続/非接続を切り替えるための第2の行選択スイッチとを少なくとも有し、第1及び第2の被測定トランジスタのゲート端子に入力されるゲート電圧差に応じた差動増幅動作を行う差動増幅回路と、差動増幅回路の2つの出力をさらに増幅する増幅回路とを備える。

(もっと読む)

シュムーパラメータ設定装置およびシュムーパラメータ設定方法

【課題】シュムーパラメータの作成を少ない操作で容易に行うことを可能とするシュムーパラメータ設定装置およびシュムーパラメータ設定方法を提供する。

【解決手段】アイテム名文字列24がシュムーパラメータ設定エリア21にドロップされると、指定受付手段12は、ドラッグしてきたアイテム名文字列24に対応するアイテムの指定を受け付け、パラメータ抽出手段13は、デバッガのドラッグ位置から判別する当該アイテムの補助情報(ピン番号・チャネル番号/タイミングセット番号/エッジ)を、テストプログラムの記述内容に基づいて判別する。設定手段14は、アイテム名文字列24に対応するアイテムと、デバッガのドラッグ位置から判別されたアイテムの補助情報とを、シュムーパラメータとしてシュムーパラメータ設定エリア21に自動設定する。

(もっと読む)

シミュレータ、及び当該シミュレータを用いた素子耐圧検証方法

【課題】検証の対象のCMOS型半導体論理回路がカスコード接続された複数のMOS素子を含む構成であったとしても、各MOS素子の耐圧検証を常に正しく判定する。

【解決手段】CMOS型半導体論理回路をインバータ単位の複数の分離回路に分離し、さらに、各分離回路の内部にフローティングノードが存在する場合に、フローティングノードの存在形態に応じて、各分離回路に含まれている各MOS素子の接続関係を部分的に変更する回路接続変更部120と、各分離回路に含まれている各MOS素子をOFF状態の素子として機能する高抵抗素子またはON状態の素子として機能する低抵抗素子に置き換える抵抗置換部125と、各分離回路に含まれている各高抵抗素子及び各低抵抗素子の定常状態時の電圧降下量を算出する定常解析部140と、各高抵抗素子の定常状態時の電圧降下量と素子基準耐圧とを比較して、各高抵抗素子の電圧降下量が素子基準耐圧よりも大きいか否かを判定する素子耐圧検証部145とを有する。

(もっと読む)

データ解析のための方法および装置

【課題】半導体製造に好適なデータ解析のための方法および装置を提供する。

【解決手段】ウエハ上に製造された複数のコンポーネントに対する試験データのようなデータ内の統計的外れ値(大きなデータ母集団のサブセット内の外れ値を表す混成外れ値を含む)を識別するための方法と装置を、半導体をテストするための自動テスト設備(ATE)のようなテスタを有するテストシステムおよびこれと協働し得るコンピュータ支援システムにより、外れ値をデータの分布に従って識別および分類することで実現する。

(もっと読む)

波形発生装置、A/D変換回路の検査方法および故障予測方法

【課題】

電子回路の動作の確認や検証試験を容易にかつコストをかけずに行える間欠的に多様な非連続信号を出力する信号発生装置を提供する。

【解決手段】

入力信号の周波数の変化に対して出力波形に時間遅れを生じる周波数応答特性を持った回路に方形波を入力すると、出力波形に過渡応答特性としてアンダーシュートとリンキングとオーバーシュートとリンキングが生じる。この現象を積極的に活用して、減衰振動波形を生成して連結し、波形の形や周波数を自由に変更できる間欠した非連続波形を生成することにある。

(もっと読む)

1 - 20 / 57

[ Back to top ]