Fターム[2G132AF18]の内容

Fターム[2G132AF18]に分類される特許

1 - 20 / 206

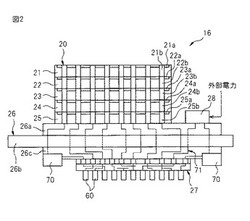

検査装置及び検査システム

【課題】汎用性を有し、高速で動作する半導体装置を検査できる検査装置を提供する。

【解決手段】検査装置は、第1貫通電極24bと、テスト信号を生成する信号生成ユニット30とを有する第1半導体基板24と、複数の接触子60を有するプローブ基板27と、第2貫通電極25bと、複数の接触子60と信号生成ユニット30との間の信号経路をプログラム可能に設定するスイッチマトリックス20eとを有する第2半導体基板と、を備え、第1半導体基板24と第2半導体基板25とは積層されており、第1貫通電極24bは、信号生成ユニット30が生成したテスト信号をスイッチマトリックス20eに伝達し、第2貫通電極25bは、スイッチマトリックス20eによって経路設定されたテスト信号を所定の接触子60に伝達し、信号生成ユニット30から、着脱自在に接続される電気的接続部を介さずに、接触子60にテスト信号が伝達される。

(もっと読む)

スイッチ装置、伝送路切替装置、および試験装置

【課題】長寿命化した圧電式アクチュエータを備えるスイッチ装置。

【解決手段】第1接点が設けられた基体と、第2接点を移動させて第1接点と接触または離間させるアクチュエータと、を備え、アクチュエータは、支持層と、支持層の上面に形成される第1圧電膜と、支持層を介して第1圧電膜に対向して、支持層の第1圧電膜が形成される面とは反対側の面に設けられ、駆動電圧に応じて伸縮してアクチュエータのそり量を変化させる第2圧電膜と、第1圧電膜および第2圧電膜のそれぞれの上面と下面とに、それぞれの駆動電圧を印加する電極層と、第2圧電膜と第2圧電膜の支持層側とは反対側の電極層との間に形成された導電性酸化物を含む第2導電性酸化物膜と、を有するスイッチ装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】ウエハの電気特性検査時にプローブ針の先端に付着する異物に起因する検査精度の低下を抑制する。

【解決手段】ウエハの電気特性検査工程で使用するプローブカード15Aは、配線基板30と、配線基板30に取り付けられた金属製のプローブ針固定部31と、プローブ針固定部31に接合された複数のプローブ針33とを有している。プローブ針固定部31には、冷却管24が挿通されており、この冷却管24内を流れる冷却液Cによって、プローブ針固定部31に接合されたプローブ針33が冷却されるようになっている。

(もっと読む)

スイッチ装置、伝送路切り替え装置、製造方法、および試験装置

【課題】剛性を高めつつ、物理的な破壊を防いだアクチュエータを提供する。

【解決手段】スイッチ装置は、第1接点122が設けられた基体110と、第2接点134を移動させて第1接点122と接触または離間させるアクチュエータと、を備え、アクチュエータは、支持層150と、支持層150上に形成され、第1駆動電圧に応じて伸縮する第1圧電膜136と、第1圧電膜136上に絶縁材料で形成され、第1圧電膜136の端部の少なくとも一部において支持層150と接して端部を覆う第1保護膜152と、を有する。

(もっと読む)

テスタコントローラおよびコンピュータプログラム

【課題】コストアップを招くことなく、簡易な構成で、負荷変動に対する出力電圧の変動を少なくする。

【解決手段】パタンプログラムを実行し、試験対象デバイスに印加するテストパタンを半導体試験装置に出力するパタンプログラム実行部と、テストパタンに同期して半導体試験装置から試験対象デバイスに供給される電圧値の変動を測定し、変動を少なくする電圧補正値と補正タイミングとを設定する電圧補正処理部と、所望の電圧値に対して、補正タイミングにおいて電圧補正値を用いて補正した電圧値を、半導体試験装置に設定する電圧制御部とを備えたテスタコントローラ。

(もっと読む)

半導体試験装置

【課題】従来のタイミング発生器を用いて、異なるタイミングで動作可能なピン数を増加させる。

【解決手段】パタン信号とエッジ信号とに基づいてドライバ波形を整形する複数個の波形整形器と、指定されたタイミングでエッジ信号を各波形整形器に出力するドライバタイミング発生器と、ドライバタイミング発生器にエッジ信号の出力タイミングを指示するとともに、複数個の波形整形器に独立にパタン信号を出力するフォーマッタとを備えた半導体試験装置。

(もっと読む)

プロービング装置

【課題】多点波形測定を必要とする電子部品の電気特性試験において、安価な構成で、かつ簡易な制御によって、被測定物測定点間が狭ピッチであっても、問題なく自動的にプロービングが可能なプロービング装置を得ること。

【解決手段】支持構造体5に垂直固定支持させた多数の両端コンタクトプローブ3の下方端を被測定物1が有する多数の被測定物測定点2に接触設定し、上方端を測定用回路基板8のS面パッド9に接触設定しておく。測定用回路基板8のY軸方向両端におけるC面信号パッド10a、10b及びC面GNDパッド11a,11bはX軸方向に所定数設けてありそれらをプロービングするプローブ12a,12b及びコンタクトプローブ13a,13bをX軸とZ軸の2軸のうちの少なくともZ軸方向に移動制御する。測定用回路基板8は、任意のS面パッド9に伝達された測定点の電気信号を表面信号パッドに伝達できる回路構成になっている。

(もっと読む)

半導体試験装置

【課題】半導体リレーを多段の階層構造としている場合に、正確なタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置2は、DUT1の試験を行うための信号を出力する複数のドライバ10と、ドライバ10の出力側に接続した出力抵抗12と、ドライバ10のタイミングを校正するために設けた基準コンパレータ6と、2以上のドライバ10から1つのドライバ10を選択する校正リレー30を1つのリレー群として多段の階層構造としたドライバ選択部5と、リレー群の中で1つの校正リレー30のみをオンにし、他の校正リレー30をオフに制御するリレー制御部31と、を備えている。

(もっと読む)

プリント基板劣化検査装置および劣化検査方法

【課題】プリント基板を破壊することなく、故障発生前にプリント基板またはプリント基板上の回路(検査部位)の修理もしくは交換を容易にできる劣化検査装置を提供する。

【解決手段】プリント基板劣化検査装置は、パルス波を出力するパルス発生器51と、プローブ32と、オシロスコープ53と、コンピュータ60とを備える。プローブ32は、検査部位と接続されたプリント基板上の配線パターンにパルス波を印加するために用いられる。オシロスコープ53は、パルス波がプリント基板から反射された反射波を、プローブ32を介して測定する。コンピュータ60は、プリント基板または検査部位に対して測定された反射波と比較のための参照用波形に基づいて、プリント基板あるいは検査部位の劣化を判定する。

(もっと読む)

半導体試験装置

【課題】半導体試験装置のシステム周波数よりも高い周波数の論理信号を低コストで生成出力することができ、リアルタイムにエッジや周波数を変更でき、高精度のタイミング精度が得られる半導体試験装置を提供すること。

【解決手段】半導体試験装置に内蔵されている信号発生部から出力される複数系統の論理信号を加算する加算器とこの加算器の出力をリタイミングクロックにしたがって取り込むラッチとこのラッチ出力を選択的に出力するスイッチとで構成された複数のパターン信号発生ユニットと、これら複数のパターン信号発生ユニットからスイッチを介して出力される出力信号間のスキューを補正する校正経路が設けられた半導体試験装置において、

前記リタイミングクロックは少なくとも2系統の論理信号を加算することにより生成され、前記校正経路は、前記各パターン信号発生ユニットのスイッチに連動して駆動され択一的に所定の出力信号を選択するロジックゲートを含むことを特徴とするもの。

(もっと読む)

スイッチ装置および試験装置

【課題】圧電素子を設けたアクチュエータの接点同士の凝着を防止するスイッチ装置を提供する。

【解決手段】スイッチ装置100は、第1接点122が設けられた接点部と、第1駆動電圧に応じて伸縮する第1圧電膜136、および第1圧電膜136と並行して設けられて第2駆動電圧に応じて伸縮する第2圧電膜138を有し、第1圧電膜136および第2圧電膜138の伸縮に伴い第2接点132を移動させて第1接点122と接触または離間させるアクチュエータと、第1駆動電圧および第2駆動電圧を制御する制御部200と、を備え、制御部200は、第1接点122および第2接点132を接触状態から切断状態へと切り替える場合に、第1駆動電圧を遮断すると共に、第2圧電膜138を伸ばす第2駆動電圧を第2圧電膜138に印加してアクチュエータの戻りを付勢する。

(もっと読む)

半導体試験装置および半導体試験装置における静電気保護方法

【課題】静電気耐量を高めた半導体試験装置を提供する。

【解決手段】測定対象デバイスに電気信号を出力する1または複数個の信号出力部と、信号出力部に対応して設けられ、信号出力部と測定対象デバイスとの間の電気的接続のオンオフを切り替える半導体リレーと、測定対象デバイスとの直接的あるいは間接的な接続の前に、半導体リレーをオンにする制御部とを備えた半導体試験装置。測定対象デバイスとの直接的あるいは間接的な接続の前に、さらに、信号出力部から0Vの電圧を出力させるようにしてもよい。

(もっと読む)

試験装置およびプログラム

【課題】試験装置は、パフォーマンスボードを接続しない状態で設定したドライバおよびコンパレータに対する補正値が、設定可能範囲の上限値または下限値に近い値の場合、パフォーマンスボードを接続した状態でのキャリブレーションにおいて、補正値を更に調整できる余地が少なくなる。

【解決手段】設定された出力補正値を出力設定値に加減算する補正部と、格納したオフセット値を出力設定値に加減算する第1加減算部と、第1出力補正値を算出し、設定可能範囲内の基準値および第1出力補正値の差分をオフセット値として第1加減算部に設定し、第2出力補正値を、基準値を基準として算出して補正部に設定する設定部とを有する試験装置。

(もっと読む)

異常通知システムおよび半導体試験装置

【課題】異常検出回路が異常を検出したときに迅速且つ確実に異常処理を行うことを目的とする。

【解決手段】複数の下位モジュール4とこれらの下位モジュール4の制御を行う上位モジュール3との間をバス2により接続した異常通知システム1は、下位モジュール4から上位モジュール3に割込み信号を出力するシリアル伝送経路5と、下位モジュール4に備えられ、複数の異常検出回路20が異常を検出したことを示す異常情報に下位モジュール4を特定するモジュール特定情報を付加した複数ビットの出力情報をパラレルデータからシリアルデータに変換してシリアル伝送経路5に出力するパラレルシリアル変換部24と、上位モジュール3に備えられ、シリアル伝送経路5から入力した出力情報をシリアルデータからパラレルデータに変換して異常情報およびモジュール特定情報を得るシリアルパラレル変換部12と、を備える。

(もっと読む)

電荷検出回路およびその検査方法

【課題】静電気等に対する耐久性を向上するとともに、検査精度を向上し、かつ、検査時間を短縮した積分アンプを提供する。

【解決手段】演算増幅器OP、および、演算増幅器OPの反転入力端子と出力端子との間に接続したサンプリングキャパシタCfを備えた積分回路41を有する。入力端子部INと演算増幅器OPの反転入力端子との電気的接続の開閉を切り換え可能なモードスイッチSWtestを有する。移送キャパシタCT、および、移送キャパシタCTを充放電させるスイッチSW1〜SW4を備えた検査用回路42を有する。検査用回路42は、移送キャパシタCTの放電により、充電した電荷の一部をサンプリングキャパシタCfに送り込む。スイッチSW1〜SW4により移送キャパシタCTを充電させている状態でサンプリングキャパシタCfを放電させる放電スイッチSWinitを有する。

(もっと読む)

半導体試験装置および半導体試験方法

【課題】分岐命令や変数指定の命令を有するテストプログラムに基づいて試験を行う場合であっても、試験時間の短縮化と同時に試験の正確性の確保を図ることを目的とする。

【解決手段】DUTの試験を行うための1または複数のPEカード3を制御するテスタコントローラ2を備える半導体試験装置1は、テスタコントローラ2に備えられ、試験を行うためのテストプログラム13に基づいて順次コマンドを発行してPEカード3に出力し、分岐命令を読み出したときには分岐条件が確定するまでコマンドの発行を停止し、変数を指定している命令を読み出したときには変数の値が確定するまでコマンドの発行を停止するコマンド発行部12と、PEカード3に備えられ、順次入力したコマンドに基づいて試験を行うための設定値データを記憶する制御レジスタ21と、を備えている。

(もっと読む)

ピンエレクトロニクス回路およびそれを用いた試験装置

【課題】伝送線路のシミュレーションモデルを簡易に抽出可能な試験装置を提供する。

【解決手段】I/OピンPI/Oは、DUTと伝送線路20を介して接続される。ドライバDRは、DUTに供給すべき試験信号を生成する。ドライバ側スイッチ22および出力抵抗Roは、ドライバとI/OピンPI/Oの間に直列に設けられる。コンパレータCPは、その入力端子がI/OピンPI/Oと接続され、DUTからの信号のレベルを判定する。ショートスイッチ34は、I/OピンPI/Oと接地端子の間に設けられる。

(もっと読む)

半導体試験装置

【課題】テストプログラムの記述が誤っている場合でも、DUT100を破壊や損傷から保護することができる半導体試験装置を実現する。

【解決手段】被試験対象デバイスに電圧または電流を印加して試験を行う半導体試験装置において、被試験対象デバイスを試験する試験内容が記述されたテストプログラムと被試験対象デバイスに印加できる電圧または電流の許容範囲が記述されたシステム特性記述ファイルとを記憶する記憶部と、テストプログラムとシステム特性記述ファイルとを記憶部から取得し、テストプログラム実行時に許容範囲に基づいてテストプログラムの設定をチェックし、設定が許容範囲を超えていた場合にユーザにエラーを通知するテスタ制御部と

を備える。

(もっと読む)

テストヘッド、試験ボードおよび試験装置

【課題】テストヘッド上に被試験デバイスを載置するための接続部を載置している状態で、内部の試験ボードを挿抜する。

【解決手段】被試験デバイスを試験する試験ボードを保持するテストヘッドであって、試験ボードの挿抜用の開口が1つの側面に形成され、試験ボードの上辺を上面に向けた状態で試験ボードを内部に保持する筐体と、試験ボードの下辺を開口から予め定められた位置までガイドし、試験ボードの下辺に対して上側への力を加えて試験ボードを筐体に装着させる装着用部材と、を備えるテストヘッドを提供する。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング調整方法

【課題】リレーとDUTとの間の伝送経路による波形劣化を反映したストローブ信号のタイミング調整を行うことを目的とする。

【解決手段】ドライバ部とコンパレータ部とを設けたユニット2を有する半導体試験装置1であって、ユニット2は、コンパレータ部の判定タイミングを規定するストローブ信号を遅延させて判定タイミングを調整するストローブ信号遅延回路17と、判定タイミングの調整を行うときに、ドライバ部とDUT3との間の接続をオフにするリレー部14と、リレー部14とDUT3との間の伝送経路の波形劣化に基づくタイミングのずれを補正するための補正データを記憶する補正データ記憶部21と、ドライバ部の駆動タイミングを規定するタイミング信号またはストローブ信号を発生するときに、補正データの分を遅延させて発生させるタイミング発生器11と、を備えている。

(もっと読む)

1 - 20 / 206

[ Back to top ]