Fターム[2G132AG14]の内容

電子回路の試験 (32,879) | 信号の印加に関するもの (2,293) | 試験用データの作成 (324) | シミュレーション技術を用いるもの (115)

Fターム[2G132AG14]の下位に属するFターム

回路設計データ(仕様)を用いるもの (44)

Fターム[2G132AG14]に分類される特許

1 - 20 / 71

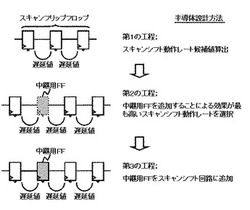

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

解析プログラム,解析装置および解析方法

【課題】スピードパス解析の解析精度を向上させる技術を提供する。

【解決手段】第1の解析部15は,パス遅延情報記憶部120から,テスト対象回路に対するディレイテストの結果から得られるパス遅延の実測値を取得する。第1の解析部15は,予測値記憶部130から,テスト対象回路に対するタイミング解析により得られるパス遅延の予測値を取得する。第1の解析部15は,特徴値記憶部140から,遅延に影響する要因ごとの特徴値を取得する。第1の解析部15は,取得したパス遅延の実測値と,パス遅延の予測値と,要因ごとの特徴値とを用いて,要因ごとの特徴値からパス遅延の実測値と予測値とのずれを算出するずれ算出モデルを求める。このとき,第1の解析部15は,パス遅延の実測値が得られない活性化パスについて,パス遅延の実測値の代わりにディレイテストで測定した最大周波数に対応する遅延の値を用いて,解析を行う。

(もっと読む)

テスト装置、テスト方法、プログラム及び記録媒体

【課題】 テストパワー考慮型のテスト生成において、テストパターン安全性を保証することを達成するテスト装置等を提供する。

【解決手段】 論理回路の故障の有無を判定するテスト装置であって、初期テストキューブが与えられ、初期未定値ビットに論理値を割り当てて中間テストパターンを生成する手段と、テストパターンが印加された論理回路に故障がなければ危険ビットが存在しないというテストパターン安全性を判定する手段と、テストパターン安全性を保証することに寄与しうる候補ビットを特定する手段と、初期未定値ビットにも候補ビットにも対応した中間テストパターンの入力ビットを新規未定値ビットとして新規テストキューブを生成する手段と、新規未定値ビットに論理値を割り当てて最終テストパターンを生成する手段と、最終テストパターン安全性を判定する手段と、論理回路テストにおいて危険ビットを使用させないマスク手段とを備える。

(もっと読む)

カレントプローブモデル化方法、カレントプローブモデル作成装置、シミュレーション方法、シミュレーション装置、及びプログラム

【課題】BCI試験のシミュレーションをより短時間に行えるようにする技術を提供する。

【解決手段】BCI試験で伝送線にバルク電流の注入に用いるカレントプローブは、伝送線にバルク電流を直接、注入する電圧源と見なし、モデル化する。それにより、カレントプローブは電圧源モデル20で模擬する。カレントプローブは電圧の印加により信号線に電流を注入する。そのようにして注入される電流は、周波数と電圧振幅値のテーブルデータ25に格納された周波数と電圧振幅値の組み合わせにより制御する。このために、周波数と組み合わせる電圧振幅値は、その周波数で実際に注入される電流の電流振幅値と、電圧源モデル20と伝送線を含む測定用回路のシミュレーションにより得られるその電流振幅値とが一致するように選択される。

(もっと読む)

マルチステージ・テスト応答コンパクタ

【課題】より高い圧縮比を提供し得る圧縮スキームを提供する。

【解決手段】いわゆる「Xプレス」テスト応答コンパクタ110、152は、オーバードライブ・セクションとスキャンチェーン選択ロジックとを含む。実施形態は約1000倍の圧縮比を提供する。例示的な実施形態は、従来のスキャンベースのテストシナリオとほぼ同じカバレッジおよびほぼ同じ診断分解能を維持できる。スキャンチェーン選択スキームのいくつかの実施形態は、テスト応答で発生してコンパクタに入る未知状態を有意に減らすことができ、または完全に排除できる。また、オンチップ・コンパクタ回路の実施形態および選択回路をマスクする制御回路網を生成する方法も開示する。

(もっと読む)

半導体集積回路のシミュレーション装置、シミュレーション方法およびシミュレーションプログラム

【課題】検証対象の回路が要求特性を満たしているか否かを、製造ばらつきを考慮して短時間で実行。

【解決手段】回路のネットリストを格納する回路情報格納部10と、検証する第1回路特性の種類を提供する検証項目提供部20と、各種素子の特性を、製造ばらつき範囲の下限値、Typ値、上限値の複数のパラメータファイルを格納するパラメータ格納部40と、回路に含まれる第1素子及び第2素子のそれぞれに対して、最小値用又は最大値用ばらつき項目リスト生成部50と、最小値と最大値との少なくとも一方を検証することを含むシミュレーション条件提供部60と、最小値と最大値との少なくとも一方を検証する情報に基づいて、製造ばらつき情報を生成する製造ばらつき情報生成部70と、製造ばらつき情報と、ネットリストと、シミュレーション条件とに基づいて、回路シミュレーションを実行する回路シミュレーション実行部90とを具備する。

(もっと読む)

集積回路、シミュレーション装置、及びシミュレーション方法

【課題】LSIを実際の使用形態に沿って動作させるような入力パターンを用いて、LSI内部の遅延故障をLSI外部において効率良く検出することを目的とする。

【解決手段】開示の装置は、LSIのディレイテスト用のディレイテストパターンを生成する制御を行う。入力パターン制御回路は、被試験対象回路へ供給される入力パターンのサイクル数をカウントし、予め設定されたカウント数と一致した時点で、被試験対象回路への入力パターンの供給を停止し、入力パターン保存回路は、このような入力パターンを保存する。スキャン制御回路は、入力パターン制御回路からの制御信号を受け、被試験対象回路へスキャンシフト信号を供給し、被試験対象回路内のスキャンチェインをシフトさせる。そして、期待値生成回路は、スキャンチェインの出力を期待値データとして保存する。

(もっと読む)

テスタシミュレーション装置、テスタシミュレーションプログラムおよびテスタシミュレーション方法

【課題】論理検証およびテストデバッグに要する総時間の短縮化を図ることを目的とする。

【解決手段】テスタによるDUTの試験を仮想的にシミュレーションするテスタシミュレーション装置1は、DUTの動作をシミュレータ上でモデル化した仮想デバイス11と、仮想デバイス11の論理検証を行うための検証シナリオの入力パターンを仮想デバイス11に印加し、仮想デバイス11から出力される応答パターンを入力して期待値パターンと比較して良否判定を行う仮想テスタ12と、入力パターンおよび期待値パターンを仮想テスタ12から取得し、入力パターンおよび応答パターンが正常なものであるときに、取得した入力パターンおよび期待値パターンをDUTの実試験を行うためのテストパターンとして生成するテストパターン生成部14と、を備えている。

(もっと読む)

半導体集積回路設計方法

【課題】従来に比べて検証期間を短縮できる半導体集積回路設計方法を提供すること。

【解決手段】処理(ST1)では、半導体集積回路の設計仕様31に対してハードウェア記述言語を用いてRTL(Registor Transfer Level)で記述され、複数のレジスタを表すRTLデータ32を生成する。処理(ST2)では、検証用のデータの事象34に従って、RTLデータ32における複数のレジスタのうちのスキャン対象レジスタ群と、端子情報35(SI、SO、MD)とを用いて、シフトレジスタ構成(SI、SO、MD)となるようにスキャン対象レジスタ群が接続された仮想スキャンチェーンを生成する。処理(ST3)では、検証用のテストパターン33及び事象34に従って、仮想スキャンチェーンに対するシミュレーションを実行する。その実行結果に問題がある場合(ST4−NG)、処理(ST1)を再度実行する。

(もっと読む)

故障マスキング係数を定めるための逆方向解析の改善

電子回路内の故障可観測性を定めるための方法及び構成が提示される。本方法では、各素子について、発生した故障が解析出力信号における異常を引き起こしうる期間が定められる。 (もっと読む)

相関図を用いた論理検証方式

【課題】

論理回路の妥当性をシミュレーションによって確認する為のテストデータの数は、確認内容の増加,論理回路の規模増加及び組合せ状態数の増加によって増え、シミュレーションに必要な時間が増えるという問題があった。また、論理回路が複雑さを増す事により、テストデータを作成する事も困難になるという問題があった。

【解決手段】

観測点を設けた論理回路とテストデータをシミュレーションして得た実行結果から、テストデータ−観測点相関図生成機能によってテストデータ−観測点相関図を生成し、テストデータと論理回路動作部の関係を可視化する。また、相関図から抽出した特徴に基づいて、テストデータの生成を制御する。

(もっと読む)

論理検証実行システム

【課題】

乱数要素を持たせた論理検証において、検証論理にあるフリップフロップのうち全く動作しないものや、動作回数が著しく低いものがある。そして、検証論理に含まれるフリップフロップ全てがあらゆる条件下で動作するまで検証を行うと検証期間の増大する。

【解決手段】

検証論理に入力する命令およびデータのパターンを乱数を用いて生成するための制約条件を定義したシナリオファイルを複数用意し、複数のファイルから実行対象とするファイルをランダムに選び、検証実行時にカバレッジ情報を出力し、蓄積したカバレッジ情報を用いて低動作回数フリップフロップを抽出し、抽出したフリップフロップを動作させたファイルが多く実行されるように動作回数に応じて実行確率を算出する処理を行うことで、抽出したフリップフロップを動作させたファイルの実行回数を上げ、検証論理にある全フリップフロップの動作回数を平均的に上げ、効率がよい論理検証を可能にする。

(もっと読む)

テストパターン生成方法、テストパターン生成装置、半導体集積回路故障検査方法、及び半導体集積回路故障検査装置

【課題】ATPGに係るテストパターン生成方法・装置を用いずに、自動的にテストパターンを生成するテストパターン生成・装置を提供する。

【解決手段】本発明のテストパターン生成方法は、回路情報と、回路における検出対象の故障情報とに基づいて、回路の動作を記述するプロパティを出力するプロパティ作成工程と、前記プロパティに基づいて、回路のテストパターンを出力する形式検証工程とを含む。

(もっと読む)

テスト支援装置

【課題】分岐などを多く含んでいて処理の流れが複雑なテストプログラム全体の流れを容易に理解できるテスト支援装置を提供することにある。

【解決手段】テストプログラムの仮想テストを行うように構成されたテスト支援装置において、前記テストプログラムの記述を解析するテストプログラム解析部と、このテストプログラム解析部の解析結果に基づき処理の流れについての判断を行うテストプログラム解析結果判断部と、これら各部におけるテストプログラムに関連した情報を表示するテストプログラム表示部、を有することを特徴とするもの。

(もっと読む)

ディレイ故障診断プログラム

【課題】 半導体集積回路の故障診断に関し、ディレイ故障の故障箇所を高精度に特定する。

【解決手段】 故障仮定と終点フリップフロップFF抽出部116を設け、故障仮定情報より故障仮定を選択し、故障仮定より出力側に向かって論理トレースを実行する。故障仮定からトレースの結果得られた終点のフリップフロップFFのテスト結果を判定する(117)。終点のフリップフロップFFまでの伝搬経路の最大値と最小値を求め、そこからディレイ余裕度を求める。ディレイ余裕度と117で求めたテスト結果を用いてディレイ範囲を求め(118)、故障候補とディレイ範囲決定部119で故障候補とディレイ故障のディレイ範囲を特定する。

(もっと読む)

半導体論理回路装置の故障診断方法及び故障診断プログラム

【課題】効率性を保持しつつ精確性を高くした半導体論理回路装置の故障診断方法及び故障診断プログラムを提供する。

【解決手段】半導体論理回路装置の回路情報において、X故障ゲートGiのファンアウト信号線に出現可能な故障論理値を表すX記号を挿入する。次に、テスト入力ベクトルVECを入力信号線に入力して初期シミュレーション出力ベクトルISOを出力信号線に得る。次に、X記号に2値論理シミュレーションを行ってX分解によるシミュレーション出力ベクトルを得る。次に、実際の半導体論理回路装置に対してテスト入力ベクトルVECを入力信号線に入力した際の観測出力ベクトルとシミュレーション出力ベクトルとの比較結果に応じて半導体論理回路装置の故障存在被疑領域を特定化する。

(もっと読む)

テストパターン管理装置及びテストパターン管理方法及びプログラム

【課題】効果的なシミュレーションが可能となるテストパターンを効率的に生成する。

【解決手段】初期確率設定ファイル13は、パラメタ項目ごとに各パラメタ値の比率を示しており、テストパターンジェネレータ2は、初期確率設定ファイル13のパラメタ値ごとの比率に従って複数種のテストパターンを生成し、テストベンチ4にテストパターン3を用いたシミュレーションを実行させる。結果ファイル入力部14が、シミュレーションの結果を示す結果ファイル6を入力し、実行ログ7に蓄積し、不具合履歴分析部9が実行ログ7から得られた不具合のあったテストパターンの要因を示す不具合要因履歴8を分析し、確率設定ファイルジェネレータ10が不具合の発生頻度の高いパラメタ値の比率を高くして新たな確率設定ファイル1を生成し、テストパターンジェネレータ2が、確率設定ファイル1に従って新たなテストパターン3を生成する。

(もっと読む)

回路設計支援プログラムおよび回路設計支援装置

【課題】スキャンテスト時において、製品を動作させるときに、その経路に故障が発生するか否かを検証すること。

【解決手段】回路設計支援装置1は、回路設計支援プログラムにより、第1の格納手段2と、第2の格納手段3と、回路配置手段4として機能する。第1の格納手段2は、複数の順序回路を備える回路設計情報(例えば、ネットリスト)を格納する。第2の格納手段3は、回路設計情報の、故障検出用のクロック(スキャンクロック)を挿入することによりタイミング制約違反となる条件を有する順序回路間の情報を格納する。回路配置手段4は、回路設計情報の第2の格納手段3により格納された情報の順序回路間に、この順序回路間の先端の順序回路に入力される信号と、この先端の順序回路が出力する信号の論理が変化しない場合のみ、先端の順序回路の出力信号を後段の順序回路に出力する回路を仮想的に配置する。

(もっと読む)

試験装置、試験方法、および、プログラム

【課題】被試験デバイスの試験において、試験ベクタの論理パターンに対する、リーク電流等の測定値の依存性を低減する。

【解決手段】試験ベクタを順次生成するベクタ展開部と、それぞれの試験ベクタに応じた試験信号を被試験デバイスに供給した場合に測定されるべき被試験デバイスの所定の特性値について、被試験デバイスの動作をシミュレートすることで、試験ベクタ毎にシミュレート値を算出するシミュレート部と、それぞれの試験ベクタを被試験デバイスに供給したときの、被試験デバイスの所定の特性値を測定し、試験ベクタ毎に測定値を取得する測定部と、それぞれの試験ベクタについての、対応するシミュレート値および測定値の比に基づいて、被試験デバイスの良否を判定する判定部とを備える試験装置を提供する。

(もっと読む)

LSIテスタおよびテストプログラム自動作成ツール並びにテストシステム

【課題】LSIテスタを用いたテストプログラムのデバッグにおいて、オペレータの負担を軽減するとともにデバッグ前に行う準備に要する時間を短縮できるようにする。

【解決手段】テストプログラム自動作成ツール(10)に、テストに応じて使用するピンのグループ(設定ピングループ)をピンラインナップと対応させて定義する機能を持たせ、テスタ(20)にはテストプログラムの実行時にデバッグ中のテストに合わせたピンラインナップを自動的に選択する機能(23,24)を持たせるようにした。

(もっと読む)

1 - 20 / 71

[ Back to top ]