Fターム[2G132AK17]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 試験モードへの切替回路 (419) | シフトレジスタを用いるもの (30)

Fターム[2G132AK17]に分類される特許

1 - 20 / 30

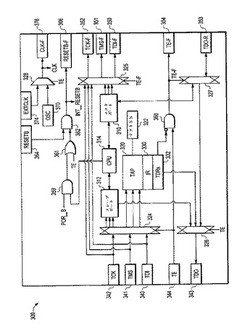

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

検査システム及びそれを用いた半導体装置並びに検査方法

【課題】 回路面積の増大が少なくコスト増を抑えることが可能な検査システムの提供。

【解決手段】 検査回路3は、第1の回路1と第2の回路2の間に介在する。また、検査回路3は、信号伝達制御機能4と検査出力機能5とを含んでいる。信号伝達制御機能4は、第1の回路1と第2の回路2の間の信号伝達を制御する。また、検査出力機能5は、検査回路3を介し、第1の回路1の出力を検査用に出力する。本発明では、信号伝達制御機能4と検査出力機能5は、互いの機能を実現する回路の一部を共有している。また、第1の回路1と第2の回路2と検査回路3は、同一の基板上に設けられている。検査回路3は信号伝達制御機能4と検査出力機能5とを切り替えて使用する。

(もっと読む)

半導体集積回路、試験方法、情報処理装置、及びプログラム

【課題】テストパターンに対する出力応答に適用されるマスク情報の反転回数を削減すること。

【解決手段】半導体集積回路は、テストパターンが入力される複数のシフトレジスタと、前記テストパターンに応じた前記複数のシフトレジスタの出力応答に対するマスク情報として適用される擬似乱数を生成する生成部と、第一の制御信号の入力に応じ、該第一の制御信号が示す前記シフトレジスタに関して前記マスク情報を反転させる反転部と、前記擬似乱数の初期値を記憶する記憶部とを有し、前記生成部が生成する前記擬似乱数は、第二の制御信号の入力に応じて前記記憶部が記憶する前記初期値によって初期化される。

(もっと読む)

半導体集積回路、および被検査回路の検査方法

【課題】BIST回路を有する半導体集積回路において、長時間を要することなく、被検査回路に対して複数回検査を実行し、かつ、各回の検査結果を個別に認識可能にする。

【解決手段】例えばメモリマクロ1のような被検査回路の検査結果を、複数個記憶可能に構成された検査結果格納回路8が設けられている。検査結果格納回路8はBIST制御回路7から出力された信号BIST_GO,BIST_DONEを入力とし、モード切替信号BIST_MODEが検査モードを示すときは、信号BIST_GOが示す検査結果を信号BIST_DONEが検査終了を示す毎に格納する。そして、モード切替信号BIST_MODEが結果読み出しモードを示すときは、検査結果格納回路8は格納している検査結果を出力する。

(もっと読む)

検査装置、および集積回路

【課題】簡易な構成により、検査対象装置のシリアルインターフェースの検査を容易化する。

【解決手段】検査装置10は、第一ビット長のパラレル信号をシリアル信号に変換し、該シリアル信号を外部に出力するDUT(検査対象装置)20を検査するものであって、DUT20は、検査の際、後述する排他的論理和の各値から成るパターンが、第二ビット長を有する所定パターンとなるように構成されている検査用データを、シリアル信号に変換するものであり、検査用データが変換されたシリアル信号をDUT20から受信する信号受信部11と、該受信したシリアル信号を、任意のビット位置から順次、第二ビット長のパラレル信号に変換するシリアルパラレル変換部12と、整数個連続して変換された第二ビット長のパラレル信号のそれぞれにおける、同一ビット位置のビット値の排他的論理和を、全てのビット位置について算出する演算部14とを備える。

(もっと読む)

半導体集積回路

【課題】遅延故障を適切に検出すること。

【解決手段】半導体集積回路は、当該半導体集積回路の被検査箇所への入力側の信号と出力側の信号とを入力とする排他論理和回路と、前記排他論理和回路の出力信号とクロック信号とを入力とする第一のマルチプレクサと、前記第一のマルチプレクサの出力信号に同期させて入力信号が示す値を記憶し、記憶している値を出力するフリップフロップとを含む検査用回路を有する。

(もっと読む)

半導体装置

【課題】誤エントリを防止できるテストモードエントリ回路を備えた半導体装置を提供する。

【解決手段】テストモードエントリ回路100は、nビットシフトレジスタ101、制御回路102及びテストモード信号発生回路103を備える。端子TCODEENTには、nビットのテストコードがシリアル入力され、nビットシフトレジスタ101は、端子TCLKに入力される周期パルスに同期してシフト動作し、テストコードを取り込む。制御回路102は、mビットカウンタ11が、カウントするカウント値がnに至ると、制御信号CNTTを出力し、シフト動作を停止させ、制御信号COMPを出力し、テストモード信号発生回路103から、テストモード信号TM0〜TMn−1を出力させる。

(もっと読む)

半導体記憶装置

【課題】 閾値電圧が負電位でも、正電位と同様のテスト方法による特性評価を実現する半導体記憶装置を提供する。

【解決手段】 本発明の半導体記憶装置は、データを記憶する複数のメモリセルを有し、テスト信号の入力により、通常モードから、メモリセルの特性評価を行うテストモードに遷移し、メモリセルを選択するメモリセル選択部と、基準電圧を発生する定電圧部と、基準電流を発生する定電流部と、X選択信号又は外部端子から入力される電圧信号のいずれかをメモリセルのゲートに供給するYスイッチ電圧切替制御回路と、Y選択信号により選択されるメモリセルのドレインに対し、リファレンス電流を供給するYスイッチ部と、ドレインの電圧であるドレイン電圧が基準電圧を超えたか否かを検出するコンパレータと、テストモードにて、制御信号により基準電流の電流値及び基準電圧の電圧値を調整し、コンパレータの判定レベルを変更する判定レベル変更部とを有する。

(もっと読む)

並列アクセスおよび直列アクセスを伴う、システムオンチップをテストするための方法ならびに装置

本発明は、チップレベルのJTAGテストに新しいハードウェア記述言語を提供する。新しいBSDL(NSDL)と呼ばれる、この新しいハードウェア記述言語は、システムオンチップのテストリソースが記述されることを可能にし、それによって、システムオンチップのテストを円滑にするように、システムオンチップが記述されることを可能にする。本発明は、システムオンチップを記述するためのボトムアップ手法を提供する。本発明は、システムオンチップの構成要素のそれぞれのアルゴリズム記述をサポートし、かつシステムオンチップの構成要素同士の間の相互接続のアリゴリズム記述をサポートし、それによって、システムオンチップ全体のアルゴリズム記述またはシステムオンチップの一部のアルゴリズム記述の生成を可能にする。本発明は、テストに関して並列アクセスを記述および使用するための方法を含めて、1つまたは複数のシステムオンチップデバイスに対する並列アクセスをサポートする。  (もっと読む)

(もっと読む)

信号品質測定装置、半導体集積回路、データ保持回路、信号品質測定方法およびプログラム

【課題】高速インタフェースの受信部における信号品質を高い精度で評価する。

【解決手段】シフトレジスタ群101は、m段のレジスタを直列に接続したシフトレジスタのデータ入力端子を互いに接続したn個のシフトレジスタから構成される。多相クロック生成回路300は、1周期の位相がn相に分割されたクロック信号を生成してシフトレジスタ毎に互いに異なる位相のクロック信号を供給する。データ入力端子611は、テスタ700から測定対象データを入力する。測定制御回路630は、多相クロック生成回路300から供給されたクロック信号に従ってシフトレジスタ群101に保持された測定対象データを取得し、シフトレジスタ群101を構成するn個のシフトレジスタの各段における測定対象データのトグル位置を検出し、この検出された各段におけるトグル位置に基づいてデータ位相品質を測定する。

(もっと読む)

半導体装置および検査方法

【課題】外形寸法を拡大することなく、対向する二面に外部電極を有する半導体集積回路の検査を行うことが可能な半導体装置を提供する。

【解決手段】一方の面1bに設けられた外部電極8はインターポーザ基板3の表面および内部に設けられた配線10により半導体チップ2に電気的に接続されている。他方の面1aには、半導体チップ2にインターポーザ基板3の表面および内部に設けられた配線により電気的に接続された外部電極4が設けられている。インターポーザ基板3の表面および内部に設けられた配線の一端が、半導体チップ2と電気的に接続され、他端が分岐され、一方の面1aに設けられた外部電極5aと他の面1bに設けられた外部電極5bに電気的に接続されている。これにより、一方の面1aに設けられた外部電極5aおよび外部電極8と検査装置とを電気的に接続することで検査することが可能となる。

(もっと読む)

半導体装置および半導体装置モジュール

【課題】半導体装置間の内部結線の接続状態をより高精度に試験することが可能な半導体モジュールおよび半導体装置を提供すること。

【解決手段】試験対象となる配線の一端側にテスト端子TTを接続するスイッチSW11ないしSW13と、試験対象となる配線の他端側に接地電位VSSを与えるトランジスタM21ないしM23とを備える。よって、試験対象の配線の一端に電源電位VDDを与え、試験対象の配線の他端に接地電位VSSを与えることで、試験対象の配線を含む電流経路を形成することができるため、オープン故障を検出することができる。また、試験対象の配線に電源電位VDDを与え、試験対象外の配線に接地電位VSSを与えれば、試験対象の配線とそれ以外の配線との間における電位差を発生させることができるため、ショート故障を検出することができる。

(もっと読む)

半導体装置

【課題】テスト中に所望の位相に対して追随できるテスト回路を備え、安価にDDRifのテストを行うことを目的としている。

【解決手段】本発明における半導体装置は、位相シフト量を決定するDLL200と、テストモード時に所定位相ずらす演算回路300と、位相シフト量を設定するレジスタ11〜16と、設定した位相にシフトして信号の送受信を行う伝送回路10とを備える。伝送回路10は、第1の信号を設定した位相にシフトする位相シフタ1と、テストモード時に第1の信号をループバックする双方向バッファ21と、双方向バッファ21から出力された信号の位相をシフトする位相シフタ2と、第3の信号の位相をシフトする位相シフタ3と、テストモード時に第3の信号をループバックする双方向バッファ22と、双方向バッファ22から出力された信号の位相をシフトする位相シフタ4と、位相シフタ2,4の出力信号を取り出すFIFO30とを備える。

(もっと読む)

メモリリード回路、それを用いたメモリ装置

【課題】メモリの検査時間を短縮する。

【解決手段】リード回路100は、マトリクス状に配置されたメモリセルの列ごとに設けられたビットラインBL1〜BLkからk個(kは自然数)のデータを読み出し、シリアルデータDSとして出力する。センスアンプSA1〜SAkは、k本のビットラインBL1〜BLkごとに設けられ、各ビットラインからデータを読み出す。シフトレジスタ30は、各センスアンプSAの出力を保持するカスケード接続されたk個のフリップフロップFF1〜FFkを含み、各センスアンプSAの出力をロードする。期待値設定部32は、k個のフリップフロップFF1〜FFkに、対応するセンスアンプSA1〜SAkの出力の期待値データを格納する。判定部36は、各フリップフロップFF1〜FFkに格納される期待値データと、対応するセンスアンプSA1〜SAkの出力との一致、不一致を判定する。

(もっと読む)

テスト回路

【課題】テスト時間を減少することができ、従って、テストコストを削減することができるテスト回路を提供する。

【解決手段】アドレス生成回路105は、外部クロック115に同期して、テストアドレス107を生成し、これをROMアドレス104として、ROM101に供給する。MISR112は、入力されたROMアドレスに104に対応してROM101から出力された出力ROMデータ106を圧縮する。4ビットシフトレジスタ114は、圧縮したデータ(MISR出力113)を4データ分まとめて出力する。

(もっと読む)

半導体装置、半導体集積回路およびバンプ抵抗測定方法

【課題】チップ間を接続するインターナルバンプの接続抵抗を容易に、精度よく、かつ、低コストで測定する。

【解決手段】メインチップ2と、メインバンプ(Ba,Bb,…)と測定・制御入力バンプ(B1〜B4)とによりメインチップ2と接続されるサブチップ3と、を備え、上記2つのチップのそれぞれに、メインバンプごとの複数の電圧経路スイッチ(T12a,T12b,…あるいはT13a,T13b,…)と、メインバンプと測定経路スイッチの各接続点(Na2,Nb2,…またはNa3,Nb3,…)に接続されている複数の電流経路スイッチ(T22a,T22b,…あるいはT23a,T23b,…)と、制御回路(シフトレジスタ42または43)と、を有し、メインチップ2は、更に、制御入力、電定電流供給および電圧測定のための複数の測定・制御端子(Ta〜Tf)を有する。

(もっと読む)

半導体集積回路装置

【課題】故障位置解析回路を設けることによる大型化を防止した半導体集積回路装置を提供する。

【解決手段】記憶部RM1〜RMnに対して1対1で対応するように設けられたスキャンパス回路SC1〜SCnと、スキャンパス回路SC1〜SCnから出力されるシリアルデータSO1〜SOnを受けてOR演算を行うOR回路OR1と、OR演算出力を受ける故障位置解析回路ENCとを備え、故障位置解析回路ENCにおいて、OR演算出力に基づいて、故障位置情報FAIL_POSIやフェイルフラグFAIL_FLAGが出力される。

(もっと読む)

アナログ−デジタル変換器の出力検査方法及び集積回路装置

【課題】 nビットのデジタル信号がアナログ変換されたアナログ電圧を出力パッドに出力させながら、高精度な電圧測定器を用いずに短時間で検査することができるデジタル−アナログ(DA)変換器の出力検査方法及びその検査回路を内蔵した集積回路を提供すること。

【解決手段】 集積回路装置は、nビットデータをパラレルで出力するデータ生成部と、その生成部からパラレルで出力されるnビットデータをアナログ電圧に変換するDA変換器と、データ生成部からのnビットデータを、検査時に入力されるクロック信号に基づいてパラレル−シリアル変換して、n個の1ビットデータをシリアル出力するパラレル−シリアル変換器と、検査時には、パラレル−シリアル変換器よりシリアルで出力されるn個の1ビットデータの各論理レベルに基づいて、DA変換器に入力されるnビットデータを、n回の各回にて2種類のnビットデータのいずれか一方に調整する回路とを有する。

(もっと読む)

検査システムおよびその検査回路、半導体装置、表示装置ならびに半導体装置の検査方法

【課題】 回路面積の増大が少なくコスト増を抑えることが可能な検査システムの提供。

【解決手段】 検査回路3は、第1の回路1と第2の回路2の間に介在する。また、検査回路3は、信号伝達制御機能4と検査出力機能5とを含んでいる。信号伝達制御機能4は、第1の回路1と第2の回路2の間の信号伝達を制御する。また、検査出力機能5は、検査回路3を介し、第1の回路1の出力を検査用に出力する。本発明では、信号伝達制御機能4と検査出力機能5は、互いの機能を実現する回路の一部を共有している。また、第1の回路1と第2の回路2と検査回路3は、同一の基板上に設けられている。検査回路3は信号伝達制御機能4と検査出力機能5とを切り替えて使用する。

(もっと読む)

1 - 20 / 30

[ Back to top ]