Fターム[2G132AK18]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 試験モードへの切替回路 (419) | カウンタを用いるもの (28)

Fターム[2G132AK18]に分類される特許

1 - 20 / 28

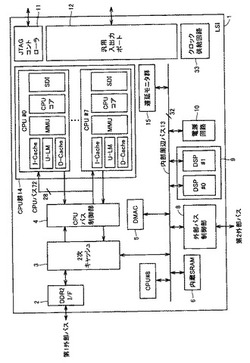

半導体集積回路

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

半導体集積回路およびその試験方法

【課題】 半導体試験装置を利用して、短い所要時間でD級増幅器の出力パルスの周波数に関する判定を行うことが可能な半導体集積回路を提供する。

【解決手段】 半導体集積回路1は、D級増幅器100と、セレクタ140と、カウンタ150とを有する。カウンタ150は、セレクタ140によって選択された出力信号OUTPまたはOUTMをモニタ対象パルスとし、リセット信号RSTの解除後、所定個数のモニタ対象パルスをカウントしたときに出力端子からカウント終了信号COを出力する。従って、リセット信号RSTの解除から所定時間経過した後の所定期間内にカウント終了信号COが出力されるか否かを判定することにより、D級増幅器100の出力信号の周波数が適正範囲内にあるか否かを判定することができる。

(もっと読む)

モニタリング装置及びモニタリングシステム

【課題】LSI等の不具合発生時の原因追求を容易化する。

【解決手段】LSI内又はLSIの近傍にモニタリング装置100を配置し、モニタリング装置100内で、周波数カウンタ20が、一定時間でのリングオシレータ10の発振周波数を計測し、計測した発振周波数を示す発振周波数情報を生成し、時刻カウンタ30が、周波数カウンタ20により発振周波数が計測された時刻を示す時刻情報を生成し、出力制御部80が、発振周波数情報と時刻情報とを対応付けて記憶装置90に出力し、記憶装置90が、発振周波数情報と時刻情報をログとして記憶する。これにより、LSIが起動してから不具合発生までの間の発振周波数の推移を観測することで遅延の相対的な変化を確認することができ、LSIの個体差を気にする必要がなく、不具合発生時の原因追求を容易化できる。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

オンチップジッタデータ取得回路、ジッタ測定装置、及びその方法

【課題】本発明は、高周波プローブを要さずにジッタ測定が可能なオンチップジッタデータ取得回路を提供することを目的とする。

【解決手段】本発明に係るオンチップジッタデータ取得回路1は、クロック信号を、遅延量選択信号で選択可能な複数の遅延量のいずれか1つの遅延量で遅延する可変遅延部10と、クロック信号の位相と、可変遅延部で遅延されたクロック信号の位相とを比較して、位相比較信号を生成する位相比較信号生成部20と、位相比較信号を所定の期間に亘り取得する位相比較信号取得部30と、を有することを特徴とする。

(もっと読む)

半導体集積デバイスのテスト回路、テスト方法及びプログラム

【課題】複数のI/Oバッファ間における相対的な差を測定し、I/Oバッファの複数信号の相対的な差が許容範囲にあれば正常な半導体集積デバイスと判定し、いままでは不良のデバイスであると判定されていたものを救済する。

【解決手段】半導体集積デバイスにおいて、ドライバ、複数のレシーバ、インバータによって発振回路を構成し、この発振回路の出力をクロック入力とする2個以上のカウンタと、カウント値を比較するコンパレータの比較結果により半導体集積デバイスの良否を判定する。

(もっと読む)

半導体集積回路装置

【課題】特定のモニタ回路が動作不良であったり、モニタ回路内のリングオシレータを構成する一部の素子の特性に異常があったりした場合、最も動作速度の遅いモニタの結果に基づいて電圧制御をおこなうと、必要電圧を過大に見積もる恐れがある。その結果、消費電力の増加を招き、また、複数モニタの検出結果の平均値をとる際にも精度が低下する。

【解決手段】複数のモニタ回路を設け、それらの検出結果の内、所定の範囲から外れたものについては検出結果を無視して残りのモニタ結果の平均値を最終的なモニタ検出値とする。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】実際の動作条件下においてエレクトロマイグレーションの劣化現象を検知すると共に、故障の兆候を検知することが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路10は、カウンタ回路6と、遅延クロック信号56を生成する遅延素子5と、クロック信号52のクロックサイクル毎にトグルするデータを入力する第1のフリップフロップ1と、第1のフリップフロップ1からの出力信号を入力する配線4と、遅延クロック信号56に基づき駆動し、配線4からの出力信号を入力する第2のフリップフロップ2と、クロック信号52に基づき駆動し、第1のフリップフロップ1からの出力信号を入力する第3のフリップフロップ3と、第2及び第3のフリップフロップ2、3からの出力信号の排他的論理和を出力する排他的論理和回路7と、を有する。

(もっと読む)

半導体集積回路

【課題】内部回路の入力ピンをそれより少ない半導体集積回路の外部ピンにマッピングし、かつ製造後の個々のチップの動作を検証するための試験を実動作速度で行うことができるようにする。

【解決手段】試験対象回路を動作させるクロックの供給・停止を制御するクロック制御部と、シリアル入力される試験パターンデータから試験対象回路に対してパラレルに供給する試験パターンを生成する信号発生部と、生成された試験パターンを蓄積する蓄積部とを有し、蓄積される試験パターンが所定のサイクル数分に達すると、クロック及び試験パターンを試験対象回路に供給するようにして、試験対象回路の入力ピンより少ない半導体集積回路の外部ピンを用いて、試験対象回路に試験パターンを供給し、試験対象回路を実動作速度で動作させ動作の検証を行えるようにする。

(もっと読む)

タイマーを内蔵した多機能半導体集積回路

【課題】専用のテスト用端子を設ける必要がないとともに、テストモードへ入るため所定の端子に電圧を印加してしたことにより並行して他のテストができなくなってテスト時間が長くなったりするのを回避できる半導体集積回路のテスト技術を提供する。

【解決手段】複数の機能ブロック(11〜15)が搭載され、前記複数の機能ブロックのいずれかにタイマー回路(20)が内蔵されている多機能半導体集積回路において、前記タイマー回路を内蔵した機能ブロック(13)以外の機能ブロックに対応して設けられている外部端子であって、通常動作状態では電源電圧よりも小さい範囲の電圧が印加される外部端子(OV,FB)に、通常動作状態では印加されないレベルの電圧が印加されると前記タイマー回路を検査するためのテストモードが設定されるように構成した。

(もっと読む)

半導体集積回路装置、半導体集積回路装置のテスト方法、バーインストレス&D/Sに用いられるプローブカード

【課題】最適なバーインストレスをサンプルに印加する。

【解決手段】半導体集積回路装置50には、バーインカウンタ1、制御部2、及び被テスト回路3が設けられる。バーインカウンタ1は、半導体記憶装置としての被テスト回路部3に印加されるバーインストレスを把握するために設けられたものである。バーインカウンタ1は、被テスト回路3に印加されるバーインストレス(印加温度及び印加電圧)を把握し、バーインストレスをカウントアップ(モニター)して、印加温度、印加電圧、及びバーインストレス時間に対応したバーインストレス情報を外部に出力する。

(もっと読む)

集積回路装置

【課題】バーンイン試験の動作を外部クロックに基づく動作切り替えるために、外部から入力される制御信号やその入力のための専用の端子を必要としない。

【解決手段】外部クロックCLK1と内蔵発振回路3で生成される内部クロックCLK2とをクロック選択回路4で動作クロックCLKとして選択する。バーンインモードテストパターン作成回路は、動作クロックCLKに同期してテストパターンを作成する。Dフリップフロップ7は、電源投入時のリセットにより外部クロックCLK1を選択するようにクロック選択回路4を制御する。また、カウンタ8は、電源投入時のリセットから内部クロックCLK2の所定のクロック数をカウントすることで所定時間を計測する。Dフリップフロップ5は、所定時間内に外部クロックCLK1の入力入力があると判定すると、外部クロックCLK1の選択を維持するようにクロック選択回路4を制御する。

(もっと読む)

標準セルライブラリーの性能改善のための測定装置

【課題】TEGを通した標準セルライブラリーの性能を測定して検証するにおいて、内蔵された回路を使用することで、標準セルの性能を効果的に改善するための測定装置を提供する。

【解決手段】外部から入力されるイネーブル信号によって活性化され、測定結果値を出力するリングオシレータブロックと;前記各リングオシレータブロックから出力される測定結果値のうち一つまたはそれ以上を選択的に出力するデコーダーと;前記デコーダーの出力を定められた区間の間に受けて、その入力値の最大値と最小値との平均を出力するスタティスティックスアシスタと;を含んで標準セルライブラリーの性能改善のための測定装置を構成する。

(もっと読む)

半導体装置

【課題】簡単で効率的にAC特性評価が可能な半導体装置を提供する。

【解決手段】搭載される内部回路を構成するMOSFETと同一の製造工程で形成されたMOSFET素子を用いて構成されたリングオシレータと外部端子から供給されるタイミング信号により上記リングオシレータの発振信号を計数の開始と停止を行う周波数カウンタを形成する。評価時に出力回路により上記周波数カウンタの計数出力をさせる。制御判定回路を設けて、上記周波数カウンタの制御と、その計数出力が許容値内にあるか判定して判定結果を出力させる。上記タイミング信号として、複数のリングオシレータのそれぞれに対応して上記周波数カウンタの計数値が最大計数値内に収まるように異なる時間に設定する。

(もっと読む)

電子機器

【課題】予期しない入力信号の組合せやタイミングで異常な動作が起こる電子機器の動作確認試験の効率を向上させることのできる電子機器を提供する。

【解決手段】所定の入力信号に基づいて予め設定された処理を実行する複数の信号処理ブロックが組み込まれた集積回路1により制御される電子機器であって、前記入力信号に外乱を付与する外乱生成部5を前記集積回路1に備え、前記外乱発生部5に前記入力信号を所定範囲内でランダムに遅延させる遅延回路51,52,53,64,55,56を備えている。

(もっと読む)

半導体集積回路およびそのテスト方法

【課題】半導体集積回路に内蔵された送受信の通信機能のテストコストの低減を可能とすること。

【解決手段】半導体集積回路100は、受信システム4…12と、送信システム13…16と、RFテスト信号供給回路18とを含む。RFテスト信号供給回路18は、送信システムからのRF送信出力信号を受信システムが処理可能な周波数帯域のRFテスト信号に変換して、受信システムに供給する。半導体集積回路100は通常動作モードに設定されることにより、受信システムと送信システムとは送受信動作を行う。半導体集積回路100は通常動作モードと異なる他の動作モードに設定されることにより、RFテスト信号供給回路18は変換したRFテスト信号を受信システムに供給する。テストで、受信システムでの受信信号が正常であれば、半導体集積回路100の受信システムと送信システムとは正常と判断される。

(もっと読む)

テスト回路

【課題】半導体集積回路装置のテスト時のテスト端子を抑制する。

【解決手段】テスト回路30には、エッジ検出回路1、エッジ検出回路2、2入力Ex−OR回路EX1、リセット機能付きフリップフロップFF1乃至FF3、端子Pad1、及び端子Pad2が設けられている。テスト回路30は8ピンマイコンの出荷テストなどを行うときに使用され、テスト端子である端子Pad1から入力されるテストクロック信号TCLKにもとづいて、2入力Ex−OR回路EX1から“High”レベルの信号であるテストイネーブル信号Test Enableが出力される。この信号により半導体集積回路装置をテストモードに移行することができる。

(もっと読む)

半導体集積回路

【課題】短パルス幅のデータ入力信号を入力する半導体集積回路内の入力回路の試験を行うことができる半導体集積回路を提供することを課題とする。

【解決手段】外部からのデータ入力信号を入力して出力するデータ入力回路(111)と、前記データ入力回路への入力に応じて変化する出力信号の期待値を記憶する比較値レジスタ(116)と、前記データ入力回路の出力信号の切り替わり回数に応じた値と期待値とを比較する比較回路(113)とを有することを特徴とする半導体集積回路が提供される。

(もっと読む)

半導体集積回路、マイクロコンピュータ、および、それらの動作モード切替え方法

【課題】従来の動作モードの設定においては、製品の出荷前と出荷後で動作モードの設定条件を変更することができなかった。

【解決手段】本発明の半導体集積回路は、書換え可能な不揮発性メモリと、動作モード設定信号が入力される動作モード設定端子と、動作モード設定信号に基づいてカウント動作を行う第1のカウンタと、を備え、不揮発性メモリは、第1のパルス数設定値を格納し、第1のカウンタのカウント値と第1のパルス数設定値が一致した場合に動作モードの切替えを実行することを特徴とする。

(もっと読む)

1 - 20 / 28

[ Back to top ]