Fターム[2G132AK21]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 試験モードへの切替回路 (419) | 遅延回路を用いるもの (42)

Fターム[2G132AK21]に分類される特許

1 - 20 / 42

半導体装置

【課題】複数箇所のタイミング違反検出を、小規模な回路構成で実現する。

【解決手段】選択信号に基づいて、複数の信号からいずれか1つを選択する第1のセレクタと、上記選択信号に基づいて、ラッチされた複数の信号からいずれか1つを選択する第2のセレクタと、クロック信号CLKを所定時間遅延する遅延回路と、遅延回路により遅延したクロック信号に同期して、第1のセレクタの出力をラッチするタイミング違反検出用フリップフロップ回路と、タイミング違反検出用フリップフロップ回路の出力と第2のセレクタの出力とを比較する比較回路とを、備える。複数の信号に対し、個別に回路を設けることなく、1つのタイミング違反検出回路で構成することができる。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

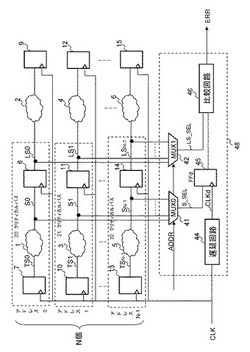

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

半導体集積回路及び半導体集積回路のテスト方法

【課題】内部に備えられた順序回路の動作検証にかかる時間を短縮できる半導体集積回路を提供すること

【解決手段】半導体集積回路1は、入力信号3が論理回路4を通過した信号である通過信号が供給されるD型F/F10を備える。遅延量測定回路6は、論理回路4により生じる入力信号3の遅延量を、D型F/F10の動作検証前に測定する。遅延制御回路5は、D型F/F10の動作検証の際に、入力信号3を遅延量測定回路6が測定した遅延量だけ遅延させた遅延信号を生成する。比較回路11は、D型F/F10の動作検証の際に、遅延制御回路5が生成した遅延信号をD型F/F10の入力とした場合のD型F/F10からの出力と、期待値と、を比較してD型F/F10の動作検証を行う。

(もっと読む)

TDC装置とTDCのキャリブレーション方法

【課題】遅延素子の遅延時間のばらつきに対してTDCの変換特性を一定とし線形性を実現可能なTDCの提供。

【解決手段】第1の信号DATAを順次遅延させる複数段の遅延素子111〜11Nを有するディレイライン10と、第2の信号CLKに応答して複数段の遅延素子の出力をサンプルする複数のフリップフロップ121〜12Nと、相隣るフリップフロップの出力結果が切り替わるエッジ位置を、第1の信号の第2の信号に対する位相差として検出するエッジ検出器13と、を備え、エッジ位置の検出結果に基づき、バイアス制御用の制御コードICNTを生成するキャリブレーション制御回路15と、制御コードに対応する複数段の遅延素子に対して供給するバイアス発生回路14を備え、第1の信号の周波数範囲に対応した段数の遅延素子に、第1の信号のエッジが位置するように遅延素子111〜11Nの遅延時間の校正を行う。

(もっと読む)

半導体装置の試験方法

【課題】 測定装置の入出力ピンの使用率を高め、同時に測定試験を行える被測定デバイスの数を増加させる。

【解決手段】 測定装置が備える複数の入出力ピンを予め設定された本数よりも多い所定本数ずつ複数の半導体装置にそれぞれ関連付ける。複数の半導体装置にそれぞれ関連付けられた所定本数の入出力ピンのうち、予め設定された本数の入出力ピンを当該関連付けされた半導体装置に割り振られた入出力ピンであると測定装置に認識させるとともに、残りの入出力ピンを少なくとも1つの仮想デバイスに割り振られた入出力ピンであると測定装置に認識させる。測定装置に、複数の半導体装置及び仮想デバイスの測定試験をそれぞれ予め設定された本数の入出力ピンを用いて行うと見せかけた状態で、複数の半導体装置の測定試験を、それぞれの半導体装置に関連付けられた所定本数の入出力ピンを用いて同時に行う。

(もっと読む)

半導体集積デバイスのテスト回路、テスト方法及びプログラム

【課題】複数のI/Oバッファ間における相対的な差を測定し、I/Oバッファの複数信号の相対的な差が許容範囲にあれば正常な半導体集積デバイスと判定し、いままでは不良のデバイスであると判定されていたものを救済する。

【解決手段】半導体集積デバイスにおいて、ドライバ、複数のレシーバ、インバータによって発振回路を構成し、この発振回路の出力をクロック入力とする2個以上のカウンタと、カウント値を比較するコンパレータの比較結果により半導体集積デバイスの良否を判定する。

(もっと読む)

半導体装置

【課題】電源投入時において誤ってテストモードが設定されたテスト回路をリセットするテスト信号発生回路を備えた半導体装置を提供する。

【解決手段】テスト信号発生回路100は、テストイネーブル信号TESTEをLレベルからHレベルへと遷移させてテスト回路を活性化し、テストイネーブル信号TESTEをHレベルからLレベルへと遷移させてテスト回路を非活性化する。テストモードエントリ信号ENTESTBがHレベルからLレベルへ遷移すると、テストイネーブル信号TESTEをLレベルからHレベルへと遷移させ、テストイネーブル信号TESTEがHレベルへと遷移してから予め設定された所定期間経過後に、テストモードエントリ信号ENTESTBがHレベルに遷移しているとき、テストイネーブル信号TESTEをHレベルからLレベルへと遷移させる。

(もっと読む)

半導体装置および制御回路

【課題】実動作時における内部クロック信号のジッタ量を検出し、検出したジッタ量を外部で利用可能に出力できる半導体装置を得ること。

【解決手段】クロック生成回路が出力しているクロック信号と、該クロック信号を少なくとも1周期遅延した遅延クロック信号との位相差に基づき前記クロック信号に含まれるジッタ成分を検出するジッタ検出部と、前記検出されたジッタ成分を電圧信号に変換する増幅回路を有する増幅部と、前記変換された電圧信号を外部へ出力するためのジッタ出力端子とを備えたことを特徴とする。

(もっと読む)

半導体回路装置、半導体回路装置の測定方法

【課題】マイクロバンプに対応した測定用のパッドを有する半導体回路装置のアクセス時間tACの測定がより高精度に行えるようにする。

【解決手段】測定クロック生成回路200はメモリ部140の動作クロックCLK2のタイミングを変化させることで測定クロックCLK3を生成する。フリップフロップ154と排他的論理和ゲート155から成る部位は、比較結果信号XOR1として、出力データDoutの位相が測定クロックCLKに対して進んでいるときと遅れているときとで異なる値の信号を出力するように動作する。そこで、測定クロックCLK3のタイミングを変化させながら出力データDoutと測定クロックCLKの位相が一致するタイミングを特定し、アクセス時間tACを求める。

(もっと読む)

半導体集積回路装置

【課題】特定のモニタ回路が動作不良であったり、モニタ回路内のリングオシレータを構成する一部の素子の特性に異常があったりした場合、最も動作速度の遅いモニタの結果に基づいて電圧制御をおこなうと、必要電圧を過大に見積もる恐れがある。その結果、消費電力の増加を招き、また、複数モニタの検出結果の平均値をとる際にも精度が低下する。

【解決手段】複数のモニタ回路を設け、それらの検出結果の内、所定の範囲から外れたものについては検出結果を無視して残りのモニタ結果の平均値を最終的なモニタ検出値とする。

(もっと読む)

半導体集積回路

【課題】 チップ内の任意の位置のトランジスタの特性をモニタすることが可能な半導体集積回路を提供する。

【解決手段】 テスト回路13-1、13-2は、複数のトランジスタを含む機能ブロック12-1〜12-nの近傍の領域に配置され、第1のフリップフロップ回路13aと、第2のフリップフロップ回路13bと、第1、第2のフリップフロップ回路間に接続された少なくとも1つのインバータ回路21,31,41とを含んでいる。信号生成回路14は、第1のクロックパルスと第2のクロックパルスを含むクロックパルスを生成し、かつ、第1、第2のクロックパルスのパルス間隔を制御可能とされている。テスト時、第1のフリップフロップ回路は、信号生成回路の第1のクロックパルスに同期してデータを出力し、第2のフリップフロップ回路は、信号生成回路の第2のクロックパルスに同期してデータをラッチする。

(もっと読む)

故障検出回路

【課題】高精度な検証装置を用いずに、精度良く遅延故障を検出できる故障検出回路を提供する。

【解決手段】故障検出回路は、入力信号を目標遅延量に従って遅延して、検証対象信号を出力する遅延処理回路と、前記入力信号を前記検証対象信号の遅延量の最小許容量だけ遅延した第1基準信号と、前記入力信号を前記検証対象信号の前記遅延量の最大許容量だけ遅延した第2基準信号と、の少なくとも何れかを出力する基準遅延処理回路と、前記検証対象信号と、前記第1基準信号と前記第2基準信号との少なくとも何れかと、を入力し、前記遅延量が前記最小許容量より小さい場合と、前記遅延量が前記最大許容量より大きい場合とに、前記遅延処理回路が故障していることを検出する故障検出部と、を備えることを特徴とする。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】実際の動作条件下においてエレクトロマイグレーションの劣化現象を検知すると共に、故障の兆候を検知することが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路10は、カウンタ回路6と、遅延クロック信号56を生成する遅延素子5と、クロック信号52のクロックサイクル毎にトグルするデータを入力する第1のフリップフロップ1と、第1のフリップフロップ1からの出力信号を入力する配線4と、遅延クロック信号56に基づき駆動し、配線4からの出力信号を入力する第2のフリップフロップ2と、クロック信号52に基づき駆動し、第1のフリップフロップ1からの出力信号を入力する第3のフリップフロップ3と、第2及び第3のフリップフロップ2、3からの出力信号の排他的論理和を出力する排他的論理和回路7と、を有する。

(もっと読む)

半導体装置

【課題】通常動作モードとテスト動作モードの切換に使用した兼用外部端子をテスト動作モード時のモニター端子としても使用できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、通常動作モードとテスト動作モードを切り換える切換回路と、前記通常動作モード時と前記テスト動作モード時で兼用する2つ以上の兼用外部端子とを備える半導体装置であり、前記切換回路は、前記兼用外部端子にて前記半導体装置で通常使用する入出力電圧の範囲外の電圧の印加を検出する検出回路と、全ての前記兼用外部端子に同時に前記入出力電圧の範囲外の電圧の印加が検出された場合テスト開始信号を出力する論理回路と、前記テスト開始信号をラッチする記憶回路とを含み、前記テスト動作モードに切り換わった後、前記兼用外部端子の内、1つの兼用外部端子に前記入出力電圧の範囲外の電圧が印加し続けられていることでテスト動作モードが維持される。

(もっと読む)

半導体集積回路装置及び半導体集積回路装置の試験方法

【課題】試験時間を短縮することができる半導体集積回路装置を提供する。

【解決手段】試験時には、マルチプレクサ19が観測対象信号P1〜P4から第1観測対象信号を選択する選択工程と、クロック供給回路27が、フリップフロップ26に、マルチプレクサ19が出力する観測対象信号の遅延変動に対してセットアップ・ホールド制約を満たすクロックを供給するクロック供給工程と、フリップフロップ26がマルチプレクサ19から出力される観測対象信号を、クロック供給回路27から出力されるクロックに同期して取り込む取込工程と、遅延調整回路28がフリップフロップ26から出力される観測対象信号を入力して遅延調整し、その出力端において、観測対象信号P1〜P4を共通タイミングでサンプリング可能とする遅延調整工程とを実行する。

(もっと読む)

デジタル信号遅延測定回路、及びデジタル信号遅延測定方法

【課題】動的IR-Dropの影響も加味したデジタル回路の真の遅延時間を測定可能としたデジタル信号遅延測定回路、及びデジタル信号遅延測定方法の提供。

【解決手段】スキャンテスト可能な回路に対するデジタル信号の遅延時間を測定するためのデジタル信号遅延測定回路であって、遅延時間測定用信号を出力する出力手段と、遅延時間測定用信号の状態が変化するタイミングを遅延させるための遅延手段と、遅延時間測定用信号を入力し、保持指令の入力タイミングで当該遅延時間測定用信号の状態を保持する少なくとも2つ以上の信号保持手段とを備え、各前記信号保持手段に対する前記保持指令の入力タイミングは同一であり、且つ、前記各信号保持手段に入力される前記遅延時間測定用信号の状態が変化するタイミングは前記遅延手段によって互いに異なり、前記各信号保持手段において保持された前記遅延時間測定用信号の状態の違いに基づいて前記遅延時間を得る。

(もっと読む)

測定システム及び測定回路

【課題】電源電圧の変動周期に制限されることなく、電源電圧の瞬時電圧値を測定する。

【解決手段】測定回路30は、7個のインバータI1〜I7がリング状にシリアル接続されたリング型発振器と、リング型発振器のリング上に配設され、各インバータの間に配設された7個のトランスミッションゲートS1〜S7を備えている。トランスミッションゲートS1〜S7は、イネーブル信号ENが入力され、ハイレベル期間においてオンし、リング型発振器を駆動させる。そして、リング型発振器から出力される出力信号を一定期間カウントすることで、ハイレベル期間における電源電圧の値を瞬時電圧値として算出する。

(もっと読む)

信号処理回路、電子装置、および信号処理回路の試験方法

【課題】簡易な構成で、従来技術より短いノイズ除去時間の測定が可能な技術を提供する。

【解決手段】信号から所定のパルス幅以下のパルスノイズを除去すべく構成されたノイズフィルタと、ノイズフィルタの出力信号がセット端子に入力されるセットリセットフリップフロップと、セットリセットフリップフロップの出力信号が出力されるモニタ端子と、を備える信号処理回路である。

(もっと読む)

電子機器

【課題】予期しない入力信号の組合せやタイミングで異常な動作が起こる電子機器の動作確認試験の効率を向上させることのできる電子機器を提供する。

【解決手段】所定の入力信号に基づいて予め設定された処理を実行する複数の信号処理ブロックが組み込まれた集積回路1により制御される電子機器であって、前記入力信号に外乱を付与する外乱生成部5を前記集積回路1に備え、前記外乱発生部5に前記入力信号を所定範囲内でランダムに遅延させる遅延回路51,52,53,64,55,56を備えている。

(もっと読む)

1 - 20 / 42

[ Back to top ]