Fターム[2G132AL31]の内容

Fターム[2G132AL31]に分類される特許

1 - 20 / 119

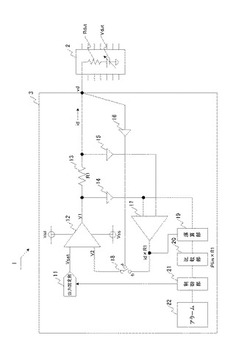

直流電流電圧源および半導体試験装置

【課題】直流の電流および電圧を発生するときに、過剰な消費電力が出力アンプに作用しないように制御することを目的とする。

【解決手段】本発明の直流電流電圧源3は、出力設定部11により設定された設定電圧Vsetを出力する出力アンプ12と、出力アンプ12が出力する出力電圧V1と出力アンプ12に帰還されて入力される入力電圧V2とを入力して、出力アンプ12の消費電力Pampを演算する演算部19と、演算部19により演算された消費電力Pampが予め設定された設定電力Plimを超過しているか否かを比較する比較部20と、消費電力Pampが設定電力Plimを超過しているときには、出力設定部11の設定値を低下させる制御を行う制御部21と、を備えている。

(もっと読む)

基板受けピン、ピンボードユニットおよび基板検査装置

【課題】コンタクトピンや検査基板に傷付きを生じさせずに検査基板を平行に支持する。

【解決手段】本体21a、取付部21bおよびフランジ部21cを有するスリーブ21と、先端部22dにスプリング23を係合可能に形成されると共に他端部にヘッド22cが配設された本体22aを有するプランジャ22と、スプリング23とを備え、スリーブ21は、外径がフランジ部21cの外径以下の筒状に形成されて本体22aを挿通可能にフランジ部21cに配設された摺動量制限部21dを備え、制限部21dは、ヘッド22c上に検査基板8が載置されていない常態において、ヘッド22cにおけるスリーブ21側の端面と、制限部21dにおけるフランジ部21c側とは反対側の端面とが、弾性限度まで伸ばしたスプリング23の長さから常態におけるスプリング23の長さL1を差し引いた第1の長さよりも短い長さL1sだけ離間するように長さL4が規定されている。

(もっと読む)

試験装置

【課題】誘導負荷部に蓄積されたエネルギーが放出されたかを検出する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスに供給する電源電圧を発生する電源部と、電源部と被試験デバイスとの間の経路上に設けられた誘導負荷部と、誘導負荷部を少なくとも含む基板を収容する収容部と、基板における予め定められた箇所の電圧が設定電圧よりも大きい場合、収容部内の基板にオペレータをアクセスさせるための開閉部のロック状態を維持するロック維持部と、を備える試験装置を提供する。

(もっと読む)

試験装置

【課題】被試験デバイスへ過剰な電流が流入することを防ぐ。

【解決手段】被試験デバイスを試験する試験装置であって、前記被試験デバイスに供給する電源電圧を発生する電源部と、前記電源部から前記被試験デバイスに至る経路上に設けられた誘導負荷部と、前記誘導負荷部に対して前記被試験デバイスと並列に接続された第1半導体スイッチと、前記被試験デバイスに対する電源電圧の供給を遮断する場合に、前記第1半導体スイッチをオンとする制御部とを備える試験装置を提供する。

(もっと読む)

試験装置

【課題】試験の異常時において被試験デバイスへの電源供給を高速に遮断する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスに供給する電源電圧を発生する電源部と、電源部と被試験デバイスとの間の経路上に設けられた誘導負荷部と、誘導負荷部と被試験デバイスとの間の経路上に直列に接続された複数の半導体スイッチと、被試験デバイスへの電圧の供給を遮断する場合において、複数の半導体スイッチをオフとする制御部と、を備える試験装置を提供する。

(もっと読む)

タイミング信号生成装置及び半導体試験装置

【課題】エッジ信号の発生エラーの原因を短時間且つ容易に解析することができるタイミング信号生成装置、及び当該装置を備える半導体試験装置を提供する。

【解決手段】タイミング信号生成装置1は、生成すべきタイミング信号TSのエッジの位置を規定するエッジ信号EG1,EG2を規定する複数のタイミングデータを記憶する記憶部11と、生成すべきタイミング信号TSに応じて記憶部11から読み出されたタイミングデータの入れ替えを行う入替部12と、入替部12から出力されるタイミングデータに基づいてエッジ信号EG1,EG2を生成するエッジ信号生成部15と、エッジ信号生成部15で生成されるエッジ信号EG1,EG2の発生エラーを検出する検出部16と、検出部16の検出結果を入替部12の入れ替え規則に応じて変換する変換部18とを備える。

(もっと読む)

半導体試験装置および半導体試験装置における静電気保護方法

【課題】静電気耐量を高めた半導体試験装置を提供する。

【解決手段】測定対象デバイスに電気信号を出力する1または複数個の信号出力部と、信号出力部に対応して設けられ、信号出力部と測定対象デバイスとの間の電気的接続のオンオフを切り替える半導体リレーと、測定対象デバイスとの直接的あるいは間接的な接続の前に、半導体リレーをオンにする制御部とを備えた半導体試験装置。測定対象デバイスとの直接的あるいは間接的な接続の前に、さらに、信号出力部から0Vの電圧を出力させるようにしてもよい。

(もっと読む)

異常通知システムおよび半導体試験装置

【課題】異常検出回路が異常を検出したときに迅速且つ確実に異常処理を行うことを目的とする。

【解決手段】複数の下位モジュール4とこれらの下位モジュール4の制御を行う上位モジュール3との間をバス2により接続した異常通知システム1は、下位モジュール4から上位モジュール3に割込み信号を出力するシリアル伝送経路5と、下位モジュール4に備えられ、複数の異常検出回路20が異常を検出したことを示す異常情報に下位モジュール4を特定するモジュール特定情報を付加した複数ビットの出力情報をパラレルデータからシリアルデータに変換してシリアル伝送経路5に出力するパラレルシリアル変換部24と、上位モジュール3に備えられ、シリアル伝送経路5から入力した出力情報をシリアルデータからパラレルデータに変換して異常情報およびモジュール特定情報を得るシリアルパラレル変換部12と、を備える。

(もっと読む)

半導体試験装置

【課題】テストプログラムの記述が誤っている場合でも、DUT100を破壊や損傷から保護することができる半導体試験装置を実現する。

【解決手段】被試験対象デバイスに電圧または電流を印加して試験を行う半導体試験装置において、被試験対象デバイスを試験する試験内容が記述されたテストプログラムと被試験対象デバイスに印加できる電圧または電流の許容範囲が記述されたシステム特性記述ファイルとを記憶する記憶部と、テストプログラムとシステム特性記述ファイルとを記憶部から取得し、テストプログラム実行時に許容範囲に基づいてテストプログラムの設定をチェックし、設定が許容範囲を超えていた場合にユーザにエラーを通知するテスタ制御部と

を備える。

(もっと読む)

試験装置及び試験方法

【課題】 試験装置及び試験方法に関し、簡単な機構により特定のプローブピンに大電流が流れることを回避する。

【解決手段】 テスターヘッドと、テスターヘッドと電気的に接続されるパファーマンスボードと、パフォーマンスボードと電気的に接続されるフロックリングと、フロックリングに電気的に接続されるプローブカードとを少なくとも備えたテスター本体部を有する試験装置のテスター本体側にプローブカードに配設したプローブピンの温度を監視するサーモグラフィを設ける。

(もっと読む)

半導体集積回路の試験方法および試験装置、並びに、半導体集積回路

【課題】半導体集積回路の試験を、電源電圧のオーバーシュートを生じることなく行うことができる半導体集積回路の試験方法および試験装置、並びに、半導体集積回路の提供を図る。

【解決手段】異なる駆動周波数f(ft,fs,0)で駆動して試験を行う半導体集積回路の試験方法であって、前記駆動周波数を変化させるとき、該駆動周波数を段階的に変化させるように構成する。

(もっと読む)

半導体集積回路

【課題】 ラッチアップの発生を防止し、内部回路に所望のストレスを印加する。

【解決手段】 第1電圧生成回路は、電源電圧より高い第1高レベル電圧を生成する。第2電圧生成回路は、電源電圧より高く、第1高レベル電圧より低い第2高レベル電圧を生成し、バーンイン試験時に停止する。第3電圧生成回路は、電源電圧より低い第3高レベル電圧を生成する。複数の内部回路は、第1高レベル電圧を受けて個別に動作するとともに、バーンイン試験中に動作する。電圧制御回路は、バーンイン試験時に第2高レベル電圧線を第3高レベル電圧線に接続する。寄生トランジスタは、第1高レベル電圧をベースで受け、第2高レベル電圧をエミッタで受ける。複数の内部回路の動作により第1高レベル電圧が一時的に低下するときに、第2高レベル電圧を低い値に設定することで、寄生トランジスタがオンすることを防止できる。

(もっと読む)

増幅装置、電源装置、電源回路および試験装置

【課題】電力増幅器の応答を高速にして、電力増幅器での電力損失を少なくする。

【解決手段】負荷に電源電圧を供給する電源装置であって、設定電圧を発生する設定電圧発生部と、設定電圧に応じた電源電圧を負荷に供給する増幅装置と、を備える電源装置であって、増幅装置は、与えられた入力電圧に応じた出力電圧を出力する電力増幅器と、電力増幅器に駆動電圧を与える電源部と、電源部から電力増幅器へと流れる駆動電流がより大きい場合に、電源部から出力される駆動電圧をより小さくして出力電圧に近づける制御部とを有する電源装置を提供する。

(もっと読む)

半導体集積回路、半導体集積回路の内部状態退避回復方法

【課題】内部状態の退避および回復時の時間を短縮し、消費電力を削減する。

【解決手段】スキャンチェーンは、スキャンパステストのときに、第1回路に含まれる複数の第1フリップフロップと、第2回路に含まれる複数の第2フリップフロップとを鎖状に接続してシフトレジスタとして動作する。バックアップ制御回路は、第1フリップフロップに保持される内部状態を示すデータを、第2フリップフロップをバイパスしたスキャンチェーンを介してメモリ回路に格納する退避動作と、メモリ回路から内部状態を示すデータを読み出して第2フリップフロップをバイパスしたスキャンチェーンを介して第1フリップフロップに再設定する回復動作とを制御する。入力選択回路は、スキャンパステストのテストデータと、メモリ回路から読み出した内部状態を示すデータとのうちの一方を選択してスキャンチェーンに供給する。

(もっと読む)

異常検出システム

【課題】集積回路の大規模化を可及的に抑制しつつ、異常検出を確実に行うことのできる異常検出システムを提供する。

【解決手段】検査対象選択回路部5が、各異常検出信号をそれぞれ伝送するための複数の伝送路をそれぞれ、前記異常検出信号の伝送を禁止する無効状態及び前記異常検出信号の伝送を許可する有効状態のいずれか一方に設定し、有効状態に設定した伝送路に前記異常検出信号が伝送されるとその異常検出信号を割り込みコントローラ4に出力し、CPU2が、各伝送路の有効状態及び無効状態の状態設定に係る設定パターンを切り替え、その設定パターンの切り替えの度に割り込みコントローラ4を介して検査対象選択回路部5から前記異常検出信号を受信したか否かを検出することで、異常の発生源として特定するようにした。

(もっと読む)

プローブ装置、処理装置及びウェハプローブテストの処理方法

【課題】効率的なウェハプローブテストが可能なプローブ装置及び処理装置の提供。

【解決手段】プローブ装置200は複数の測定ステージ220とプローブカードを識別するための第1の識別子を複数のプローブカードから読み取る情報読み取り部260と測定ステージを識別するための第2の識別子が記憶された第1の記憶手段と第1の記憶手段から第2の識別子を読み取る情報読み取り部260と読み取った第1第2の識別子が対応付けられて記憶される測定ステージID記憶部212と搬送アーム230で測定ステージへ搬送された半導体ウェハに第1の検査を行う手段と処理装置から測定ステージの不使用を示す情報と第1及びまたは第2の識別子が対応付けられたステージ情報を受信する情報送受信部270と受信したステージ情報に基づいて、測定ステージへ半導体ウェハを搬送する搬送アーム230と搬送された半導体ウェハに第2の検査を行う手段を具備する。

(もっと読む)

半導体試験装置

【課題】瞬低が生じた場合に制御装置と処理装置との双方のハングアップを回避することができる半導体試験装置を提供する。

【解決手段】半導体試験装置1は、半導体試験装置1を統括制御するテスタコントローラ10と、半導体デバイスの試験結果を用いてリダンダンシ演算を行うリダンダンシシステム20と、バスBで生ずる瞬低を検出する瞬低検出装置30とを備える。テスタコントローラ10は、瞬低検出装置30から瞬低を検出した旨を示す割り込み信号IRが出力されると、瞬低が生じた旨を示すソフトウェア割り込みを、バスBを介してリダンダンシシステム20が備えるリダンダンシ制御装置40及びリダンダンシ演算装置50a〜50nの各々に対して行う。

(もっと読む)

被検査体の検査方法及び被検査体の検査用プログラム

【課題】初回の検査で特定のデバイスDにおいて規則的に検査不良が発生した場合、2回目の検査でその検査不良がデバイスDに原因があるか否かを判断でき、延いては歩留まりを向上させることができる。

【解決手段】本発明の検査方法は、制御装置14の制御下で、ウエハWを載置する載置台11を移動させて、ウエハWの2個のデバイスDにプローブカード12の複数のプローブ12Aを電気的に接触させて、全てのデバイスDについて電気的特性検査を行う際、全てのデバイスDの電気的特性検査を終了した後、複数のプローブ12Aが接触する2個のデバイスDのうち、2個目のデバイスDで検査不良を発生している場合には、全てのデバイスDについて再検査を行い、再検査の際に、プローブカード12とウエハWが接触する今回の接触位置を、前回の検査での接触位置からデバイス1個分だけずらしてデバイスDの電気的特性検査を2個分ずつ行うことを特徴とする。

(もっと読む)

試験装置及び試験方法

【課題】本発明は、試験装置及び試験方法に関し、例えば集積回路の試験装置に適用して、テストパターン等を印加している端子に対して別電源により高電圧を印加する場合に、安全に高電圧を印加することができるようにする。

【解決手段】本発明は、直流電圧V1を低下させた状態で試験対象2のピン7に直流電圧V1を印加した後、動作試験用の出力信号S1の印加を中止し、その後、直流電圧V11を耐久試験用の電圧に立ち上げる。

(もっと読む)

半導体試験装置

【課題】実装識別線に断線やコネクタピンの曲がりなどの異常が発生していることを検出する。

【解決手段】半導体試験装置は、着脱可能な電源部21と、電源部21が実装されていることを示す第1の実装識別データ又は電源部が実装されていないことを示す第2の実装識別データを記憶する実装状態記憶部10と、実装状態記憶部10から第1或いは第2の実装識別データを読み出し、電源部21から識別情報を読み出す制御部7とを備える。実装状態記憶部10は、電源部21と実装状態記憶部10が実装識別線13を介して電気的に接続されている場合に第1の実装識別データを記憶し、電気的に接続されていない場合に第2の実装識別データを記憶する。制御部7は、制御線15を介して識別情報を読み出すことに成功し且つ実装状態記憶部10から第2の実装識別データを読み出した場合に実装識別線13に異常が発生していると判断する。

(もっと読む)

1 - 20 / 119

[ Back to top ]