Fターム[4E351BB18]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | 印刷電気部品の種類と構造 (5,073) | 複合部品(組合せによる上位機能部品) (38) | 非印刷部品を含むもの (20)

Fターム[4E351BB18]の下位に属するFターム

印刷部品と非印刷部品の位置関係 (8)

副基板を搭載するもの (2)

Fターム[4E351BB18]に分類される特許

1 - 10 / 10

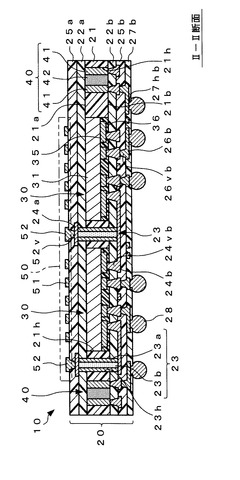

半導体装置内蔵基板モジュール及びその製造方法

【課題】特定の機能を備えた半導体装置の高集積化及び小型化を図ることができるとともに、部品実装に係る製造工程の簡略化や効率化を図ることができる半導体装置内蔵基板モジュール、及び、その製造方法を提供する。

【解決手段】半導体装置内蔵基板モジュール10は、コア基板21に、ウエハレベルCSP構造の半導体装置30が内蔵された基板装置部20と、所望の機能を有する機能部であるコイル部50とが、一体的に形成されるとともに、これらが、積層配線を構成する配線層やビア、貫通電極を介して、相互に電気的に接続された構成を有している。

(もっと読む)

プリント基板

【課題】 安価な構成でレーザドライバICをノイズ源として発生する不要輻射を抑制可能なプリント基板を提供することである。

【解決手段】 レーザ素子と、レーザを駆動する第1の回路と、第1の回路を前段で駆動する第2の回路と、第3の回路とを備え、前記各回路が有する各電源・GND端子とが内部的に分離されたICにおいて、このICを搭載するプリント基板に、レーザ素子と第1及び第2の回路の電源・GND配線から第3の回路及びプリント基板の電源・GND配線へと導かれる経路に設けられるインダクタを備え、そのインダクタによりレーザ素子と第1及び第2の回路の動作によって発生した高周波の電位変動を抑制する。

(もっと読む)

部品内蔵実装基板

【課題】高速・高密度電子機器で特に信号品質の確保が必要なCPU−メモリ間のアドレス線において、小型化と高周波特性確保の両立が実現できる部品内蔵実装基板を提供する。

【解決手段】絶縁基板100の表面上に、CPU101と、チップ部品としての並列終端抵抗105と、メモリ102とが搭載されている。絶縁基板100の内部には、CPU101の直下に第1のデカップリングキャパシタ106aが内蔵され、メモリ102の直下に第2のデカップリングキャパシタ106bが内蔵されている。並列終端抵抗105の直下には、膜部品としての直列終端抵抗103b及び信号品質補償用キャパシタ104bがその面を絶縁基板100の表面に平行にして内蔵されており、両者間に第3のデカップリングキャパシタ106cが内蔵されている。

(もっと読む)

薄膜コンデンサ搭載基板、および該基板の製造方法と該基板を用いてなる半導体装置

【課題】半導体チップをコンデンサに近付けて実装することが可能で、かつ低コストで製造可能な薄膜コンデンサ搭載配線基板及びその製造方法を提供することを目的とする。

【解決手段】金属層Aと金属層Cの間に誘電体層Bを少なくとも備える薄膜コンデンサが、前記金属層Aが外表面となるように接着層を介して配線基板上に積層され、前記薄膜コンデンサおよび前記配線基板の最外層が、接続端子となる箇所を除いてソルダーレジスト層で覆われた薄膜コンデンサ搭載基板であって、前記薄膜コンデンサが、前記金属層Aおよび前記誘電体層Bに前記金属層Cを露出させる開口部Xを有し、前記ソルダーレジスト層が、前記開口部Xの内側面を覆い、前記金属層Cの露出面を接続端子となす開口部Yを有することを特徴とする、薄膜コンデンサ搭載基板とその製造方法を提供する。

(もっと読む)

回路基板の製造方法及びその方法で得られた回路基板

【課題】ディスプレイ用などの各画素を制御するための回路チップが埋め込まれた樹脂シートを有する回路基板を、品質よく、高い生産性のもとで効率的に製造する方法を提供する。

【解決手段】樹脂シート中に回路チップが埋め込まれてなる回路チップ埋設樹脂シートを有する回路基板の製造方法であって、(a)工程用基板上に回路チップを配置・固定する工程、(b)回路チップが配置・固定された工程用基板上に、液状のエネルギー硬化型樹脂シート形成材料を塗布し、未硬化塗布層を形成する工程、(c)前記未硬化塗布層にエネルギーを印加して硬化させ、回路チップ埋設樹脂シート層を形成する工程、及び(d)前記回路チップ埋設樹脂シート層から工程用基板を剥離する工程、を含む回路基板の製造方法である。

(もっと読む)

接合部電流又は電圧検出及び調整機能を有する回路基板及びそれを実装した電子機器

【課題】

基板単体のEMI対策を完遂したとしても、基板を格納する筐体(フレームやシャーシ等)に実装した時点で、不要電磁放射のレベルが変化してしまい、新たなEMI対策を要してしまうという問題がある。

【解決手段】

筐体又は電子機器に実装するための貫通孔と、

前記貫通孔に垂直な面上でかつ前記貫通孔を中心とした円周に鎖交するように設けられたコイル状の導体パターンとを有することを特徴とする回路基板を提案する。

(もっと読む)

回路基板用シート、その製造方法及びチップ埋設回路基板

【課題】ディスプレイ用などの各画素を制御するために回路チップが埋め込まれた回路基板を、品質よく、高い生産性のもとで効率的に作製するための回路基板用シート、及びチップ埋設回路基板を提供する。

【解決手段】回路チップを埋め込むためのエネルギー線硬化型高分子材料からなる回路基板用シートであって、前記エネルギー線硬化型高分子材料からなる未硬化層における回路チップを埋め込む側の表面に、両端部に開口する複数の凹条溝が形成された回路基板用シート、及びこの回路基板用シートにおけるエネルギー線硬化型高分子材料からなる未硬化層に回路チップ埋め込み、これにエネルギー線を照射して硬化させてなるチップ埋設回路基板である。

(もっと読む)

目に見える素子を面上に有する電子モジュール及びそのようなモジュールの製造方法

本発明は、電子モジュールの製造方法、及び2つのシート(2,9)と電子素子(3)の組み付けを含むこの方法により作製されるモジュールに関する。モジュールの面のうちの1つを構成する第1絶縁シート(2)は、電子素子(3)が収納される少なくとも1つのウィンドウ(4)を含み、前記素子(3)の1つの面は前記第1シート(2)の表面と同じ高さにあり、モジュールの外面上に現れる。第2シートはモジュールの他方の面を構成する。モジュールは、素子(3)のウィンドウ(4)の少なくとも周囲を覆う領域内に広がり第1シート(2)と第2シート(9)の間に含まれる領域内にある接着フィルム(5)を備えることを特徴とする。モジュールは、2つの絶縁シート(2,9)の間に設置され素子(3)の内面上にある接続用導体範囲(13)上の素子(3)に接続された少なくとも1つの電子回路(6)を含むこともできる。本発明の目的は、望ましくない残渣が素子(3)の近傍のモジュールの外面上に出現するのを防止することである。これらの残渣は、ウィンドウ(4)を通して、及び/又はウィンドウ内に収納されている素子(3)を通して充填物質(8)が侵入することに由来する。  (もっと読む)

(もっと読む)

電子回路ユニット

【課題】 小型化に好適な面実装タイプの電子回路ユニットを提供すること。

【解決手段】 アルミナ基板1上にコンデンサC1〜C7と抵抗R1〜R3およびインダクタンス素子L1〜L3を含む回路素子とこれら回路素子に接続される導電パターンPとを薄膜形成し、ダイオードD1とトランジスタTr1の半導体ベアチップを導電パターンPの接続ランドにワイヤーボンディングし、かつ、アルミナ基板1上に所定間隔を存して対向する一対の導電路S1,S2からなるインダクタンス素子を薄膜形成し、これら導電路S1,S2によって不平衡/平衡変換回路を構成した。

(もっと読む)

プリント配線板及び電気機器

【課題】電源層とグランド層との各パターンから発生する不要電磁放射を抑制すること。

【解決手段】電子部品を搭載していないプリント配線板10自体の共振周波数fとほぼ同一の共振周波数を有するバイパスコンデンサ18を、プリント配線板10の電源層11とグランド層12との間に搭載する。

(もっと読む)

1 - 10 / 10

[ Back to top ]