Fターム[4E351BB27]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | 印刷電気部品の種類と構造 (5,073) | 構造一般 (3,045) | 同種又は異種の複数部品を積層(立体回路) (12)

Fターム[4E351BB27]に分類される特許

1 - 12 / 12

読み書き装置および携帯機器

【課題】携帯機器への搭載を十分に可能な柔軟性と小型化とを兼ね備えた読み書き装置を提供する。

【解決手段】可搬記録媒体の記録内容を読み書きする読み書き装置として、可塑性を有する1枚のフレキシブル基板1に、可搬記録媒体と電磁結合するアンテナコイル2、アンテナコイル2を介して可搬記録媒体との間でデータの読み書き動作を行う制御回路3、上位装置と接続す上位装置接続用端子5を一端に有する接続ケーブル4を実装する。フレキシブル基板1を複数の階層の多層基板とし、アンテナコイル2を複数の階層に分割配置し、かつ、分割した各アンテナコイルを同一の中心軸を中心として各階層の外周に沿って同一方向に巻き、互いをスルーホールで接続する。制御回路3をアンテナコイル2の中心軸と一致する位置の近傍に集中的に配置する。制御回路3の配置領域を覆うように形成したグランド面に、該グランド面の中心から放射状に複数の切れ込みを形成する。

(もっと読む)

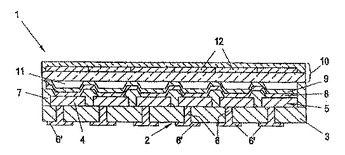

高周波用電子部品

【課題】インダクタ用導体層とキャパシタ用導体層とを含む低温同時焼成セラミック多層基板を用いて構成された高周波用電子部品の特性および信頼性を向上させる。

【解決手段】電子部品1は、1以上のインダクタおよび1以上のキャパシタを含む低温同時焼成セラミック多層基板10を備えている。多層基板10は、積層された複数の誘電体層と、それぞれ積層方向に隣接する2つの誘電体層の間に配置された複数の導体層とを有している。複数の導体層は、1以上のインダクタを構成するための1以上のインダクタ用導体層と、1以上のキャパシタを構成するための2以上のキャパシタ用導体層とを含んでいる。インダクタ用導体層の厚みは、キャパシタ用導体層の厚みよりも大きい。また、インダクタ用導体層における金属材料に対するガラス成分の割合は、0であるか、キャパシタ用導体層における金属材料に対するガラス成分の割合よりも小さい。

(もっと読む)

電子部品およびその製造方法

【課題】

小型、かつ、湿度や温度の影響を受けにくく、長期的な信頼性の高い電子部品を提供する。

【解決手段】

受動素子を内蔵した低温同時焼成セラミックス(LTCC)基板10と;LTTC基板10の表面上に形成され、インダクタ固定に用いられる固定用樹脂絶縁層31と;固定用樹脂絶縁層31のLTTC基板10側と接触していない表面上に形成されたスパイラル状の金属銅製のインダクタ32と;を備える構成を採用する。

(もっと読む)

配線基板及びその製造方法

【課題】配線基板の各層と電子部品との位置精度を向上させることにより、小型化を可能とし、さらに、一括で半導体素子、キャパシタ、抵抗体、及びインダクタ等の電子部品を配線基板内に内蔵させることより、製造時間及びコストを低減させる。

【解決手段】半導体素子、キャパシタ、抵抗、及びインダクタ等の電子部品が内蔵される配線基板において、各層の積層の際に、電子部品が実装されているフィルムキャリアのスプロケットホール等により位置合せを行うことで、配線基板の各層と電子部品との位置精度を向上させることにより、また、技術的に確立されたILB接続技術を用いることにより、半導体素子の狭ピッチ化への対応、接続の信頼性確保、さらには、上層に最短距離で配線を引き出しが可能となり、小型化を実現する。

(もっと読む)

配線基板内蔵用コンデンサ及び配線基板

【課題】樹脂材との密着性を向上させることが可能な配線基板内蔵用コンデンサ、及び信

頼性が充分に確保された配線基板を提供する。

【解決手段】配線基板内蔵用コンデンサ1は、積層された複数の誘電体層3と、互いに異

なる誘電体層3間に配置された内部電極層4,5とを有するコンデンサ本体2等から構成

されている。コンデンサ本体2の側面2c1〜2c3には、コンデンサ本体2の厚さ方向

に延びた凹部2dが形成されている。

(もっと読む)

電気導体構造を備えるフラット基板

本発明は、フラット基板内部に組み込まれた、またはフラット基板表面に付設された電気導体構造、および/または技術的にコーティングされた表面を備えるフラット基板に関する。本発明は、少なくとも1つのセンサがフラット基板に組み込まれ、またはフラット基板の表面に付設され、このセンサが、フラット基板内部に生じる変形に応じてセンサ信号を生成すること、少なくとも1つのアクチュエータがフラット基板に組み込まれ、またはフラット基板の表面に付設され、このアクチュエータが、作動されたとき、フラット基板を機械的に再変形させることができること、ならびに、この少なくとも1つのセンサおよび少なくとも1つのアクチュエータと接続された信号ユニットが設けられ、この信号ユニットが、センサ信号に基づいて、アクチュエータを作動させるアクチュエータ信号を生成し、それによってフラット基板内部に生じる変形が低減されることを特色とする。 (もっと読む)

厚膜電子部品の製造方法

【課題】 印刷工法では形成できない、アスペクト比の高い厚膜導体形成を可能にするとともに、信頼性の高い絶縁膜を形成し、さらに、導体材料以外の接着層を不要とし、絶縁膜の硬化処理回数を減らして工数を大幅に低減する厚膜電子部品を提供する。

【解決手段】 絶縁基板上に下地導体膜を形成し、その下地導体膜の表面に所定のパターンで第1のマスクを形成し、そのマスクで覆われない下地導体層の表面にマスクと同じ厚さの第1の導体層を形成し、第1の導体層の一部と第1のマスクの表面に第2のマスクを形成し、第2のマスクの形成されない導体第1の導体層上に第2の導体層を形成し、第1および第2のマスクを除去し、下地導体膜の露出部分を除去し、絶縁基板表面と第1の導体層の表面を絶縁膜で覆い、第2の導体パターンを絶縁膜上に形成する。

(もっと読む)

配線基板

【課題】 絶縁層及び配線層の剥離やクラックの発生を防止すると共に、表皮効果に基づく高周波伝送損失を低減する配線基板を提供する。

【解決手段】

絶縁層及び配線層を有する配線基板において、前記配線層2、4、6、8は金属部からなり、金属部の厚さ方向の中間部位(第二の金属層2b、4b、6b、8b)が、絶縁層との界面部位よりも気孔率が大きい多孔質金属からなる。

(もっと読む)

導電性ペーストおよびその製造方法、ならびにセラミック多層基板

【課題】未焼成の低温焼結セラミックと導電性ペーストとを同時に焼成する際に、両者の収縮挙動を精度よく合わせ、かつ、未焼成の低温焼結セラミックにおける収縮バラツキを低減し、焼成後の低温焼結セラミックの変形を防止する。

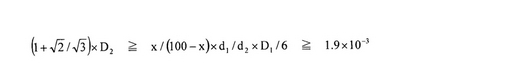

【解決手段】表面に第1の金属酸化物粒子が付着した金属粉末と、前記第1の金属酸化物粒子とは別に添加される第2の金属酸化物粒子と、有機ビヒクルと、を含有し、前記金属粉末の平均粒径をD1(μm)、前記第1の金属酸化物粒子をの平均粒径をD2(μm)とし、前記金属粉末および前記第1の金属酸化物粒子の合計100重量%に対する前記第1の金属酸化物粒子の含有量をx(重量%)としたとき、下記式を満足する導電性ペーストを作製する。 (もっと読む)

(もっと読む)

目に見える素子を面上に有する電子モジュール及びそのようなモジュールの製造方法

本発明は、電子モジュールの製造方法、及び2つのシート(2,9)と電子素子(3)の組み付けを含むこの方法により作製されるモジュールに関する。モジュールの面のうちの1つを構成する第1絶縁シート(2)は、電子素子(3)が収納される少なくとも1つのウィンドウ(4)を含み、前記素子(3)の1つの面は前記第1シート(2)の表面と同じ高さにあり、モジュールの外面上に現れる。第2シートはモジュールの他方の面を構成する。モジュールは、素子(3)のウィンドウ(4)の少なくとも周囲を覆う領域内に広がり第1シート(2)と第2シート(9)の間に含まれる領域内にある接着フィルム(5)を備えることを特徴とする。モジュールは、2つの絶縁シート(2,9)の間に設置され素子(3)の内面上にある接続用導体範囲(13)上の素子(3)に接続された少なくとも1つの電子回路(6)を含むこともできる。本発明の目的は、望ましくない残渣が素子(3)の近傍のモジュールの外面上に出現するのを防止することである。これらの残渣は、ウィンドウ(4)を通して、及び/又はウィンドウ内に収納されている素子(3)を通して充填物質(8)が侵入することに由来する。  (もっと読む)

(もっと読む)

導電体充填ビアを用いた内蔵キャパシタ

内蔵キャパシタ及びその製造方法が提供される。内蔵キャパシタの製造方法は、誘電体基板(100)に少なくとも1つの孔部(115)を形成する工程を含む。孔部を形成するため、誘電体基板は機械的に打ち抜かれ、或いはレーザ切断され得る。第1電極(470)を形成するために孔部は導電体(250)で充填される。第1電極と電気的に接触しないように誘電体基板に導体(360)が形成される。孔部の深さ及び/又は断面積は、電極と導体との間に所望量の容量結合が設けられるように選定される。さらに、第2導体が、第1電極と電気的に接触するように誘電体基板に堆積される。少なくとも第2の孔部が誘電体基板に形成され、第2電極を形成するために導電体で充填される。第2電極は第1電極に電気的に接続される。  (もっと読む)

(もっと読む)

薄膜アセンブリおよび薄膜アセンブリの製造方法

基材(2)および、薄膜技術によって基材上に設けられた少なくとも1つの電子薄膜構成要素(8)、を有する、薄膜アセンブリ(1)であって、ここでベース電極(4)が基材上に提供されており、その上に、薄膜構成要素の一部を形成する、ベース電極薄膜層(21)が、上部トップ電極(9)と併せて配置されており;

この基材(2)は、絶縁材ベース体(3)と、導体層(5)としての金属コーティングと、を有する、従来知られているプリント回路基板(2)から構成され、

この導体層(5)は、ベース電極(4)を形成し、そしてこの目的のために、少なくとも薄膜構成要素(8)の位置上はスムージングされており、および

接触層(18)が、スムージングされ、必要に応じて補強された導体層(5)と、薄膜構成要素(8)の積層薄膜層(21)と、の間に、薄膜技術によって提供されており、ここで接触層が、ベース電極(4)の表面に、物理的または化学的に吸着されている、薄膜アセンブリ。

(もっと読む)

(もっと読む)

1 - 12 / 12

[ Back to top ]