Fターム[4M104DD68]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | リフトオフ (591)

Fターム[4M104DD68]に分類される特許

581 - 591 / 591

半導体装置の製造方法

【課題】良好な電気特性を有し、歩留が改善する半導体装置の製造方法を提供すること。

【解決手段】電子供給層13およびキャップ層14を設けた半導体基板10上に第1絶縁膜15を堆積する第1工程と、半導体基板10上にレジスト膜16を形成する第2工程と、レジスト膜16に開口16aを形成する第3工程と、開口16aを通して第1絶縁膜15をエッチングし開口15aを形成する第4工程と、レジスト膜16を剥離する第5工程と、第1絶縁膜15の開口15aを通して、電子供給層13と選択的にキャップ層14をエッチングし開口14aを形成する第6工程と、キャップ層14の開口14aを塞がない膜厚の第2絶縁膜17を堆積する第7工程と、第2絶縁膜17にエッチバック処理を行い電子供給層13を露出させる第8工程と、第2絶縁膜17をマスクにして電子供給層13を所定の深さまでエッチングする第9工程と、電子供給層13上にゲートメタル20を形成する第10工程とからなる。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法

【課題】リフトオフ処理時間を大にすることなく、寸法精度に優れた微細パターンを容易に形成することのできる半導体装置の製造方法を提供すること。

【解決手段】表面レジスト層15は、前述のパターン露光領域外のみ通常のポジ型レジストとして現像される。そして、下層のレジスト層13はネガ型に反転した表面レジスト層15のパターン露光領域下部も現像されるため、下層のレジスト層13は表面レジスト層15に対し、アンダーカットされた断面形状となる。なお、表面レジスト層15は、下層のレジスト層13との相互拡散の影響により逆テーパ形状を有する。

(もっと読む)

基板の無電解めっき方法および基板上の金属パターン形成方法

【課題】 レジストを用い、無電解めっきによって基板の表面に金属パターンを形成する方法であって、基板表面への密着性に優れた精細な金属パターンを得ることができるとともに、レジストパターンおよびその上の無電解めっき被膜を同時に除去すること、およびレジストパターン上の無電解めっき被膜のみを除去することのいずれもが容易になる方法を提供する。

【解決手段】 レジストパターンが形成された基板の表面全面を酸化処理(例えば紫外線照射)し、次いでレジストパターンの最上層を除去した後、基板の表面全面に無電解めっきを行う。

(もっと読む)

バイポーラトランジスタとその製造方法

【課題】 ベース電極がエアブリッジ構造を有するバイポーラトランジスタにおいて、構造の簡潔化、ベース電極に対する外部配線としてのベース配線のコンタクト位置の自由度を高めることができるようにする。

【解決手段】 ベース層13の少なくとも一部が上面に臨んで形成された半導体メサ部BMを有し、そのベース層13にコンタクトされたベース電極15が、半導体メサ部BMより外側の空間に浮上延長する浮上延長部15Fを有し、この延長浮上部15Fをベース電極13に対するベース配線42のコンタクト部15Cとする。このようにして、コンタクト部を固定部に設ける場合におけるこの固定部を形成するための構造、製造の煩雑さを回避でき、かつベース電極に対するベース配線のコンタクト部の選定の自由度をたかめ、レイアウト等の設計の自由度を高めるものである。

(もっと読む)

窒化物系化合物半導体装置及びその製造方法

【課題】 極めて簡単な手段を採ることで、窒化物系化合物半導体と電極との接触抵抗を低下させ、また、電極表面及び電極パターンエッジのモフォロジを良好に維持することを可能にして高い信頼性を実現できるようにする。

【解決手段】 金属窒化物、例えばTiNを含む第1の層及びMox Ga1-x (0<x<1)を含む第2の層が半導体に近い側から前記の順に積層されてなる電極を備えてなることが基本になっている。

(もっと読む)

トランジスタの製造方法、電気光学装置の製造方法、および電子デバイスの製造方法

【課題】 チャネル長の短い薄膜トランジスタを簡便に、かつ、低廉なコストで形成することができる薄膜トランジスタの製造方法を提供する。

【解決手段】 液滴乾燥法を用いることによってバンク30を形成し、このバンク30を挟んでソース電極40aとドレイン電極40bを形成する。その後、バンク30を剥離することによって得られる溝パターン50に半導体材料を供給して半導体層を形成し、ゲート絶縁膜、ゲート電極等を形成することにより、薄膜トランジスタを製造する。

(もっと読む)

ナノワイヤによってコンタクトがとられる導電性材料の層を有する電子装置を製造する方法

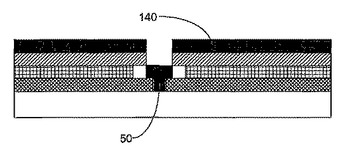

本発明による電子装置(100)は、第1値と第2値との間で電気的にスイッチ可能な電気抵抗率を有するメモリ材料の層(107)を備える。メモリ材料は相変化材料でもよい。電子装置(100)は電子装置の第1端子(172)とメモリ材料の層(107)を電気的に接続する一組のナノワイヤ(NW)をさらに備え、それによって、第1端子からナノワイヤ(NW)及びメモリ材料の層(107)を介して電子装置の第2端子(272)への電流の伝導を可能にする。各ナノワイヤ(NW)は各々のコンタクト領域でメモリ材料の層(107)に電気的にコンタクトがとられる。全てのコンタクト領域ほぼ同一である。本発明による方法は、本発明による電子装置(100)を製造するのに適している。  (もっと読む)

(もっと読む)

自己走査型発光素子アレイチップおよびその製造方法

【課題】基板の表面側にアノード電極またはカソード電極を設けた発光素子サイリスタが複数配列された自己走査型発光素子アレイチップであって、チップ面積が大きくならない構造を提供する。

【解決手段】p形GaAs基板10の上に、p形GaAs層12,n形GaAs層14,p形GaAs層16,n形GaAs層18が順次積層され、n形GaAs層18上にカソード電極22が、p形GaAs層16上にゲート電極23が形成されている。GaAs層12に溝50が設けられ、溝の側壁にアノード電極20が形成されている。

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

581 - 591 / 591

[ Back to top ]