Fターム[4M106CA01]の内容

半導体等の試験・測定 (39,904) | 検査内容 (5,684) | 電圧−電流特性 (1,196)

Fターム[4M106CA01]に分類される特許

1,181 - 1,196 / 1,196

マイクロバンプの形成方法

【課題】 微細化、狭ピッチ化が進んでいるコンタクトプローブとして使用可能なニッケルバンプを、湿式めっきプロセスを用いて形成する方法を提供すること。

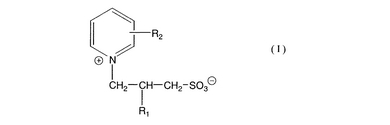

【解決手段】 微小開口部を有するフォトレジストで被めっき基板を被覆し、次いで当該被めっき基板を、添加剤として次の式(I)、

【化1】

(式中、R1は水素原子または水酸基を示し、R2は水素原子またはビニル基を示す)

で表されるピリジニウムプロピルスルホネートまたはその誘導体を含有するニッケルめっき浴により電気めっきし、前記微小開口部部分にニッケルめっき皮膜を析出させることを特徴とするマイクロバンプの形成方法。

(もっと読む)

プローブの位置合せを行なう方法

支持基板に対してプローブを位置合せする方法は、平坦面と縁部とを形成し第1の結晶面をさらに形成する支持基板を配設するステップと、縁部の表面に第1の露出領域を形成する第1のマスクを支持基板の表面に配設するステップと、特定の腐食剤と、第1の露出領域をエッチングするこの腐食剤により形成される陥凹において第1の側壁と反対側の第2の側壁と縁部から遠隔した端部壁と底壁とを形成する陥凹とを配設するステップとを含む。この方法は、平坦面と、第1の結晶面と同一の第2の結晶面とを形成するプローブ基板を配設することと、特定の腐食剤を使用してプローブ基板からプローブを形成する際に、第1および第2の結晶面が全く同じに配置され、プローブが第1の側壁及び第2の側壁と一致する表面を形成するようにプローブ基板を配置することとをさらに含む。  (もっと読む)

(もっと読む)

プローブ再試験データ解析を使用するウェハ試験での生産性向上

【課題】製造後に集積回路デバイスをウェハ/プローブ試験する方法およびシステムを提供すること。

【解決手段】本発明は、初期グループのデバイス(例えば集積回路チップ)を試験して、試験に不合格となった初期不合格グループのデバイスを生成することで始まる。初期不合格グループ内のデバイスは、故障のタイプで識別される。次いで、本発明は、初期不合格グループ内のデバイスを再試験して、再試験に合格した再試験合格グループのデバイスを識別する。次に、本発明は再試験合格グループ内のデバイスを分析し、それによって、初期試験に不合格となった不合格デバイスが再試験に合格する尤度に関する統計を故障のタイプに従って本発明で生成することが可能となる。次いで、本発明は、これらの統計を評価して、どのタイプの故障が所定のしきい値より高い再試験合格率を有するかを判定する。これにより、本発明は、再試験が承認されるタイプの欠陥を列挙する最適化再試験テーブルを含むデータベースを生成する。

(もっと読む)

速い製作サイクルを有する高密度の相互接続システム

【課題】改善された製作サイクルを提供する、コネクタ用、ソケットアゼンブリ用および/またはプローブカード・システム用などの改善された相互接続システムおよび方法を提供すること。

【解決手段】コネクタ用、ソケットアゼンブリ用および/またはプローブカード・システム用などの改善された相互接続システムおよび方法が、記載される。典型的なシステムは、プローバー内に搭載された半導体ウェハに対する電気的接続を確立するためのプローブカード・インタフェース・アゼンブリ(PCIA)を有する。PCIAは、上面および対向する下部平らな搭載面を有する、半導体ウェハに平行なマザーボード、マザーボードの下面とウェハ間に設置される少なくとも3つのポイントにより定義される基準平面、マザーボード搭載面の下に設置される少なくとも1つのコンポーネント、およびウェハに対する基準平面の平面性を調整するためのメカニズムを有する。そこから延在する複数のスプリングプローブを有するプローブチップは、さらなる平面性の調整を必要とせずに、搭載可能かつPCIAから取り外し可能である。相互接続構造および方法は、改善された製作サイクルを提供することが好ましい。

(もっと読む)

インテリジェントなプローブカードのアーキテクチャ

ウェハのテストシステムのプローブカードが提供され、プローブカードの基板上特徴は、以下の1つ以上を含む(a)複数のレジスタを各DUT入力と直列に配置し、欠陥のあるDUTの分離により提供される、DUT信号の分離(b)各DUTの電力ピンと直列なスイッチ、電流リミッタ、またはレギュレータにより提供され、電力供給を欠陥のあるDUTから分離する、DUT電力の分離(c)基板上のマイクロコントローラまたはFPGAを用いて提供される自己診断(d)基板上の追加的なテスト回路に適応するよう、プローブカードの一部として提供される、堆積型ドーターカード(e)ベースPCBとドーターカードとの間またはベースPCBとテストシステムコントローラとの間のインターフェースワイヤの本数を最小化するよう、ベースPCBとプローブカードのドーターカードまたはテストシステムコントローラとの間のインターフェースバスを使用すること。  (もっと読む)

(もっと読む)

プローブカード及びその製造方法

プローブカード1を、一端側にウエハ側プランジャ51、他端側に基板側プランジャ52を有する複数のプローブピン50と、複数のプローブピン50

が半導体ウエハの外部端子の配列に対応して配列されるとともに、プローブピン50のウエハ側プランジャ51が臨出するように、複数のプローブピン50を支持する上下2つのプローブガイド30,40と、プローブガイド30,40に支持されたプローブピン50の基板側プランジャ52が接触するパッド13を有するプリント基板10と、プリント基板10の裏面に設けられた補強部材20とから構成する。そして、プローブガイド30,40を半導体ウエハの熱膨張係数と実質的に同じ熱膨張係数を有する材料によって作製し、プローブガイド30,40をその周縁部及び中心部においてプリント基板10及び補強部材20に固定する。 このような構成を有するプローブカード1は、半導体ウエハの外部端子及びプリント基板10のパッド13に対するプローブピン50の針位置精度を高く維持することができる。

(もっと読む)

被試験デバイスに対する試験信号の非接触インターフェーシング

本発明は、被試験電子デバイスの試験に際し、被試験デバイスに対して物理的に接触せずに試験信号を通信することができる、インターフェ−シングに関する。インターフェース装置は、テスターから試験データを受信する。試験データを表す信号は、インターフェース装置および被試験デバイス上の電磁的に接続された構造を介して被試験デバイスに送信される。被試験デバイスは、試験データを処理し、応答データを生成する。応答データを表す信号は、被試験デバイスおよびインターフェース装置上の電磁的に接続された構造を介してインターフェース装置に送信される。  (もっと読む)

(もっと読む)

アクティブ・ウェハプローブ

能動回路(16)を備える、半導体ウェハを検査するのに好適なプローブ。プローブは、能動回路(16)と支持構造(10)との間に可撓性の相互接続部(14)を備えることができる。そのプローブは、テスト下のデバイスに対して、比較的低いキャパシタンスを負荷することができる。  (もっと読む)

(もっと読む)

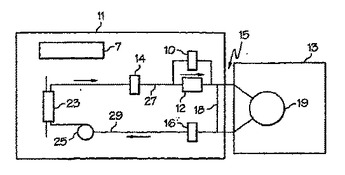

熱制御式チャックにおける電気的ノイズを低減する装置および方法

半導体ウェハなどのワークピースおよびそのウェハを支持するチャックの温度を制御する装置および方法が、説明される。この装置は、温度制御用流体の温度の制御に使用される熱交換器を含む。第1の流体搬送経路により温度制御用流体は、熱交換器から排出口に搬送される。排出口はワークピースチャックに連結されており、温度制御用流体がワークピースチャックに搬送されるようになっている。第2の流体搬送経路により温度制御用流体は、導入口から熱交換器に搬送される。導入口はワークピースチャックに接続されており、温度制御用流体がワークピースチャックから温度制御装置に搬送されるようになっている。二重流量方式を用いて、チャックの温度を変化させているときには、温度制御用流体を相対的に大流量で循環させてチャックの温度変化が高速で行われるようにする。チャックの温度を所定の設定点温度に保持しているときには、流体の流量を減じて、摩擦電気効果等の流体の動きがもたらす電気的ノイズが低減されるようにする。毛細管が、第1および第2の流体搬送経路の間に連結される。第1および第2のバルブを第1および第2の流体搬送経路に連結して、チャックが高温状態のときに流体がチャックに流れ込まないようにすることで流体の沸騰がひき起こす動きを無くしている。  (もっと読む)

(もっと読む)

光画成(photo−defined)マイクロ電気接点の形成方法

半導体集積回路をテストするためのプローブ・テスト・ヘッドを製造する方法は、1つ又は複数のマスク73として、複数のプローブ81の形状72を画成するステップと、該マスク73を使用して、複数のプローブを製造するためのステップと、第1のダイ42と第2のダイ44内の対応するホールを通して複数のプローブ81を配置するステップとを含んでいる。該複数のプローブ81を製造するためのステップは、フォト・エッチングと光画成電気鋳造のうちの1つを含んでもよい。  (もっと読む)

(もっと読む)

半導体処理ステップに関連するエッチ・バイアスを決定する試験装置及び方法

半導体処理ステップに関連するエッチ・バイアスを決定するテスト装置であって、基板と、基板上にあり第1の幅を有する第1のカソード層と、基板上にあり第2の幅を有する第2のカソード層と、基板上にあるカソードの大きな面積とを含んでおり、カソードの大きな面積は、第1及び第2の幅のいずれよりも実質的に大きな第3の幅W“及び長さL”を有する。  (もっと読む)

(もっと読む)

半導体コンポーネントとウエハの製造を評価するための手法

ウエハが部分的に製造された状態である時点からでも、ウエハの製造を分析することができる。特定の性能パラメータ値は、ウエハのダイの能動領域の複数の箇所で決定することができる。特定の性能パラメータが、製造の特定の製造プロセスを示すことは周知である。このとき、評価情報は、複数の箇所における性能パラメータ値の変動に基づいて得ることができる。これは、ダイから生成されるチップの有用性に影響を及ぼさずに実施可能である。評価情報は、性能パラメータ値が示した特定の製造プロセスを含む1つ以上のプロセスが実施された方法を評価するために使用することができる。  (もっと読む)

(もっと読む)

検査パッド構造を有する集積回路および検査方法

半導体装置(10)は、ワイヤボンディングのために周囲に多数のボンド・パッド(24)を有する。半導体装置(10)は、モジュール(12)およびその他の回路を有するが、モジュール(12)は検査のために他の回路よりも遥かに長い時間を必要とする。比較的少数のボンド・パッド(20)、モジュール・ボンド・パッド(20)が、少なくとも部分的に、内蔵自己検査(BIST)(16)回路を有する半導体装置によるモジュール検査のために必要である。これらのモジュール・ボンド・パッド(22)の機能性は、半導体装置(10)の上面上および内部に二重化されており、モジュール検査パッド(22)は周辺のボンド・パッド(24)よりも遥かに大きい。検査のために大きなパッド(22)を有することにより、プローブ・ニードルを長くすることができ、したがって並行検査機能が向上する。機能性の二重化は、モジュール・ボンド・パッド(20)およびモジュール検査パッド(22)が互いに短絡しなくてよいように、検査パッド・インターフェースを介して達成する。  (もっと読む)

(もっと読む)

プローブカードを平坦化するための装置及びその使用方法

第1の平面を定める特徴部(68)を有する補強部材(60)を備えた、ウェーハプローブ(15)及びプローブカード(34)に用いるための装置(69)。補強部材は、プローブカードの中央部分(56)の上に装着することができる。基準部材(42)は、ウェーハプローブに装着するために備えられ、第2の平面を定める特徴部(44)を伴う下面を有する。第1の平面を定める補強部材の特徴部が、第2の平面を定める基準部材の特徴部に押しつけられた時に、プローブカードのプローブ要素(59)は、ウェーハプローブに対して実質的に平坦化される。 (もっと読む)

半導体集積回路を試験するための試験機アーキテクチャ

モジュール式試験機アーキテクチャ(100)により、エンド・ユーザがスキャン・チェーン・モジュールおよびクロック・ドライバ・モジュールを組み合わせることができる。各モジュールは、同期バス(118)を介して相互接続され、それによって試験モジュール同士が互いに同期するのが可能であり、したがって、各モジュールは、試験全体におけるそのモジュールの部分を、他のモジュールによって行われる試験に対して適切な時間に実行することができる。このモジュールには、BISTドライバ・モジュール、データ取得モジュール(208)、ネットワーク化インターフェース・モジュール(202)、コントローラ・モジュール(204)、電流測定モジュール(210)、およびDCパラメトリクス・モジュールを含めることができる。

(もっと読む)

(もっと読む)

能動電子部品の直接冷却をともなう冷却アセンブリ

テストシステムまたは半導体パッケージにおいて使用するプローブカード冷却アセンブリには、直接冷却によって冷却される1つまたは複数のダイを備えたパッケージが含まれる。冷却パッケージには、能動電子部品を備えた1つまたは複数のダイおよび少なくとも1つの冷却剤ポートが含まれ、この冷却剤ポートによって、動作中に、冷却剤が、高密度パッケージに入り、ダイの能動電子部品を直接冷却することが可能となる。 (もっと読む)

1,181 - 1,196 / 1,196

[ Back to top ]