Fターム[4M106CA26]の内容

半導体等の試験・測定 (39,904) | 検査内容 (5,684) | 記憶の良否 (30)

Fターム[4M106CA26]に分類される特許

1 - 20 / 30

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の電気的テストにおいて、テストヘッド内の電源からプローブ等に至る比較的長い経路を介して供給される電源電圧の変動を防止するために、通常、テストボード上等に、電界コンデンサ等の大容量のバイパスコンデンサを設置している。しかし、大容量のバイパスコンデンサで吸収できる変動は、せいぜい数十ナノ秒程度の比較的短時間の変動のみであり、100ナノ秒を超えるような比較的長時間の変動には対応できない。

【解決手段】本願発明は、半導体集積回路装置の製造工程中において、半導体集積回路装置の電気的テストを実行するに当たり、電源電圧をテストボード上に設けられた電池から供給するものである。

(もっと読む)

ウェハテスト装置、ウェハテスト方法およびプログラム

【課題】ウェハテストのテスト時間を増加させることなく、検出された不良セルがいずれの不良パターンで不良となったのかを検知できるようにすること。

【解決手段】ウェハテスト装置は、第1および第2のテストプログラムを保持する記憶部と、第1のテストプログラムを用いてロット内の複数のウェハのうちの一部のウェハに対するテストを行なうとともに、第2のテストプログラムを用いてロット内の複数のウェハのうちの残部のウェハに対するテストを行なう演算部とを備え、第1のテストプログラムは、ウェハに対して複数の動作テストを実行し、各動作テストが終了するごとにウェハに含まれる不良メモリセルの累積情報を装置の外部に出力し、第2のテストプログラムは、ウェハに対して複数の動作テストを実行し、すべて動作テストが終了した後にウェハに含まれる不良メモリセルの累積情報を装置の外部に出力する。

(もっと読む)

半導体記憶装置の評価方法

【課題】半導体記憶装置のトンネル絶縁膜の電荷分布を評価することが可能な半導体記憶装置の評価方法を提供する。

【解決手段】半導体記憶装置の評価方法は、浮遊ゲート型の半導体記憶装置の評価方法である。時間の対数の変化に対する前記半導体記憶装置のメモリセルの閾値電圧Vtの変化率に、ε*Cr*2k/Tox/qを乗じる。なお、εはトンネル絶縁膜の誘電率であり、Crは前記メモリセルのカップリング比であり、Toxは前記メモリセルのトンネル酸化膜の膜厚であり、kは電荷がデトラップする時の存在確率の減衰率でありk=(2mE/(h/2π)2)0.5と表され、mは電子の質量、 Eは前記トンネル絶縁膜のトラップのエネルギー準位、hはプランク定数、πは円周率である。これにより、前記メモリセルのトンネル絶縁膜中の電子濃度分布を求める。

(もっと読む)

半導体装置の不良解析システム及び方法

【課題】フェイルビットマップを速やかに表示し、半導体装置の検査コストの増大を防止できる半導体装置の不良解析システムを提供する。

【解決手段】不良解析システムは、物理フェイルビットマップをメッシュ分割して、一部ビット不良領域のフェイルビットマップ画像データを縮約率毎、チップ毎、レイヤ毎に分類して第1画像データ記憶領域32に記憶する。また、不良解析システムは、フェイルビットマップ画像データを不良モードの種類毎、縮約率毎、チップ毎、レイヤ毎に分類して第2画像データ記憶領域34に記憶する。さらに、不良解析システムは、ユーザからの表示形式及び/又は表示領域の指示に基づいて、第1画像データ記憶領域32又は第2画像データ記憶領域34からフェイルビットマップ画像データを抽出して結合し、表示部44に表示する。

(もっと読む)

半導体装置の不良解析方法

【課題】不良解析時間を短くできる半導体装置の不良解析方法を提供する。

【解決手段】解析対象としての半導体装置を平面的に並ぶ複数のブロックに仮想的に区画し、前記半導体装置のレイアウトデータと前記ブロックの仮想区画データとに基づいて、前記ブロック毎に、前記各ブロック中に存在する複数の回路構成要素のうちの同一種類のあるものと他のものとによる各集合についての不良発生の確度を算出し、これにより前記ブロック毎に複数の前記確度が表された、テーブルを作成し、前記半導体装置に対して電気的特性のテストを行って、不良を把握した場合には、把握した不良の存在するブロックを、前記複数のブロックの中から特定し、前記テーブルを参照して、前記特定したブロックにおいて、前記確度の高い順番に、その確度に関連する種類の前記回路構成要素に対して、不良を検出するための物理解析を行う。

(もっと読む)

抵抗メモリ素子の抵抗測定方法及び抵抗測定システム

【課題】抵抗メモリ素子の抵抗測定方法及び抵抗測定システムを提供すること。

【解決手段】抵抗メモリ素子の抵抗測定方法及び抵抗測定システムにおいて、前記抵抗メモリ素子の抵抗測定のために、まず、データ書き込みパルスを印加した後、抵抗読み取りパルスを印加する。前記抵抗読み取りパルスを印加した時のパルス波形から前記抵抗メモリ素子のセルを通して、降下する微少電圧と、これを使い、抵抗メモリ素子の抵抗を測定する。前記方法によると、抵抗メモリ素子のセルにデータを記録した直後の抵抗メモリ素子の抵抗を正確に測定することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】不良アドレス1ビット分を一対のアンチヒューズ素子に記憶させる半導体装置において、一方のアンチヒューズ素子のみが不良品である場合であっても、不良品として検出できるようにする。

【解決手段】半導体装置10は、それぞれハイレベル及びローレベルのうちのいずれか一方にある一対のアンチヒューズ素子51A,51Bと、これらのうちの少なくとも一方がハイレベルにある場合と、両方がローレベルにある場合とで異なる論理情報を出力するオア回路56と、これらの論理状態が互いに異なる場合と、互いに同一である場合とで異なる論理情報を出力するエクスクルーシブオア回路58とを備えることを特徴とする。

(もっと読む)

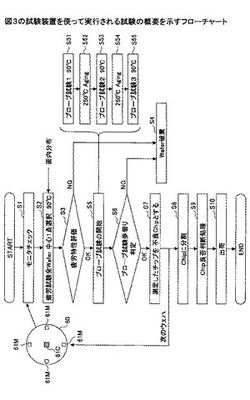

半導体チップの検査方法

【課題】より多くのデータを取得できるようにした半導体チップの検査方法を提供する。

【解決手段】複数の試験チップに通常試験を実施する工程と、複数の試験チップの中から、予め設定されたサンプリング頻度に基づいて特別試験の対象となる試験チップ(即ち、特定チップ)を選択する工程と、特定チップに特別試験を実施する工程と、を含む。特別試験では、特定チップに負荷を与えてこれを破壊又は劣化させる。プローブ検査の工程で、より多くのデータを取得することができる。

(もっと読む)

フラッシュメモリ、およびその製造方法

【課題】 潜在的な不良を抱えたメモリセルトランジスタを含み、半導体基板とゲート電極の間またはゲート電極内に異物が存在する異常構造のメモリセルトランジスタを除去可能なフラッシュメモリ、およびその製造方法を提供する。

【解決手段】 本発明は、半導体基板としてのシリコン基板1上に、上面が平坦な正常構造の正常ゲート電極G1と、上面の少なくとも一部に突起部8aを有する異常構造の異常ゲート電極G2とが配置されたフラッシュメモリにおいて、正常ゲート電極G1は、第一の拡散層3に接続される第一のコンタクト電極30とビット線16とを接続するビア15と電気的に分離され、異常ゲート電極G2は、ビア15と、異常ゲート電極G2上面の突起部8aにおいて電気的に接続されている。

(もっと読む)

半導体装置の検査方法及び半導体装置

【課題】個々の半導体装置について、試験工程での書き換え回数を信頼性高く管理できるようにした半導体装置の検査方法及び半導体装置を提供する。

【解決手段】データの書き換えが可能なメモリ回路23を備えるICチップの検査方法であって、メモリ回路23に、ユーザによって使用される主記憶領域31と、試験用記憶領域33とを用意しておき、主記憶領域31に対してデータの書き換え試験を行う工程と、書き換え試験を行う工程で主記憶領域31に対して実際に行われたデータの書き換え回数を試験用記憶領域33に記録する工程と、を含む。このような方法によれば、個々のICチップについて、その出荷前の試験工程で実際に行われたデータの書き換え回数を正確に管理することができる。

(もっと読む)

強誘電体メモリの製造方法および試験システム

【課題】 ツインセンスアンプを有する強誘電体メモリの製造工程において、インプリント特性を考慮した試験を実施し、インプリントによる不良が市場で発生することを防止する。

【解決手段】 単一の論理レベルを記憶する強誘電体キャパシタを有する第1メモリセルと、相補の論理レベルを記憶する強誘電体キャパシタ対を有する第2メモリセルと、第1および第2メモリセルに接続されたツインセンスアンプとを有する強誘電体メモリが製造される。まず、第1および第2メモリセルに第1論理が書き込まれ、インプリントを進めるために、強誘電体メモリが高温下で放置される。次に、第1メモリセルに第1論理と逆の第2論理が書き込まれる。そして、第1メモリセルに保持されている論理が読み出され、読み出される論理が第2論理と異なるとき、強誘電体メモリの不良が検出される。

(もっと読む)

半導体装置製造システム、半導体装置の製造方法、及び半導体装置

【課題】半導体装置の集積度を向上する。

【解決手段】本発明による半導体製造装置は、メモリセルテストシステム30と素子配線形成装置50とを具備する。メモリセルテストシステム30は、メモリセル部が形成された半導体装置に対し、メモリセルテストを行う。素子配線形成装置50は、メモリセルテストの結果に応じたパタンのヒューズ素子11a〜11fを半導体装置上に形成し、ヒューズ素子が形成された領域の上方の領域に素子又は配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタの特性への影響を抑制することができる半導体装置の製造方法を提供する。

【解決手段】正常と不良とを区別するしきい値として、予め求めておいた残留分極量の減極率を設定する(ステップS12)。チップ毎に一部のメモリセルの残留分極量を室温で測定する(ステップS13)。この測定では、当該強誘電体メモリの通常の動作電圧、例えば3.3Vを印加する。ステップS13において残留分極量QSW0を測定したメモリセルの残留分極量を150℃で測定する(ステップS14)。この測定でも、当該強誘電体メモリの通常の動作電圧、例えば3.3Vを印加する。これら2つの残留分極量を用いて減極率を算出する(ステップS15)。ステップS12で設定したしきい値とステップS15で求めた減極率とを比較し、減極率がしきい値以下のものを合格と判定し、それ以外のものを不良と判定する(ステップS16)。

(もっと読む)

半導体検査装置及び半導体検査方法

【課題】半導体メモリの良否を確実に判定することができる半導体検査装置及び半導体検査方法を得る。

【解決手段】メモリセルアレイ110に対して最初にステップ440aの1ビット分のセルの”1”読み出しテスト、ステップ440bの1ビット分のセルの”0”書き込み、ステップ440cの1ビット分のセルの”0”読み出しテストを実行することで、電源供給からステップ440cのリファレンスセルの”0”読み出しテスト開始までの時間を大幅に短縮できる。また、その結果、ノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ126のゲート126gの断線又は高抵抗によるリファレンスビット線116bの不良をスクリーニングすることができる。

(もっと読む)

データ保持特性の低下を防ぐシステム

【課題】相変化抵抗メモリに記憶されるコンフィギュレーションデータのデータ保持時間が、後工程における高温により短縮するのを防ぐための方法を提供する。

【解決手段】後工程の高温によるデータ保持特性への影響をなくすために、後工程前、または後工程中に抵抗メモリを冷却する冷却システムを設ける。また、後工程後にコンフィギュレーションデータを抵抗メモリから読み出すとともに、該データを該抵抗メモリに書き込みなおす。

(もっと読む)

半導体装置

【課題】高速DRAMなどにおいてボンディングパッドと共に評価パッドも増加する状況の下、余計なチップ面積の増大を最小限に抑える。

【解決手段】ウェハ上の1チップ分のDRAMでは、チップ上の中央部に、アドレスピン、データピン、電源ピン、グラウンドピンなどの様々な機能を持つ複数のパッド(No.1~103)が一列に配置されている。これらのパッド(No.1~103)のうち、パッケージ組み立て時にはボンディングはするが評価用パッケージ段階やプローブテスト時では使用しないパッド3の横に、パッケージ組み立て時にボンディングは実施されない電源モニタ用評価パッド4が近接して配置されている。

(もっと読む)

半導体集積回路および半導体集積回路のテスト方法

【課題】 半導体集積回路が良品か否かを容易に識別する。

【解決手段】 プログラム回路は、第1プログラム部がプログラムされているときにパス信号を活性化する。第1プログラム部は、内部回路のテストがパスしたときにプログラムされる。モード設定回路は、外部制御により動作モードを通常動作モードまたはテストモードに切り替える。状態制御回路は、通常動作モード中にパス信号が非活性化されているときに、内部回路のうち一部の回路に正常動作と異なる異常動作を実行させる。通常動作モードにおいて、異常動作を認識することにより、半導体集積回路が不良であることを容易に認識できる。テストモードに移行することなく、不良を認識できるため、例えば、半導体集積回路を購入するユーザにも、不良を容易に認識できる。

(もっと読む)

半導体試験システム

【課題】半導体装置に関する不良の検出精度を維持しつつも短時間で試験を実施することができる半導体試験システムを提供することができる。

【解決手段】半導体装置に関して試験を実施すべき複数の検査項目について管理する検査項目管理手段9と、複数の検査項目に従って半導体装置について試験を実施する試験実施手段11と、試験実施手段11による試験結果に基づいて、複数の検査項目に含まれる特定検査項目によって検出可能な特定の不良が、複数の検査項目に含まれる他の検査項目によって検出可能であるか否かについて判断する検出可否判断手段21と、検出可否判断手段21によって特定の不良が他の検査項目で検出可能であると判断された場合、検査項目管理手段9で管理している複数の検査項目から特定検査項目を削除する検査項目削除手段13とを備える。

(もっと読む)

半導体検査装置および半導体装置の検査方法

【課題】半導体装置の高精度な評価が可能な半導体検査装置および検査方法を提供する。

【解決手段】pn接合およびプラグが形成された段階の半導体ウエハ22に対して、pn接合に実動作時と同等の電位が印加されるような照射条件で一次電子線17を複数回照射し、これに応じて発生した二次電子線18をフォトマル67で検出し、その検出信号を二次電子検出系回路部34に出力する。二次電子検出系回路部34は、入力された検出信号をアンプ62,63で増幅後、A/D変換器66を経由して二次電子画像51の輝度信号を出力する。このような検査に際し、一次電子線17の大きさを一次電子線量モニタ部36で監視し、二次電子検出系回路部34の増幅率およびオフセット電位を一定レベル信号モニタ部37で監視し、これらに変動が生じた場合には二次電子画像51の輝度信号に対して変動分の補正を行う。

(もっと読む)

1 - 20 / 30

[ Back to top ]