Fターム[4M106DD16]の内容

半導体等の試験・測定 (39,904) | ウェーハ・プローバ(接触型検査装置) (3,541) | プローブ (3,210) | マルチプローブ (215)

Fターム[4M106DD16]に分類される特許

1 - 20 / 215

格子状配列プローブ組立体

【課題】 狭ピッチ多ピンの格子状配列型パッドに適応可能なプローブカードを提供すること。

【解決手段】 垂直プローブ部とプローブのバネ構造部と回路基板までの導電部を樹脂フィルム上に1つ又は複数配置した第1のプローブ群と、前記第1のプローブ群と同一又は異なる配置のプローブ群を有する第2、第3、第4等のプローブを適切な間隔で積層し、前記プローブ付樹脂フィルム上のプローブの端子配列方向が、ウェハ上のチップのパッドのXY方向配列に対して所定の角度を有することにより、所望の格子配列のパッド接続部を有する。

(もっと読む)

半導体製造装置用ヒータユニット

【課題】 高い均熱性および高い剛性を有していることに加えて、温度変化に対する平面度変化が極めて小さい半導体製造装置用ヒータユニットを提供する。

【解決手段】 ウエハを載置するための載置面1aを有する銅やアルミニウムなどの金属からなる載置台1と、載置台1を支持するセラミックス製の支持板2と、支持板2の下面側に設けられた銅やアルミニウムなどの金属からなる保持部材3と、支持板2を下側から支持する複数の支持部材4とからヒータユニットを構成する。支持板2にはその厚み方向に複数の貫通孔2aを設けて、これら複数の貫通孔2aにそれぞれ挿通した複数の結合部材7で載置台1と保持部材3とを結合するのが好ましい。

(もっと読む)

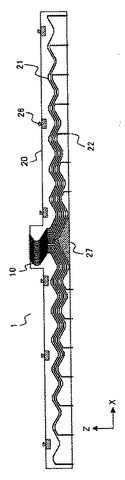

パワーデバイス用のウエハキャリア及びパワーデバイスの検査方法

【課題】パワーデバイスをウエハ状態のまま検査することができるパワーデバイス用のウエハキャリアを提供する。

【解決手段】本発明のパワーデバイス用のウエハキャリア20は、パワーデバイスの電気的特性検査をウエハレベルで行う際に、検査装置10の載置台11上に吸着固定して用いられ且つ複数のパワーデバイスが形成されたウエハWを保持するもので、キャリア本体21と、キャリア本体21の第1の主面上にウエハの載置面として形成された導電性金属膜23と、載置面に形成された真空吸着用の溝20Aと、載置台11の真空吸着用の溝11Aと連通し且つ真空吸着用の溝20A内で開口する吸引孔20Bと、を備えている。

(もっと読む)

試験装置、ステージ装置、および試験方法

【課題】両面に電極を有する半導体デバイスをウエハの状態で試験する。

【解決手段】ウエハに形成されウエハの上面側に上側電極下面側に下側電極を有する複数のデバイスを試験する試験装置であって、ウエハが載置されるステージ部と、ステージ部における複数のデバイスの下側電極に対向して設けられた複数の開口内に設けられ下側電極と接触する伸縮可能な複数の下側端子と、複数のデバイスが有する上側電極と接触する複数の上側端子と、上側端子および下側端子を介して複数のデバイスに電圧を印加して、複数のデバイスを試験する試験部とを備え、下側端子はウエハがステージ部に押し当てられるのに伴って収縮する試験装置を提供する。

(もっと読む)

テスタ及びそのテスタを含んだテスト装置

【課題】ウェーハにワンタッチ・テストを行うことができるテスタ及びそのテスタを含んだテスト装置を提供する。

【解決手段】回転自在な構造のテスト・インターフェースを具備することで、ウェーハ・インデキシングなしに、ウェーハにワンタッチ・テストを行うことができるテスタ及びそのテスタを含んだテスト装置であり、該テスト装置は、回転するZIFリング130を具備したテストヘッド100と、前記テストヘッド100に電気的に連結され、ウェーハ内の多数の半導体デバイスをテストするための信号を、前記テストヘッド100に伝達するテスト本体とを具備したテスタ、ZIFリング130と結合するリング状のコネクタ部132と、中央部に配され、半導体デバイスをテストするための多数の探針が配されているニードル・ブロック320と、を具備したプローブカード、テストされるウェーハが置かれて支持されるウェーハ支持チャックを含む。

(もっと読む)

ウエハー検査システム

【課題】リレー回路板により、テスト結果信号の分流を行い、イメージ信号はイメージ処理装置に直接伝送して処理を行うウエハー検査システムを提供する。

【解決手段】ウエハー検査システムは、ウエハー9に対して検査を行い、各プローブ2022はウエハー9に触れ、電気信号を伝送及び受信し、照明器203は開口2021を通して光をウエハー9上に照射し、テストサーバー204は検査の関連プロセス及びデータ処理の執行を制御し、テスト回路板210はテスト信号を発信し、結果信号を受信し、判断を行い、ロードボード208は制御回路板209と少なくとも1個のテスト回路板210に連接し、少なくとも1個のリレー回路板207はプローブカード202、ロードボード208、少なくとも1個のイメージ処理カード206にそれぞれ連接し、伝送データの伝送方向を切り替える。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 熱負荷試験時において、プローブカード用セラミック配線基板に設けられた測定端子とSiウェハの表面に形成された測定パッドとの位置ずれが小さく、異物付着による外観不良の極めて少ないプローブカード用セラミック配線基板とこれを用いたプローブカードを提供する。

【解決手段】 セラミック焼結体が、該セラミック焼結体中に含まれるAlをAl2O3換算およびSiをSiO2換算した合計量を100質量部としたときに、前記MnをMn2O3換算で2.0〜4.0質量部、前記TiをTiO2換算で4.0〜8.0質量部および前記MoをMoO3換算で0.4〜2.1質量部含有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 半導体基板上に形成された半導体集積回路の、特にプローブ検査時間を短縮することができる検査工程を提供する。

【解決手段】 検査対象となる半導体基板には、半導体集積回路本体を含む回路領域2aと、それに隣接するスクライブエリアにTEG3aが形成され、回路領域2aには第1パッド電極5a、5bの列が、またTEG3aには第2パッド電極6の列が設けられる。ここでTEG3aに隣接している方の第1パッド電極5aが第2のパッド電極6に対向しないように配置される。このような状態の第1パッド電極5a、5bおよび第2パッド電極6にプローブ針8a、8b、9を接触させて半導体集積回路の検査とTEGの測定とを同時に行う。

(もっと読む)

半導体デバイスのテスト装置、テストシステム、及びテスト方法

【課題】従来のマルチサイト・テストやコンカレント・テストにおける各種の問題点の少なくとも一部を解決し、テスト時間の短縮を図ること等ができる、テスト装置、テストシステム、及びテスト方法を提供すること。

【解決手段】第1IPコア4と第2IPコア5を集積して構成された第1半導体デバイス1と、第1IPコア4と第2IPコア5を集積して構成された第2半導体デバイス2とを、同時にテストするためのテスト装置20であって、ワークステーション21と、第1IPコア4をテストするための第1テスト回路22と、第1半導体デバイス1に電力を供給する第1電源回路23と、第2IPコア5をテストするための第2テスト回路24と、第2半導体デバイス2に電力を供給する第2電源回路25とを備える。

(もっと読む)

半導体試験方法および半導体試験システム

【課題】半導体試験装置のピンリソースを効率的に使用できる半導体試験方法および半導体試験システムを提供する。

【解決手段】実施形態によれば、半導体試験装置により、同一種類の半導体装置の各々に複数のテスト項目の電気的試験を行う半導体試験方法が開示される。この方法は、前記複数のテスト項目を、前記半導体試験装置の所定数のピンを使用して試験可能なテスト項目群と、前記所定数より少ない数のピンを使用して試験可能なM−1(Mは2以上の整数)個のテスト項目群と、のM個のテスト項目群に分けて、前記各テスト項目群を試験するそれぞれのピン接続を、前記半導体試験装置とM個の前記半導体装置との間で行い、前記ピン接続を行った後、前記半導体試験装置により、前記各テスト項目群の試験を同時に行う、ことを特徴とする。

(もっと読む)

インターポーザ基板

【課題】 測定端子を固定するための基板の変形が少なく、測定端子が半導体チップとなる部分の電気特性を正確に測定することができ、かつアライメントマークを認識しやすくするためのインターポーザ基板を提供する。

【解決手段】 セラミックスからなるインターポーザ基板の主面に、アライメントマークとしての有底穴を有し、有底穴の底面が中心に向かって深くなっている凹状であることとしたことから、インターポーザ基板の強度がアライメントマークが貫通穴である場合に比べて増加し製品の撓みが抑えられ、高精度な位置決めを行なうことができる。さらに有底穴の底面のフラットに近い面積が小さくなるため、画像認識のための反射光を減少させることができ、アライメントマークと主面とのコントラストを大きくすることができアライメントマークの認識性を向上できる。

(もっと読む)

被検査装置用インタフェース回路

【課題】 半導体装置の大型化を抑制できる被検査装置用インタフェース回路を提供する。

【解決手段】 検査装置4により検査される被検査装置5に設けられた端子回路7と接続されて、検査装置4と非接触で通信する第1の入出力回路6を備え、かつ、端子回路7が被検査装置5に信号を入力する回路の場合には、第1の入出力回路6は入力回路により形成され、端子回路7が被検査装置5から信号を出力する回路の場合には、第1の入出力回路6は出力回路により形成されている。

(もっと読む)

半導体検査システム、それを構成する半導体装置および半導体検査装置、並びに半導体装置の検査方法

【課題】半導体検査システムにおいて、単一の電源から複数の半導体主回路部に電源を供給する場合、各半導体主回路部に安定した電源を供給することができない。

【解決手段】本発明の半導体検査システムは、半導体装置と、半導体検査装置とを有し、半導体装置は、半導体基板と、半導体基板に配置された複数の半導体回路領域を有し、半導体回路領域はそれぞれ、半導体検査装置による検査の対象となる半導体主回路部と電源制御部を備え、半導体検査装置は、主電源部と、プローブカードを有し、プローブカードは、主電源部に接続された共通電源配線を備え、共通電源配線から各電源制御部に対して、第1の電源がそれぞれ供給され、電源制御部は、第1の電源を供給源として第2の電源を半導体主回路部に供給する。

(もっと読む)

半導体装置

【課題】 ウエハ上に形成された半導体チップを試験するときに、プローブの移動回数を最小限にし、試験時間を短縮する。

【解決手段】 半導体装置は複数の半導体チップを有し、各半導体チップは、試験信号に応じて試験される回路ブロックと、回路ブロックから出力される試験結果を、隣接する半導体チップの少なくともいずれかと試験結果出力端子とに出力するとともに、隣接する半導体チップから転送される試験結果を隣接する別の半導体チップと試験結果出力端子とに出力する転送回路とを有する。これにより、半導体チップの試験結果を隣接する半導体チップに順次に転送できるため、全ての半導体チップの試験結果を1つの半導体チップの試験結果出力端子から出力できる。

(もっと読む)

半導体素子及び半導体装置の製造方法

【課題】隣接した半導体素子領域(IC領域)を同時に検査しても、検査用のプローブが外部電極から食み出し難くい、半導体素子、半導体ウエハ、及び半導体装置の製造方法を提供する。

【解決手段】外周に沿って配置された複数の外部電極28を有する、矩形の半導体素子38であって、前記外部電極の対向する二辺が、前記半導体素子の一の対角線34に垂直な方向36を向いている半導体素子。

(もっと読む)

検査用半導体装置および半導体装置の検査方法

【課題】非接触インタフェースを備えた半導体装置において、異なる種類の半導体装置を検査する際のコストが増大する。

【解決手段】

検査用半導体装置は、検査用LSIを備え、その検査用LSIは検査対象半導体装置との間で非接触で信号を通信するための複数の非接触インタフェースと、非接触インタフェースに接続された通信部と、通信部を制御する通信制御部と、を有する。通信制御部は、検査対象半導体装置の構成に応じて通信部の動作状態を制御する。

(もっと読む)

プローブカードの製造方法およびプローブカード

【課題】プローブ先端の高さ方向および平面方向に関して高精度に位置決め可能なプローブカードの製造方法およびプローブカードを提供する。

【解決手段】プローブが配置された複数のプローブ基板をプローブカードの第1の基板上に固定する工程を含むプローブカードの製造方法であって、前記複数のプローブ基板に配置されたプローブの先端の高さ方向の位置を揃えた状態で、前記複数のプローブ基板を配置する工程と、前記複数のプローブ基板のプローブが配置されていない方の面に、弾性変形し得るスペーサを配置し、固定用樹脂を塗布する工程と、前記弾性変形し得るスペーサが配置され前記固定用樹脂が塗布された前記複数のプローブ基板の面側に前記第1の基板を載せて加圧し、前記弾性変形し得るスペーサを変形させた状態で前記複数のプローブ基板を前記第1の基板に固定する工程とを備える。

(もっと読む)

半導体集積回路のテスト方法、半導体集積回路のテストプログラム、及び半導体集積回路のテスト装置

【課題】半導体チップのテスト所要時間を短縮する方法を提供すること。

【解決手段】複数の半導体集積回路装置それぞれに、複数のテストの内から互いに異なるいずれかを割り当てる第1のステップと、複数のテストの内、複数の半導体集積回路装置それぞれに割り当てられたテストをそれぞれ実行する第2のステップと、複数のテストの内の特定テストにおいて複数の半導体集積回路装置の内から不良品を検出した場合に、複数の半導体集積回路装置から不良品を除いた残りの半導体集積回路装置に特定テストを次のテストとして割り当てる第3のステップと、残りの半導体集積回路装置に割り当てられた特定テストをそれぞれ実行する第4のステップとを備える。

(もっと読む)

プローブカード

【目的】 本発明の目的は、プローブユニットの配線基板に対する接着力を必要以上に強くすることなく、且つプローブ基板が変形することがないプローブカードを提供することにある。

【構成】 本プローブカードは、プローブ110と、プローブ110が設けられた第1面121と該第1面121の裏側面である第2面122とを有するプローブ基板120と、プローブ基板120の第2面122側に間隔を空けて配置される配線基板200と、プローブ基板120の第2面122と配線基板200との間に介在しており且つプローブ基板120の第2面122に当接する第1当接面131から配線基板200に当接する第2当接面132にかけて貫通する貫通孔133が設けられたスペーサ130と、スペーサ130の貫通孔133内に設けられ、プローブ基板120の第2面122と配線基板200とを接着する接着樹脂140aとを備えている。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 熱負荷試験時において、プローブカード用セラミック配線基板に設けられたプローブピンとSiウエハの表面に形成された測定パッドとの位置ずれが小さく、電気特性の検査に好適に使用できるプローブカード用セラミック配線基板とこれを用いたプローブカードを提供する。

【解決手段】 X線回折のデータを用いたリートベルト解析により求めた結晶相の割合で、ムライトが48〜81質量%、アルミナ、ディオプサイトおよびジルコンから選ばれる少なくとも1種の結晶相が19〜52質量%であり、吸水率が1%以下のセラミック焼結体からなるセラミック絶縁層と、銅が40〜60体積%、タングステンが40〜60体積%となる組成を有する銅とタングステンとの複合導体とを具備する。

(もっと読む)

1 - 20 / 215

[ Back to top ]