Fターム[4M118BA04]の内容

固体撮像素子 (108,909) | 基本構造 (11,702) | 受光部(光電変換部)を複数持つもの (11,448) | ICマルチチップ型 (85)

Fターム[4M118BA04]に分類される特許

41 - 60 / 85

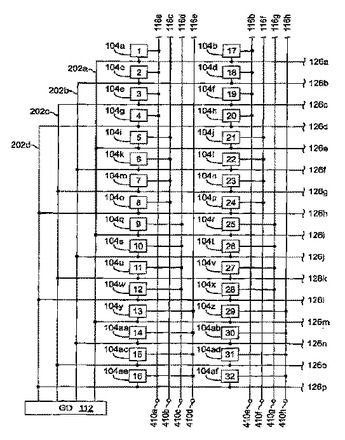

互い違いの画素を有する複数チップを使用する走査型撮像装置

固体撮像システムは、一方の一続きの画素が、他方の一続きの画素に関してずらされ、即ち互い違いにされている第1および第2の一続きの画素(191、192、193)を有する少なくとも1つのCMOS撮像装置(190)を有する。複数の撮像装置が端から端へと配列され、ジャンパ線(48)が画素出力導体または各々を接続し、それによって画素は各々の一続きに対する共通出力増幅器(160、161)へ入り、チップ間オフセット電圧を最小にする。画素は相互から斜めにずらしてよく、カラーリボンフィルタが画像区域を斜めに横切って配列されるカラー撮像装置を構築することができる。この配列はカラーのクロストークを最小にする。マイクロレンズのアレイ(200、210、210'、211)は、各々のマイクロレンズが複数の画素を覆うように置かれる。各マイクロレンズの下側の画素は、斜行部分に沿って整列することができる。同じマイクロレンズの下側の異なる画素は異なる積分時間を有することができ、撮像装置のダイナミックレンジを拡大する。

(もっと読む)

(もっと読む)

放射線画像検出器

【課題】放射線の照射を受けて電荷を発生する電荷発生層と、上記電荷を収集する収集電極、収集電極によって収集された電荷を蓄積する蓄積容量および蓄積容量に蓄積された電荷を読み出すためのTFTスイッチを有する多数の画素と多数の走査線と多数のデータ線とを備えた検出層とが積層され、蓄積容量が、TFTスイッチのドレイン電極に接続される蓄積容量電極とそのドレイン電極が属するTFTスイッチに隣接するTFTスイッチに接続される走査線との間で構成されるとともに、TFTスイッチのアレイが上下に2分割されて駆動されデータ線が上下に2分割された放射線画像検出器において、分割境界部の画素についても蓄積容量を構成し、分割境界部の画像段差を目立たなくする。

【解決手段】TFTスイッチ3のアレイの上下の分割境界部に、分割境界部に配置された画素の蓄積容量4を構成するダミー配線30を設ける。

(もっと読む)

光電変換デバイスの製造方法及び光電変換デバイス

【課題】信頼性が高い長尺の光電変換デバイスを低コストの下に得易い光電変換デバイスの製造方法、及び長尺化しても信頼性の高いものを得易い光電変換デバイスを提供すること。

【解決手段】透明基板5と、透明基板上5に形成された複数の光電変換素子PEと、透明基板5に実装されて複数の光電変換素子PFの各々に生じた電荷を基にデータ信号を生成する信号生成手段30と、透明基板上に形成されて複数の光電変換素子の各々と信号生成手段とを接続する複数の第1配線25と、複数の第1配線25それぞれの一端に1つずつ接続されて前記一端と信号生成手段との間に介在するパッド27と、透明基板上に形成されて信号生成手段30と外部回路とを接続する複数の第2配線37とを備えた光電変換デバイス1Aを製造するにあたり、少なくとも1層からなる導電層をパターニングしてパッドと第2配線35とを形成する。

(もっと読む)

イメージセンサ

【課題】光電変換素子と駆動回路との接続本法を減らし、高SN比で情報を読み取ることができる信頼性に優れたイメージセンサを提供すること。

【解決手段】一対の陽極と陰極との間に狭持され有機化合物層からなる光電変換層によって構成される光電変換素子がアレイ状に配置された複数の光電変換素子アレイ3と、光電変換素子が光電変換した信号電荷を検知し、その信号電荷を読み出すICチップ4と、をガラス基板2上に備えるイメージセンサであって、光電変換素子アレイ3を構成する各光電変換素子のITO陽極5aは、ICチップ4と1対1で接続される配線5bと一体的に形成されるとともに、光電変換素子アレイ3中の各光電変換素子を構成する陰極は、2つ以上の光電変換素子に共通接続されたパターンを有する配線6によって光電変換素子アレイ3上に形成される。

(もっと読む)

イメージセンサモジュール

【課題】光源装置を基板に対して適切に取り付けることが可能なイメージセンサモジュールを提供すること。

【解決手段】主走査方向xに延びる長矩形状の基板1と、光源装置2と、主走査方向xに延びており、光源装置2に正対する光入射面、および上記光入射面から入射した光を主走査方向に延びる線状光として読取対象に対して出射する光出射面を有する導光体と、基板1上に主走査方向xに沿って配列されており、上記読取対象からの反射光を受光する複数のセンサICチップ3と、を備えたイメージセンサモジュールA1であって、光源装置2は、光源基板20と、この光源基板20に実装された光源とを備えており、光源基板20と基板1とは、複数のリード7を介して固定されている。

(もっと読む)

イメージセンサモジュール

【課題】光源装置を基板に対して適切に取り付けることが可能なイメージセンサモジュールを提供すること。

【解決手段】基板1と、光源装置2と、導光体4と、複数のセンサICチップ3と、を備えたイメージセンサモジュールA1であって、光源装置2は、主走査方向xおよび副走査方向yのいずれにも直角である方向に延びる部分を有する複数の端子22を有しており、基板1には、その主走査方向x一端から突出する複数ののリード7が固定されており、各端子22と各リード7とは、互いに接合されている。

(もっと読む)

単一の複合アセンブリに組み込まれるリモートコントロールレシーバデバイス、及び周辺光フォトセンサデバイス

【課題】RCレシーバデバイスと周辺光フォトセンサデバイスを省スペースで電子機器に組み込むことが可能な複合アセンブリを提供すること。

【解決手段】RCレシーバデバイスと周辺光フォトセンサ(ALPS)デバイスを単一のマウンティングデバイス(例えば、回路基板やリードフレーム基板)上に取り付け、それらが単一の複合アセンブリの一部を形成するようにする。その結果、アセンブリを電子機器に組み込んだときに消費される空間の量を低減することができ、電子機器のサイズを小型化することが可能になる。また、RCレシーバデバイスとALPSデバイスを単一の複合アセンブリ上で実施することで、複合アセンブリの製造、組み立て、及び出荷に関するコストも低減される。

(もっと読む)

光電変換センサ

【課題】光電変換素子の出力に含まれるオフセット出力を均一化することのできる光電変換センサを得ること。

【解決手段】光電変換部3は、3つの光電変換素子a,b,cの列「a,a’,a”」「b,b’,b”」「c,c’,c”」で構成されるが、各光電変換素子は同じ素子面積であり同じ容量値C1を有している。光電変換素子a,b,cを出力回路4に接続する配線5は、全て同じ形状・長さであり配線容量値C2は全ての配線5において同じである。出力回路4内の各駆動回路7で用いる電荷蓄積用の容量素子の値C3は全ての容量素子において同じである。比α{α=(C1+C2)/C3}は、全ての光電変換素子においてほぼ等しくなり各光電変換素子のオフセット出力は均一化される。出力回路4ではA/D変換範囲の基準レベルを統一した共通のA/D変換回路8を使用することができる。

(もっと読む)

画像取得システム及び方法

本発明による画像システム(imaging system)は、第1の行に存在する第1の画素と、前記第1の行に存在する第2の画素と、第2の行に存在する第3の画素と、ゲートドライバと、前記ゲートドライバから延びた第1の電気信号ラインと、前記第1の画素が接続された第2の電気信号ラインと、前記第3の画素が接続された第3の電気信号ラインとを備える。前記第3の画素と前記第1の画素は第1の列に存在する。前記第1の画素および第2の画素は前記第1の電気信号ラインに接続される。  (もっと読む)

(もっと読む)

受光モジュール

【課題】受光可能範囲を拡大することが可能な受光モジュールを提供すること。

【解決手段】受光素子2Aと、受光素子2Aを封止し、かつ受光素子2Aの正面に位置するレンズ4Aaが形成された樹脂パッケージ4Aと、を備える受光モジュールA1であって、受光素子2Bと、受光素子2Bを封止し、かつ受光素子2Bの正面に位置するレンズ4Baが形成された樹脂パッケージ4Bと、屈曲させられた状態で受光素子2Bおよび樹脂パッケージ4Bを樹脂パッケージ4Aに対して保持可能である連結部13と、をさらに備えている。

(もっと読む)

固体撮像装置および固体撮像装置の製造方法

【課題】固体撮像素子が形成された半導体層と、固体撮像素子を制御するロジック回路が形成された半導体層の双方の内部応力を打ち消すことで、双方の半導体層を張り合わせてなる基板の歪みを緩和することを可能とする。

【解決手段】固体撮像素子20が形成された第1半導体層11と、前記固体撮像素子を制御するロジック回路40が形成されたもので前記第1半導体層11と異なる結晶方位を有する第2半導体層31とを備え、前記第1半導体層11と前記第2半導体層31とが前記第1半導体層11と前記第2半導体層31との双方の内部応力を打ち消すように張り合わされている。

(もっと読む)

光電変換装置

【課題】低コストの下に短時間で製造することができ、かつ画像データを得ることができる光電変換装置を提供すること。

【解決手段】可視領域および紫外領域および赤外領域の波長の光を感知し電気信号に変換する光電変換装置であって、透明基板2上に、透明電極7と有機光電変換部と背面電極とを有する有機光電変換素子を複数配置すると共に、当該透明基板2上に、前記複数の有機光電変換素子に複数の読み出し配線15により接続された信号読み出し部18を配置して、光電変換素子から発生された電気信号を各画素ごとに選択的に読み出す構成とした。

(もっと読む)

イメージセンサ用半導体装置およびその製造方法

【課題】光半導体素子を含んだ複数の半導体素子を積層して搭載するイメージセンサ用半導体装置の放熱性能を高め、また半導体素子間の電気的な相互干渉を緩和する。

【解決手段】外部回路と接続するための導体1が設けられた凹状のパッケージ2内に、光半導体素子4,半導体素子3が積層して搭載され、パッケージ2の開口が光透過性蓋体6で封止されたイメージセンサ用半導体装置において、パッケージ2の内外に露出する熱伝導体8を備え、半導体素子4,半導体素子3間に熱伝導性板体9が配置され、熱伝導性板体9と熱伝導体8とが接続された構造とする。これにより、半導体素子3と光半導体素子4の双方から熱伝導性板体9と熱伝導体8とに順次に伝熱する、という高熱伝導率の伝熱経路が確保される。

(もっと読む)

放射線アレイセンサーの製造方法

【課題】大面積で、かつ、最適な成膜条件で作製される放射線有感層を有する放射線検出素子アレイを、低コストで提供する。

【解決手段】表裏両面もしくは裏面のみに電極3を形成したSi等の硬質導電性平板1の表面上に、CdTe、CdZnTe、GaAs、HgI2 等の半絶縁性化合物半導体膜4を、CVD、もしくは、蒸着等の気相成膜法を用いて形成する。次に、前記半絶縁性化合物半導体膜上に、複数個の信号取り出し電極5を形成し、所定のサイズに切り出して放射線検出素子アレイチップ6とする。

(もっと読む)

半導体装置、光電変換装置、これらの製造方法、及びマルチチップ型イメージセンサ

【課題】パッド部開口のためのエッチング除去工程と同一の工程でスクライブライン領域に沿ってエッチング除去を行なってもパッド部でのワイヤボンディング強度を確保でき、エッチング除去したパッド部の化合物の再付着を抑制して外観不良を低減する。

【解決手段】半導体装置は、半導体基板1201中に複数の半導体装置領域1102が形成され、各半導体装置領域1102の分割ライン領域であるスクライブライン領域1205に沿ってダイシングされる。このスクライブライン領域1205上の少なくとも一部には、スクライブライン領域1205を横切ってポリシリコン膜101が形成されている。半導体装置領域1102内には、MOSトランジスタが配置され、MOSトランジスタのゲート電極1207とポリシリコン膜101がともに半導体基板1102から同一のゲート絶縁膜を介して配置される。

(もっと読む)

イメージセンサ

【課題】 光電変換素子の出力である画像信号を平坦な波形とし、精度の高い画像情報の取り込みを可能とするイメージセンサをを提供する。

【解決手段】 本発明のイメージセンサは、入力する光信号を明度レベルに対応した電圧の電気信号に変換する光電変換素子と、光電変換素子に対応して設けられ、各光電変換素子の電気信号の出力部と共通出力線との間をオン/オフする選択スイッチと、入力されるパルスに従い、順次前記選択スイッチをオン/オフ制御する走査回路と、一方の入力端子から入力される前記電気信号と、他方の入力端子から入力される基準電圧との差電圧を増幅する差動増幅器と、電気信号が入力される、差動増幅器の一方の入力端子に一端が接続され、他端に基準電圧が入力された抵抗と

を有することを特徴とする。

(もっと読む)

放射線検出器および放射線画像検出装置

【課題】複数の放射線検出素子を基板上に隙間なく並設することができ、放射線検出のデッドスペースの発生を抑えて、分解能の高い放射線画像の検出可能にする。

【解決手段】第1の電極面23とこの第1の電極面23の反対側に位置する第2の電極面40とを有する放射線検出素子21が基板22上に搭載され、放射線検出素子21の第1の電極面23に導電性接着剤36を介して導電性シート37が接着され、この導電性シート37を介して、前記第1の電極面が前記基板32上の電気回路に接続されている。

(もっと読む)

放射線画像検出モジュールおよび放射線画像検出装置

【課題】放射線検出素子に対し、集積回路素子がはみ出さないような形態にモジュール化可能にし、放射線検出素子の隙間のない配列による画像の高解像度化、および大画面表示を実現可能にする。

【解決手段】放射線検出素子11と集積回路素子12を電気的に接続してなる放射線画像検出モジュールMであって、集積回路素子11における前記電気的な接続面側から該接続面側とは反対側の裏面側へ、電源供給用および信号引出し用の回路18を垂直方向に引き出す構成である。

(もっと読む)

放射線画像検出モジュール

【課題】放射線検出エリアの拡大および放射線画像の高解像度化を実現可能にする。

【解決手段】集積回路素子12の表面に位置する信号引出し用パッド16を、集積回路素子12と放射線検出素子11とがオーバラップする領域内に形成する。

(もっと読む)

放射線画像検出モジュールおよび放射線画像検出装置

【課題】集積回路素子と放射線検出素子とから構成される放射線画像検出モジュールを、基板上において前後左右の4辺方向に隙間なく連設可能にする。

【解決手段】信号処理回路19の配置エリア上に位置する信号処理側ピクセル電極パッド15を、信号処理回路19の配置エリア外の集積回路素子12上に延設される配線20を介して、該集積回路素子12における各ピクセル対応のピクセル信号処理回路21に出力する。

(もっと読む)

41 - 60 / 85

[ Back to top ]