Fターム[4M119FF03]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの形状又は作成方法 (789) | セルフアラインコンタクト (12) | 側壁形状を利用 (10)

Fターム[4M119FF03]に分類される特許

1 - 10 / 10

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

半導体メモリ

【課題】半導体装置のプロセスマージンを向上できる。

【解決手段】本発明の例の半導体メモリは、同一の配線層内に設けられる2つのビット線BL1,BL2と、メモリセルアレイ内に設けられるアクティブ領域AA2と、アクティブ領域AA2と交差する2つのワード線WL1,WL2と、ゲートがワード線WL1,WL2にそれぞれ接続されアクティブ領域AA2上に設けられる第1及び第2のトランジスタTr1,Tr2と、ビット線BL2とトランジスタTr1のソース/ドレインとに接続される第1の抵抗性記憶素子MTJ1と、ビット線BL2とトランジスタTr2のソース/ドレインとに接続される第2の抵抗性記憶素子MTJ2と、ビット線BL1と2つのトランジスタTr1,Tr2の共有ノードに接続され、ワード線WL1,WL2間に配置される配線層M2とを具備し、アクティブ領域AA2はメモリセルアレイの一端から他端まで延在する。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】セルサイズの微細化を図る。

【解決手段】磁気ランダムアクセスメモリは、第1の配線BLと、この第1の配線の上方に第1の配線と離間して設けられた第2の配線WWLと、第1及び第2の配線間に配置され、第1の配線の上面に接して配置され、固定層と記録層と非磁性層とを有する磁気抵抗効果素子MTJと、この磁気抵抗効果素子上に配置され、磁気抵抗効果素子と積層して一体に形成された金属層HMと、金属層、磁気抵抗効果素子及び第1の配線の側面に設けられたサイド絶縁膜24と、このサイド絶縁膜の側面と接して形成されたコンタクト26と、金属層及びコンタクト上に配置され、磁気抵抗効果素子とコンタクトとを電気的に接続する第3の配線WWLとを具備する。

(もっと読む)

磁気記憶装置の製造方法

【課題】磁気抵抗効果素子を含むメモリセルのサイズを縮小する。

【解決手段】磁気記憶装置の製造方法は、コンタクトプラグ13および第1の絶縁層11上に、磁気抵抗効果素子10を形成する工程と、上部電極層16上に、第1の方向に延在する第1のマスク層18を形成する工程と、上部電極層16を第1のマスク層18を用いてエッチングする工程と、上部電極層16および非磁性層15上に保護膜20を形成する工程と、保護膜20上に第2のマスク層21を形成する工程と、第2の方向に延在するように、第2のマスク層21上にレジスト層22を形成する工程と、第2のマスク層21をレジスト層22を用いてエッチングし、上部電極層16の側部に側壁部21Aを形成する工程と、非磁性層15および下部電極層14を、第2のマスク層21および側壁部21Aを用いてエッチングする工程とを含む。

(もっと読む)

磁気トンネル接合素子およびその形成方法ならびに磁気メモリセルおよびその製造方法

【課題】電気的な短絡を生じることなく安定した磁気情報の書込および読出をおこなうことのできる磁気メモリセルを提供する。

【解決手段】本発明の磁気メモリセルは、MTJ素子1と、これをその積層方向において挟んで対向するワード線21およびビット線31を備える。MTJ素子1は、最上層にキャップ層11を含むスタック10と、このスタック10の周囲を、端面10Tと接するように取り囲み、かつ、シリコン窒化物からなるスペーサ33と、このスペーサ33の周囲を取り囲むシリコン酸化物層51とを備える。キャップ層11の上面11Sは、シリコン酸化物層51の上面51Sよりもワード線21から離れる方向へ突き出している。スペーサ33によって短絡を抑制することができる。さらに、上面11Sとビット線31との確実かつ良好な接続を容易に可能とする構造となっている。

(もっと読む)

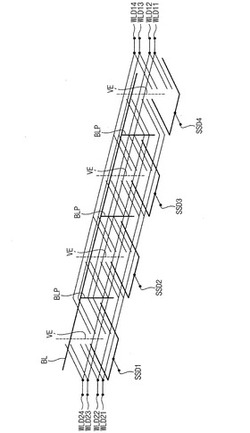

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]