Fターム[4M119FF07]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの形状又は作成方法 (789) | 配線層を貫通するコンタクト配線 (9)

Fターム[4M119FF07]に分類される特許

1 - 9 / 9

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

半導体記憶装置

【課題】セルトランジスタの電流駆動能力の劣化を抑制し、メモリセルごとの信号のばらつきを抑制し、かつ、微細化された半導体記憶装置を提供する。

【解決手段】メモリは、MTJを備える。アクティブエリアは、セルトランジスタごとに分離されており、セルトランジスタのゲートの延伸方向に対してほぼ直交する第1の方向に延伸している。アクティブエリアは、第1の方向に配列されてアクティブエリア列を構成している。第2の方向に隣接する2つのアクティブエリア列は、第1の方向に半ピッチずつずれて配置されている。アクティブエリアの表面上方から見たときに、MTJは各アクティブエリアの一端に重複するように配置されている。第1および第2の配線は、互いに隣接するアクティブエリア列のMTJに交互に重複するように第1および第2の方向に対して傾斜する方向に折り返しながら延伸している。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】コンタクト電極と配線とを安定して接続する。

【解決手段】実施形態の半導体装置は、平面形状がリング状の第1のコンタクト部41を有する第1の配線40と、第1の配線40より下層に設けられる第2の配線50と、コンタクト部41のリング状の部分を貫通して、2つの配線40,50を電気的に接続するコンタクト電極60とを含み、基板11上に設けられる配線領域を具備する。

(もっと読む)

半導体装置

【課題】内部回路の動作パラメータなどの設定を行うデータを長期にわたって安定に供給する。

【解決手段】第1の動作モード(PROM)時には、不揮発性メモリセルに対し非破壊的に書換え可能な態様でデータを書込み、第2の動作モード(OTP)時には不揮発性メモリセルに対し、破壊的に書換え不可能な態様でデータを書込む。この不揮発性メモリセルは、記憶素子として、可変磁気抵抗素子を有し、可変磁気抵抗素子の抵抗値に応じて情報を不揮発的に記憶する。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】セルサイズの微細化を図る。

【解決手段】磁気ランダムアクセスメモリは、第1の配線BLと、この第1の配線の上方に第1の配線と離間して設けられた第2の配線WWLと、第1及び第2の配線間に配置され、第1の配線の上面に接して配置され、固定層と記録層と非磁性層とを有する磁気抵抗効果素子MTJと、この磁気抵抗効果素子上に配置され、磁気抵抗効果素子と積層して一体に形成された金属層HMと、金属層、磁気抵抗効果素子及び第1の配線の側面に設けられたサイド絶縁膜24と、このサイド絶縁膜の側面と接して形成されたコンタクト26と、金属層及びコンタクト上に配置され、磁気抵抗効果素子とコンタクトとを電気的に接続する第3の配線WWLとを具備する。

(もっと読む)

磁気メモリセル、磁気ランダムアクセスメモリ、半導体装置及び半導体装置の製造方法

【課題】MRAMにおける書き込みディスターブを抑制しながら、高集積化を促進可能な磁気メモリセルを提供する。

【解決手段】トランジスタTR1、TR2と磁気抵抗素子群2とを具備する磁気メモリセルを用いる。TR1は、ゲートをワード線WL1に、第1ソース・ドレインをビット線BL1に接続される。TR2は、ゲートをワード線WL1に、第3ソース・ドレインをビット線BL2に接続される。磁気抵抗素子群2は、書き込み電流の通過する導電部が互いに直列又は並列に接続された複数の磁気抵抗素子MTJを備え、導電部の一方をTR1の第2ソース・ドレインに、他方をTR2の第4ソース・ドレイン電極に接続され、複数の磁気抵抗素子MTJにおける一方を導電部に、他方をワード線WL2に接続され、複数の磁気抵抗素子MTJの磁化の向きの組み合わせで情報を記憶する。複数の磁気抵抗素子MTJは、互いにその抵抗値が異なる。

(もっと読む)

他の種類の回路と共に集積されたMRAM装置

磁気抵抗ランダムアクセスメモリ(MRAM)(13)が、他の回路種(12)と共に埋め込まれている。演算装置のようなロジック(12)が、MRAM(13)と共に埋め込むのに特に適した回路種である。埋め込みを効率的に行うには、金属層(26)を他の回路(12)の相互接続部の一部として用い、更にMRAMセル(13)の一部として用いる。MRAMセル(13)は全て、プログラム線によって書き込まれる。プログラム線は、2本の線であり、交差して書き込むセルを規定する。このように、金属線(26)の共通使用があり、MRAMのプログラム線の一方に用いられ、更にロジック(12)の相互接続線の一方に用いられるので、設計が簡略化される。  (もっと読む)

(もっと読む)

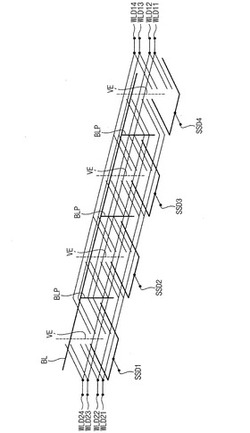

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

1 - 9 / 9

[ Back to top ]