Fターム[4M119JJ18]の内容

MRAM・スピンメモリ技術 (17,699) | 製造方法 (929) | 加工方法 (452) | 側壁形状マスクを用いた加工 (34)

Fターム[4M119JJ18]に分類される特許

1 - 20 / 34

磁気抵抗素子の製造方法

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】書き込み電流の低減およびリテンション特性の向上を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ可変である第1磁性層31と、前記第1磁性層上に形成されたトンネルバリア層32と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ不変である第2磁性層40と、を具備する。前記第2磁性層は、垂直磁気異方性の起源となる本体層34と、前記トンネルバリア層と前記本体層との間に形成され、前記本体層よりも高い透磁率を有し、前記本体層よりも大きい平面サイズを有する界面層33と、を備える。前記本体層の側面に、前記本体層よりも高い透磁率を有するシールド層90が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】記録層に作用する参照層からの漏洩磁界を低減しつつ、トンネルバリア層の絶縁不良を低減する。

【解決手段】実施形態による磁気ランダムアクセスメモリは、膜面に垂直方向の磁気異方性を有し、磁化方向が可変である記録層18と、膜面に垂直方向の磁気異方性を有し、磁化方向が不変である参照層16と、記録層及び参照層間に設けられた第1の非磁性層15と、をそれぞれ具備する複数の磁気抵抗素子10を備え、記録層は、複数の磁気抵抗素子毎に物理的に分離され、参照層及び第1の非磁性層は、複数の磁気抵抗素子を跨いで連続的に延在する。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、MTJ素子がコンタクトプラグ内のシームまたはボイドの影響を受けることなく、MTJ素子の特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数のセルトランジスタは、半導体基板上に設けられている。コンタクトプラグは、隣接するセルトランジスタ間に埋め込まれ、該隣接するセルトランジスタ間にある拡散層に電気的に接続されている。層間絶縁膜は、複数のコンタクトプラグ間を埋め込む。記憶素子は、コンタクトプラグの上方に設けられておらず、層間絶縁膜の上方に設けられている。側壁膜は、記憶素子の側面の少なくとも一部を被覆し、半導体基板の表面上方から見たときに、コンタクトプラグに重複するように設けられている。下部電極は、記憶素子の底面と層間絶縁膜との間、および、側壁膜とコンタクトプラグとの間に設けられ、記憶素子とコンタクトプラグとを電気的に接続する。

(もっと読む)

エッチング装置及び半導体装置の製造方法

【課題】難エッチング材料を、高速、高精度及び低ダメージでエッチングする。

【解決手段】実施形態に係わるエッチング装置は、上面側に披処理基板19が搭載されるステージ11と、ステージ11の上面側を覆うチャンバー12と、ステージ11の下面側に付加され、開口部を有する下部電極13aと、チャンバー12内にエッチングガスを供給するガス供給部14と、下部電極13aに高周波を印加することにより、チャンバー12内のエッチングガスをプラズマ化する高周波電源部17と、下部電極13aの開口部を介して被処理基板19にマイクロ波を印加することにより、披処理基板19の温度を最適範囲内に設定するマイクロ波発生部15と、ガス供給部14、高周波電源部17及びマイクロ波発生部15を制御する制御部18とを備える。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体記憶装置

【課題】安定した特性の磁気抵抗効果素子を有する半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、複数の磁気抵抗効果素子を有し、この各磁気抵抗効果素子は、半導体基板上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第2の磁性層と、からなる積層構造を有し、保護膜を介して各磁気抵抗効果素子の側壁を覆うように設けられ、且つ、磁気抵抗効果素子に対して、磁化容易軸に沿った方向に引張応力を与える側壁膜を備え、側壁膜のうちの第1の磁性層を覆う部分は、側壁膜のうちの第2の磁性層を覆う部分と比べて厚い。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

抵抗変化メモリ

【課題】セルサイズの微細化が可能な抵抗変化メモリを提供する。

【解決手段】抵抗変化メモリ10は、第1の方向に延在する複数のワード線と、第2の方向に延在する第1乃至第3のビット線と、第1及び第3のビット線に接続された複数の可変抵抗素子20と、半導体基板30内に設けられ、かつ斜め方向に延在する複数のアクティブ領域AAと、複数のアクティブ領域AAに設けられた、かつ可変抵抗素子20に接続された複数の選択トランジスタ21と、選択トランジスタと第3のビット線とを接続する複数のコンタクトプラグ37とを含む。複数の可変抵抗素子20は、第2の方向に並ぶようにして、第1のビット線の下方かつ複数のワード線間のそれぞれに配置された第1の可変抵抗素子群と、第2の方向に並ぶようにして、第3のビット線の下方かつ複数のワード線間のそれぞれに配置された第2の可変抵抗素子群とからなる。

(もっと読む)

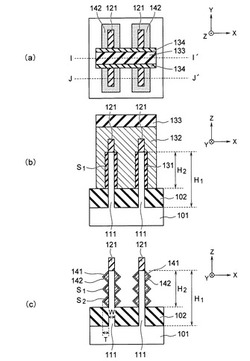

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

磁気スタックおよびメモリセル、ならびにセルを製造する方法

【課題】データ記憶装置における増加された記憶容量をもたらし得るより小さい全体セル厚さを提供する。

【解決手段】STRAMセルのような、不揮発性メモリセルについての装置および関連する方法が開示される。さまざまな実施形態に従えば、磁気自由層は、非磁気スペーサ層によって反強磁性層(AFM)から横方向に分離されるとともに、磁気トンネル接合によって合成反強磁性層(SAF)から内側に分離される。AFMは、磁気トンネル接合を超えて横方向に伸延するSAFのピニング領域との接触を通じて、SAFの磁化を固定する。

(もっと読む)

磁性メモリの製造方法

【課題】メモリセルに含まれる強磁性体膜の酸化を抑制しながら、磁性メモリのメモリセルを形成する技術を提供する。

【解決手段】磁性メモリの製造方法は、金属強磁性体により磁性体膜6を基板1の上面側に形成することと、無機物により磁性体膜6の上面に接触する無機物膜7、8を形成することと、無機物膜7、8の上面に、レジストによりレジストパターン9を形成することと、レジストパターン9をマスクとして無機物膜7、8をエッチングし、マスクパターン7’、8’を形成することと、レジストパターン9を除去することと、レジストパターンが除去された後、マスクパターン7’、8’をマスクとして磁性体膜6をエッチングすることとを備えている。磁性体膜6のうちマスクパターン7’、8’と接触する接触部分は、レジストパターンの除去の際に露出されず、酸化されにくい。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを構成する上部の導電要素と下部の導電要素との短絡を抑制することが可能な半導体装置、およびその製造方法を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に位置する、ピン層MPLと、トンネル絶縁層MTLと、フリー層MFLとを含む磁気トンネル接合構造MRDと、磁気トンネル接合構造MRDの下側側面に接する下側絶縁層III1と、下側絶縁層III1上に位置して磁気トンネル接合構造MRDの上側側面に接し、かつ磁気トンネル接合構造MRDの上面を露出する側壁絶縁層III2と、側壁絶縁層III2から露出する磁気トンネル接合構造MRDの上面に接する導電層BLとを備えている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタの拡散層に電気的に接続されたコンタクトプラグと、コンタクトプラグ上に形成され、上面がスイッチングトランジスタの上面よりも高い位置にある上部コネクタと、上部コネクタの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

1 - 20 / 34

[ Back to top ]