Fターム[5B001AB03]の内容

Fターム[5B001AB03]の下位に属するFターム

予測 (2)

Fターム[5B001AB03]に分類される特許

1 - 20 / 43

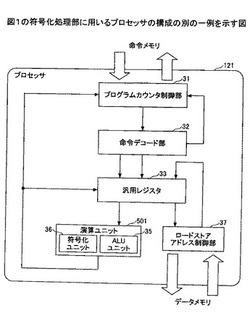

プロセッサ

【課題】高速に符号化処理を実行可能なプロセッサを提供する。

【解決手段】プロセッサは、演算論理ユニットと、XOR回路及びAND回路を含む符号化ユニットと、第1命令のデコード結果に応じて演算論理ユニットを制御して演算処理を実行させると共に、第1命令とは別の第2命令のデコード結果に応じて符号化ユニットを制御して再帰的畳み込み符号化処理を実行させる命令デコード部と、演算論理ユニットにより実行する演算処理のオペランドを格納するとともに、符号化ユニットにより実行する符号化処理に用いるデータ及びパラメータを格納するレジスタとを含む。

(もっと読む)

情報処理装置および情報処理方法

【課題】冗長ビットのビット長を抑制しつつ誤り訂正・検出の精度を向上させる。

【解決手段】誤り検出・誤り訂正を行う誤り制御を実現するための情報処理装置は、情報ビット列を取得する情報ビット列取得部と、情報ビット列に基づき、所定の符号を用いた符号化により、情報ビット列全体の誤り制御を実行可能な冗長ビット列を生成して、情報ビット列と冗長ビット列とを含む符号語を生成する符号化部とを備える。符号化部は、冗長ビット列に含まれる少なくとも1つのビットのそれぞれが、情報ビット列を複数に分割したビット列であって情報ビット列における連続した複数のビットにより構成されるビット列である分割情報ビット列の1つに対するパリティビットとしても機能するように、冗長ビット列を生成する。

(もっと読む)

情報伝送装置

【課題】安全性が要求される鉄道保安システムにおいても安全性を維持して誤り訂正符号を導入して情報を伝送してシステムの稼働率は向上させる。

【解決手段】地上装置1の送信機5は、入力した送信データに誤り訂正符号を付加して送信語を生成して通信路8に送信する。車上装置3の受信機6は、通信路8から受信した受信語に対してシンドロームを計算し、計算したシンドロームを用いて受信語の誤り訂正処理を行う。また、計算したシンドロームを用いて誤り訂正の状況を評価し、誤り訂正の状況があらかじめ設定された基準状態より良好な場合に誤り訂正処理をした受信データの出力を許可し、誤り訂正の状況があらかじめ設定された基準状態より悪くなっているとき誤り訂正処理をした受信データの出力を禁止する。

(もっと読む)

ポイズン・ビット・エラー検査コード手法

一実施例では、方法は、イベントの生起及び非生起の何れかを判定する工程であって、生起及び非生起の何れかがイベント判定をもたらす工程と、イベント・ビットを有するコードを処理する工程であって、上記処理は、イベント・ビットがイベント判定に対応するかを判定することにより、判定及びコードに応じる工程と、イベント・ビットがイベント判定に対応しない場合、イベント判定に対応するポイズン・ビットを生成するようコードをコード化する工程とを提供する。  (もっと読む)

(もっと読む)

分散的な記憶及び通信

a)データを複数のデータサブセット(A,B)に分割し、b)複数のデータサブセット(A,B)からパリティデータ(P)を生成することで、前記複数のデータサブセットのうちの1つ又は複数のデータサブセットが、残りデータサブセットとパリティデータ(P)とから再生成されるようにすることにより、データを記憶、検索、送信、又は受信する。ステップaとbとが、前記複数のデータサブセット及び前記パリティデータの各々に対して繰り返されることにより、更なるデータサブセットと更なるパリティデータとが生成され、d)前記更なるデータサブセットと前記更なるパリティデータとが別々の記憶場所(380)に記憶されるか、又は送信される。 (もっと読む)

符号化装置および方法

【課題】符号化に係る処理を高速化する。

【解決手段】組み合わせ回路253では、(NK)段レジスタ251の上位2pシンボルから逐次qj(x2p)の係数を得て、これらの2p個の係数と生成多項式を乗算した値を、レジスタ出力および新たな2p個の情報シンボルからなる値より減算することによって、次のレジスタ入力値に用いる。レジスタから得られる2pシンボル分の係数qj(x2p)は同時に得られるため、係数と生成多項式の乗算は同時に行なうことができる。本発明は、符号化を行う装置のパリティを生成する回路に適用することができる。

(もっと読む)

データ完全性検証メカニズム

【課題】データの完全性を保守するための方法および装置が提供される。

【解決手段】ある局面の方法に従うと、物理的なチェックサム計算がデータブロック上で行なわれる(404)。物理的なチェックサム計算を行なった後、論理チェックが、データブロック内に含まれるデータ上で行なわれる(406)。データブロックが論理チェックをパスすると、データブロックは不揮発性メモリに書込まれ得る(410)。その後、データブロックが不揮発性メモリから読出されると、物理的なチェックサム検証手順がデータブロック上で行なわれて(412)、データブロック内に含まれるデータ上で論理チェックが行なわれた後にデータブロックが破損したかが判断される。

(もっと読む)

エラー検出コード生成装置および方法

【課題】エラー検出コードの生成に必要な時間を短縮できるようにしたエラー検出コード生成装置および方法を提供する。

【解決手段】仮想DBI(Data Bus Inversion)情報とデータを用いて仮想エラー検出コードを生成するエラー検出コード生成部と、およびエラー検出コードの生成に関わるデータ数の偶数又は奇数のうちのいずれか1つを定義する偶数/奇数情報、前記偶数/奇数情報と連関するDBI情報、および前記仮想エラー検出コードを用いて前記エラー検出コードを生成するエラー検出コード再生成部を備える。

(もっと読む)

符号化装置、暗号化装置及びプログラム

【課題】CPUの演算能力を効率よく利用できる符号化装置を提供する。

【解決手段】係数データ5を格納する係数テーブル格納部6と、情報シンボル11のビット数の整数倍のビット幅を有するレジスタ1a〜1dと、情報シンボル11をレジスタ1a〜1dに入力するデータ入力部9と、レジスタ1dからデータを出力するデータ出力部2と、データ出力部2によりレジスタ1dから出力されたデータに基づいて、レジスタ1a〜1dに格納される情報シンボル11の符号化に用いる係数データ5を指定するアドレス指定部4と、アドレス指定部4により指定された係数データ5とレジスタ1a〜1dに格納される情報シンボル11との排他的論理和の演算を行い、該情報シンボル11の符号化データを求める排他的論理和演算器3とを備える。

(もっと読む)

エラー検出装置及びエラー検出方法

【課題】 エラー検出機能の詳細な故障診断を行うことができるエラー検出装置を提供する。

【解決手段】 CPU I/F1100からメモリ1200に送られるデータ列に対するエラー検出データを生成するパリティビット生成部1301と、

エラー検出データに基づいて、メモリ1200から出力されるデータ列のエラーを検出するパリティチェック部1401と、データ列に対するエラー検出データとして、パリティビット生成部1301からのデータと、診断用のデータを送信するCPUから送られてくるデータとを切り替えて出力する選択回路1302と、選択回路1302がCPUから送られてくるデータを出力する状態にあるときに、選択回路1302から出力されたエラー検出データに基づいて、パリティビット生成部1301とパリティチェック部1401の少なくとも一方を含むエラー検出機能の故障診断を行うことを特徴としている。

(もっと読む)

復号装置及び復号方法

【課題】Log−MAPの訂正能力の劣化を低減することができる復号装置及び復号方法を提供すること。

【解決手段】復号装置は、受信データと外部情報からLog−MAPアルゴリズムにおけるブランチメトリックを算出するBM計算部11と、ブランチメトリックに基づきパスメトリックの最大値を算出するACS演算部12と、パスメトリックのヤコビアン補正値を算出する補正項計算部13と、受信データの大きさに基づきヤコビアン補正値の値を調整して最大値に加算することで当該パスメトリックを補正する補正演算部14とを有する。

(もっと読む)

誤り訂正方法

【課題】2次元符号のホログラムメモリ記録再生装置において、符号化効率を改善できる誤り訂正方法を提供する。

【解決手段】所定数の2次元符号語に対して、各符号語の同じ位置に存在するビットをそれぞれ1つのビット列として抽出し(ステップ101)、前記2次元符号語ブロックに対して1つのビット列を除いた残りの各ビット列毎に誤り訂正符号化を行い複数のパリティビットを生成し(ステップ102)、パリティビットに対応する2次元符号語を2次元符号復調して前記複数のパリティビットを生成し、前記複数のパリティビットを用いて前記2次元符号語ブロックの前記誤り訂正符号化されたビット列の誤り訂正を行い、その結果に基づき前記誤り訂正符号化ステップで前記誤り訂正符号化を行わなかったビット列に対して2次元符号化則を利用して誤り訂正を行う(ステップ203)。

(もっと読む)

プログラム可能なトレリス・デコーダおよび関連する方法

最尤シーケンス推定(MLSE)デコーダ(たとえばビタビ・デコーダ)のようなプログラム可能なデコーダが、複数のプログラム可能なトレリス・パラメータのためのプログラミング入力と、前記プログラミング入力に接続され、前記複数のプログラム可能なトレリス・パラメータに基づいて定義される少なくとも一つのトレリス構造を有するトレリス・デコーダを実装する、FPGAのようなプログラム可能なデバイスとを含みうる。前記複数のプログラム可能なトレリス・パラメータは、各トレリス段についてアクティブまたは非アクティブ状態となるトレリス段のためのトレリス接続性情報、トレリス枝遷移データ値およびトレリス枝遷移についてのメトリック・インデックスを含みうる。また、トレリス構造は逆状態(reverse-state)トレリス構造を含んでいてもよい。本プログラム可能型トレリス・デコーダは、畳み込み符号、トレリス符号化変調(TCM)、ISIチャネルおよびCPM波形をデコードできる。  (もっと読む)

(もっと読む)

光集線装置および光加入者装置

【課題】G−PONの下り信号のFECフレームサイズは255と120の2通りであり、FECフレームサイズが異なっても、同じエラー訂正符号で処理可能な光集線装置および光加入者装置を提供する。

【解決手段】光電変換部とPON送受信部と物理層とからなり、PON送受信部は、短縮補償パラメータテーブルと該短縮補償パラメータテーブルを参照して補償後データを演算する短縮補償計算部とを含む誤り符号訂正符号エンコーダを含む光集線装置または光電変換部とPON送受信部と物理層とからなり、PON送受信部は、短縮補償パラメータテーブルと該短縮補償パラメータテーブルを参照して補償後データを演算する短縮補償計算部とを含む誤り符号訂正符号エンコーダを含む光加入者装置により、解決できる。

(もっと読む)

符号化装置及び復号化装置

【課題】新たな装置を追加することなく、LDPC符号とRS符号とを連接符号化することができる符号化装置及びこの符号化装置で符号化されたデータを復号化する復号化装置を提供すること。

【解決手段】符号化装置110は、RS符号で符号化するRS符号化部111と、RS符号化されたデータを一時的に保存するバッファ部112と、LDPC符号用の検査行列を生成する検査行列生成部113と、LDPC符号で符号化するLDPC符号化部114とを備え、検査行列生成部113は、情報部分行列HA及びパリティ部分行列HTを含む検査行列Hを生成し、検査行列Hの符号長N、情報長及びパリティ長を、それぞれ、RS(204,188)符号で符号化されたパケットのパケット長の所定整数倍の長さに設定する構成とした。

(もっと読む)

情報処理装置および情報処理方法

【課題】誤り制御において、冗長ビットのビット長を抑制しつつ、誤り訂正・検出の精度を向上させることを可能とする。

【解決手段】誤り検出と誤り訂正との少なくとも一方を行う誤り制御を実現するための情報処理装置は、情報ビット列を取得する情報ビット列取得部と、情報ビット列に基づき、所定の符号を用いた符号化により、情報ビット列全体の誤り制御を実行可能な冗長ビット列を生成し、情報ビット列と冗長ビット列とを含む符号語を生成する符号化部と、を備える。符号化部は、冗長ビット列に含まれる少なくとも1つのビットのそれぞれが、情報ビット列を複数に分割した分割情報ビット列の1つに対するパリティビットとしても機能するように、冗長ビット列を生成する。

(もっと読む)

異なるデータ保護方法間で切換えにおいてデータの完全性を維持する方法、装置及びプログラム

【課題】異なるデータ保護タイプ間の切換えにおいてデータの完全性を維持するための方法、装置及びプログラムを提供する。

【解決手段】データ及び第1の保護タイプ情報を受信し、第2の保護タイプ情報を発生し、第2の保護タイプ情報の発生後、第1の保護タイプ情報を用いてデータをチェックし、第1の保護タイプ情報のチェックの失敗を条件に、エラー表示を発生する。

(もっと読む)

エラー補正コードストライピング

【課題】ディジタルデータ内のエラーを検出および補正するのに必要な量のエラー補正コードデータを減少させ、しかも隣接するデータの大きいグループ内のエラーを補正する能力を維持する方法を開示する。

【解決手段】エラー補正コードの計算のために数学的にグループ化された記号間に空間的または時間的に距離を置く。

【効果】エラーは、1次元エラー補正コードのみを使用してエラーを容易に補正することができ、2次元プロダクトエラー補正コードの必要性、および列ECCデータが必然的にブロックに追加する追加のデータオーバヘッドはなくなる。

(もっと読む)

移動通信システムにおける伝送構成方法

【課題】情報ビットストリームが、物理層上で可変または多変データレート伝

送モードでインターリーバサイズにマッピングされる3GPP2通信システムに

おける伝送チェーン構成方法を提供すること。

【解決手段】物理層上で情報ビットストリームをデータレートにマッピングす

る過程で、3GPP2通信システムにおいて伝送チェーン構成する方法は、1/

コーディングレートの逆数値を有するターボコードと、コンボルーショナルコー

ドとの何れかで互いに異なるビットレートを有する情報ビットストリームをチャ

ネルコーディングする工程と、チャネル符号化したビットストリームが所望のイ

ンターリービングサイズより小さい場合に、符号化したビットストリームを繰り

返し、チャネル符号化したビットストリームが所望のインターリービングサイズ

より大きい場合に、パンクチャリングを行う工程とを備える。

(もっと読む)

二重化制御システム

【課題】バックボードバスの片側に異常が発生した場合でも、無駄なアクセスよるプロセッサ装置のパフォーマンス低下を防止した二重化制御システムを実現する。

【解決手段】二重化されたプロセッサ装置間の通信の異常検出を向上させた二重化制御システムに関するものである。2つのプロセッサ装置は、二重化されたシリアルバスにより接続され、制御演算及び相手側のプロセッサ装置とのアクセスを実行する上位コントローラと、シリアルデータの送信を制御する二重化された送信コントローラと、シリアルデータの受信を制御する二重化された受信コントローラと、受信データの正当性を診断する二重化された診断手段とを設けた。

(もっと読む)

1 - 20 / 43

[ Back to top ]