Fターム[5B005JJ01]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912) | 信頼性向上 (543)

Fターム[5B005JJ01]に分類される特許

1 - 20 / 543

ソフトエラー耐性調整機能を備えた電子システム装置及びソフトエラー耐性調整方法

半導体記憶装置

ホスト装置、システム、及び装置

複数の状態のプロセッサのための命令のキャッシング

不揮発性キャッシュメモリ、不揮発性キャッシュメモリの処理方法、コンピュータシステム

【課題】不揮発性メモリをキャッシュメモリとして使用する場合に、電力遮断状態での保持されているデータの信頼性を向上させる。

【解決手段】キャッシュデータの記憶に不揮発性メモリを用いる。この場合に、電力供給遮断の準備として、待機状態データを生成して不揮発性メモリ部上に記憶する待機準備処理を行う。また電力供給再開の際に、待機状態データを用いて不揮発性メモリ部に記憶されたキャッシュデータの復帰処理を行う。

(もっと読む)

情報処理装置およびメモリ管理装置の動作確認方法

【課題】仮想アドレスを物理アドレスに変換するメモリ管理装置が正常に動作しているか否かを確認可能とする。

【解決手段】情報処理装置1は、メモリ11と、メモリ11の物理アドレス又はそれに対応する仮想アドレスを指定することで、メモリ11の物理アドレスに対してデータの読み出し又は書き込みを行うためのシステムプログラムと、システムプログラムを実行するプロセッサ10と、プロセッサ10からのメモリ11に対する仮想アドレスを指定した読み出し及び書き込みにおいて、仮想アドレスを物理アドレスに変換するメモリ管理装置14を備える。プロセッサ10は、システムプログラムによって、物理アドレスを指定してデータの書き込みを実施した後、その物理アドレスに対応する仮想アドレスを指定してデータの読み出しを実施して、書き込んだデータと、読み出したデータが一致するか否かを判定する。

(もっと読む)

記憶装置および計算機

【課題】不揮発性メモリからキャッシュメモリへの書込回数を削減する。

【解決手段】記憶装置10は、不揮発性メモリ30とキャッシュメモリ20とメモリコントローラ12とを有する。不揮発性メモリ30は、分割データと格納場所を管理する論理/物理アドレス変換テーブル32を記録している。キャッシュメモリ20は、データキャッシュ21と、論理/物理アドレス変換テーブル32の一部を保持する論理/物理アドレス変換テーブルキャッシュ22を記録している。メモリコントローラ12は、外部からデータの読み出し要求を受けたとき、データキャッシュ21上に空きエントリが無かったならば、データキャッシュ21上の分割データのうち、論理/物理アドレス変換テーブル32のエントリが、論理/物理アドレス変換テーブルキャッシュ22に有るものを優先的に不揮発性メモリ30に退避して空きエントリを作成し、データを読み出す。

(もっと読む)

車載装置

【課題】ライトキャッシュメモリを有するハードディスク装置を用いる場合に、動作途中でエンジンが始動されても動作が長時間中断されることがなく、装置規模の拡大を最小限に抑えることができる車載装置を提供すること。

【解決手段】車載装置100は、ライトキャッシュメモリ34の使用/不使用を指定可能なハードディスク装置30と、製品マイコン部10と、ハードディスク装置30に動作電力を供給する電源回路60と、昇圧回路64が接続されており製品マイコン部10に動作電力を供給する電源回路62と、エンジン始動前にライトキャッシュメモリ34の不使用をハードディスク装置30に対して指示し、エンジン始動後にライトキャッシュメモリ34の使用をハードディスク装置30に対して指示するCM制御部としてのCPU12とを備えている。

(もっと読む)

データ制御方法およびシステム

【課題】 本実施例に係るバックアップ方法は、RAIDシステムが停電した場合であっても、バックアップユニットの電力容量を増やさずに、コントローラモジュールに搭載する揮発メモリが保持するデータを保証することを目的とする。

【解決手段】 本実施例に係るデータ制御方法は、コントローラが、揮発メモリに保持されたデータに基づいて該データの誤り確認用データを生成し、前記揮発メモリに保持されたデータを前記生成された誤り確認用データと共に不揮発メモリに転送し、前記不揮発メモリにおける指定の記憶領域への前記転送されたデータの書き込みの際にエラーが発生したとき、前記転送されたデータが復元可能な場合は前記不揮発メモリに転送された前記誤り確認用データの内容を変更し、前記転送されたデータが復元できない場合は前記指定の記憶領域にエラーがあることを示す情報を管理情報に記録する。

(もっと読む)

演算制御装置及び演算制御方法並びにプログラム、並列プロセッサ

【課題】並列プロセッサに対して、並列演算に伴う複数のメモリ間でのデータ移動について、ユーザコードの開発者の負担を減らすと共に、ユーザコードの可搬性を高める。

【解決手段】属性群格納部132は、各データブロックに対して夫々設定された属性群を取得して保持する。シナリオ決定部134は、これらの属性群と、並列プロセッサである演算ユニット140の構成を示す構成パラメータとに基づいて、最下位階層のメモリと、他の階層のメモリとの間での各データブロックの転送方式を決定し、決定した転送方式に応じて各データブロックの転送、及び該転送に対応する並列演算の制御を行う。属性群は、転送方式を決定するために必要である一方、並列プロセッサの構成に依存しない属性を1つ以上含む。ライトブロックの属性群は、該ライトブロックが既に他の階層のメモリに存在し、かつ、前記最下位階層のメモリに転送されると仮定して設定されたものである。

(もっと読む)

メモリ制御装置及びメモリ制御方法

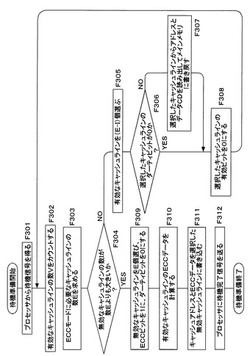

【課題】メモリアクセスにおいてECCの方式変更を自動的に行う技術を提供する。

【解決手段】バッファメモリと、このバッファメモリを単位データ毎にキャッシュするキャッシュメモリと、この単位データにバイトECCを付加する付加手段とを備えたメモリ制御装置。また、バッファメモリを備えたメモリ制御装置におけるメモリ制御方法であって、このバッファメモリを単位データ毎にキャッシュし、この単位データにバイトECCを付加するメモリ制御方法。

(もっと読む)

マルチコアプロセッサシステムおよびマルチコアプロセッサ

【課題】キャッシュの一貫性をソフトウェアで維持することができるクラスタ型のマルチコアプロセッサシステムを得ること。

【解決手段】メモリ領域は、1次キャッシュおよび2次キャッシュをともに使用する第1のアクセスによる読み書きが許可され、1つのタスクに独占的な使用権が与えられている第1の状態と、2次キャッシュのみ使用する第2のアクセスによる読み書きが許可され、1つのプロセスに独占的な使用権が与えられている第2の状態と、キャッシュを使用しない第3のアクセスによる読み書きが許可され、全てのプロセスに使用権が与えられている第3の状態とを容認する。カーネル部は、第1の状態から第2の状態に遷移させるとき、1次キャッシュを2次キャッシュにライトバックし、第2の状態から第3の状態に遷移させるとき、2次キャッシュをメモリ領域にライトバックする。

(もっと読む)

情報処理装置およびプログラム

【課題】2次ストレージへの書き込み頻度を下げて消費電力を下げる。

【解決手段】実施形態の情報処理装置は、補助記憶部と、主記憶部と、蓄電部と、第1書込部と、第2書込部と、を備える。主記憶部は、補助記憶部に記憶するデータを一時記憶するキャッシュ領域を含む不揮発性の記憶部である。第1書込部は、データをキャッシュ領域に書き込む。第2書込部は、蓄電部の電力量が予め定められた第1閾値より大きい場合に、キャッシュ領域に書き込まれたデータを補助記憶部に書き込む。

(もっと読む)

退避処理装置、及び、退避処理方法

【課題】複雑な処理を行わず、キャッシュメモリに蓄積中のデータの退避処理を可能とする。

【解決手段】キャッシュメモリの退避を行う第1の不揮発性メモリと、第2の不揮発性メモリと、キャッシュメモリ内のデータにおいて、第1の不揮発性メモリの書込が失敗した領域の情報の履歴を記録した管理テーブルを記憶する記憶部と、第1の不揮発性メモリへの退避処理を行う第1の制御部と、第1の制御部から送られてくる情報を、時間情報と共に、第2の不揮発性メモリへ書きこむ第2の制御部とを有し、第1の制御部は、停電発生時に、キャッシュメモリに記憶されているデータを不揮発性メモリに書き込む処理を実行し、前記退避処理に当たり、該書込が正常に行われたかを検証するとともに、該検証にて正常に書きこまれていない場合、前記不揮発性メモリの正常な書込ができなかった領域の情報を、記憶部に記憶する。

(もっと読む)

キャッシュコントローラ、キャッシュ制御方法及びデータ記憶装置

【課題】ハードエラーの発生に対する効率的な対処を実現し、キャッシュ動作の性能の劣化を抑制できるキャッシュコントローラを提供することにある。

【解決手段】実施形態によれば、キャッシュコントローラは、エラー検出訂正モジュールと、コントローラとを具備する。エラー検出訂正モジュールは、キャッシュメモリから読み出されたデータからエラーを検出し、当該エラーを訂正する。コントローラは、前記エラー検出訂正手段によるエラー訂正が不可能で前記エラーの種別がハードエラーの場合に、前記キャッシュメモリに対する電源遮断及び電源再投入の電源制御を実行する。

(もっと読む)

メモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラム

【課題】ストアイン方式のメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステムを提供すること

【解決手段】本発明のメモリシステムは、1stキャッシュメモリ10と1stキャッシュメモリ10に優先してプロセッサからアクセスされる1stキャッシュメモリ20と、1stキャッシュメモリ10においてキャッシュデータのリプレースを行う場合に、1stキャッシュメモリ10に格納されているキャッシュデータのうち、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、1stキャッシュメモリ20に格納されているキャッシュデータのうちリプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部4と、を備える。

(もっと読む)

情報処理装置及びエラー訂正支援方法

【課題】リプライデータに訂正不能なエラーが生じたことに起因するシステムの稼働率の低下を改善しつつ、回路規模の膨大化を回避する。

【解決手段】キャッシュミスのときに、メインメモリから出力されるリプライデータRD0に対して、訂正不能なエラーの有無を検出すると共に、該検出の結果とメインメモリとを示す付加情報を付加する。上記付加情報を含むリプライデータRD1でブロックロードする際に、該リプライデータRD1に含まれる付加情報を記憶しておく。キャッシュヒットのときにキャッシュメモリから出力されるリプライデータRD2に対して、ブロックロード時に記憶しておいた付加情報が「エラーがある」を示す場合に上記付加情報を付加する。上記付加情報が「エラーが無い」を示す場合に、訂正不能なエラーの有無を検出すると共に、該検出の結果とキャッシュメモリとを示す付加情報を付加する。

(もっと読む)

メモリ装置の診断方法及びメモリ装置の診断装置並びに情報処理装置

【課題】メモリ装置を備えた情報処理装置の、処理上のスループットを低下させることなく、かつ高い信頼性を維持して該メモリ装置の故障診断を行うこと。

【解決手段】

アドレス予測部11は、情報処理装置3を構成するCPU付属のメモリ装置に対し、メモリアクセスの状況(より具体的には、キャッシュラインが保持するキャッシュライン管理情報など)から判断して、近々に書き込みアクセスが発生することになると予測されるメモリのアドレス情報の特定を行う。次に、通達部12は、アドレス予測部11が特定した前記アドレス情報を、メモリ診断部に送出する。これにより、メモリ診断部は、CPU付属のメモリ装置(図示は省略)の、該特定されたアドレス情報が示す記憶領域のみを目下の診断対象とすることができる。

(もっと読む)

記憶装置及びその制御方法

【課題】バックアップ電源の疲弊に応じて機器の動作を変える技術を提供する。

【解決手段】記憶用メモリと、この記憶用メモリへのキャッシュを担うキャッシュメモリ

と、このキャッシュメモリへのキャッシュサイズを制御する制御手段と、電源断時のバッ

クアップを行うバックアップ手段とを備え、このバックアップ手段の疲弊に応じて前記制

御手段は前記キャッシュサイズを変える記憶装置。また、記憶用メモリと、この記憶用メ

モリのキャッシュを担うキャッシュメモリとを備え、電源断時のバックアップを行う記憶

装置の制御方法であって、この記憶装置にバックアップを行うバックアップ電源の疲弊を

予め測定し、この疲弊に応じて前記キャッシュメモリへのキャッシュサイズを調整する制

御方法。

(もっと読む)

メモリシステムおよびその動作方法

【課題】動作速度を低下させることなくシステムの信頼性を向上させることが可能なメモリシステムおよびその動作方法を提供する。

【解決手段】不揮発性メモリシステム2は、ブロック(ページ)単位でデータのアクセスが行われるNAND型フラッシュメモリ21(第1の不揮発性メモリ)と、ワード単位でデータのランダムアクセスが行われるNVRAM22(第2の不揮発性メモリ)と、NAND型フラッシュメモリ21およびNVRAM22の動作の制御を行うNVMコントローラ23(制御部)とを備えている。NVRAM22のデータに適用されるエラー訂正コードECC2が、NAND型フラッシュメモリ21内に保持されている。NVRAM22に対するアクセス速度の低下が回避されつつ、このNVRAM22におけるデータ保持特性が改善される。

(もっと読む)

1 - 20 / 543

[ Back to top ]