Fターム[5B005JJ12]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912) | 高速化 (1,154) | W/R動作の高速化 (909)

Fターム[5B005JJ12]の下位に属するFターム

ヒット率の向上 (342)

Fターム[5B005JJ12]に分類される特許

1 - 20 / 567

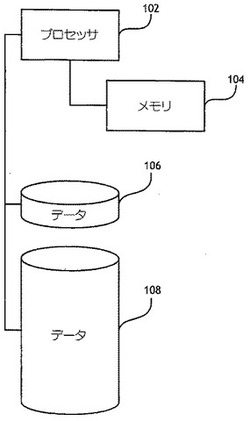

階層間の効率的なデータ移行を管理する装置

【課題】低速階層及び高速階層を有するデータストレージシステムにおいて、階層間でデータを効率的に移行させる。

【解決手段】高速データストレージデバイス106のリザーブスペースを備えている。プロセッサ102は、メモリ104に記憶されたリザーブスペーステーブルを参照して、低速データストレージデバイス108に記憶されたデータへのアクセスが高頻度となることによりホットデータとなると、該データを高速データストレージデバイス106のリザーブスペースに移し、該ホットデータを高速データストレージデバイス106上に保持する。データ移行は、一方向性であることが多く、データは低速階層から高速階層へ移行し、通常動作中のオーバーヘッドを低減することができる。

(もっと読む)

情報処理装置、ハイブリッド記憶装置、およびキャッシュ方法

【課題】記憶装置をHDDのキャッシュとして利用する場合に、アクセス性能の低下、およびキャッシュヒット率の低下を抑制すること。

【解決手段】実施形態によれば、ホストからのハードディスクドライブへのアクセス要求に対して、前記ハードディスクドライブの設定数以上の連続するセクタのデータにアクセスするかを判定する判定手段と、記憶装置を前記ハードディスクドライブのキャッシュとして用いるキャッシュ手段であって、前記設定数以上の連続するセクタのデータにアクセスすると判定された場合に前記記憶装置をキャッシュとして用いない、キャッシュ手段とを具備する。

(もっと読む)

情報処理装置

【課題】ネットワーク透過な単一レベル記憶を実現すること。

【解決手段】本発明の一つの実施形態によれば、情報処理装置は、第1メモリと、第2メモリと、仮想アドレス空間の少なくとも一部の仮想アドレスと前記第1メモリの物理アドレスとの対応関係を管理する変換情報を参照して、前記第1メモリにアクセスする制御部と、を備える。前記仮想アドレス空間には、他の情報処理装置に格納されたデータも割り当てられる。前記制御部は、アクセス対象データが前記他の情報処理装置に格納され手いる状態でページフォールトが発生した場合、前記他の情報処理装置に格納された前記アクセス対象データを前記第1メモリに格納するとともに、前記アクセス対象データに対応する仮想アドレスと前記第1メモリの物理アドレスの対応関係を前記変換情報に登録する。

(もっと読む)

マルチレベルのキャッシュ階層におけるキャストアウトを低減するための装置および方法

【課題】下位レベルキャッシュから置換されたキャッシュラインの上位レベルキャッシュへの割り当てを低減する方法を提供する。

【解決手段】置換ラインがすでに上位レベルに割り当てられと決定されたとき、置換されたキャッシュラインの割り当ては、次のレベルキャッシュにおいて防がれ、これにより、キャストアウトが低減する。そのような目的に、ラインは、下位レベルキャッシュ204において置換されるように選択される。上位レベルキャッシュ208において選択されたラインが存在するか示す選択されたラインに関連する情報が識別される。上位レベルキャッシュにおける選択されたラインの割り当ては、識別された情報に基づいて防がれる。選択されたラインの割り当てを防ぐことは、割り当てに関連するであろう電力を蓄える。

(もっと読む)

情報処理装置およびキャッシュ方法

【課題】コントローラに接続された第1の記憶装置をコントローラに接続された第2の記憶装置のリードキャッシュとして用いた場合に性能の低下を抑制すること。

【解決手段】実施形態によれば、情報処理装置は、コントローラと、キャッシュ手段とを具備する。コントローラは、第1の記憶装置および第2の記憶装置にコマンドを発行することによってデータの転送を行う。キャッシュ手段は、前記第1の記憶装置を前記第2の記憶装置のリードキャッシュとして用いる。キャッシュ手段は、前記コントローラが前記第1の記憶装置に対して設定数より大きい数のコマンドを発行している場合、キャッシュデータを前記第1の記憶装置に書き込むためのライトコマンドを、発行しているコマンド数が前記設定数以下になるまで前記コントローラへの発行を保留する。

(もっと読む)

記憶制御システムおよび方法、置換方式および方法

【課題】キャッシュ置換方法に関し、無駄なプリチャージを削減しメモリの消費電力を削減する。

【解決手段】DRAM100内のロウバッファ102は、メモリアレイ101から所定のデータ長を単位とするいずれかのデータを読み出して格納する。LLC206は、ロウバッファ102に記憶されたデータの一部をキャッシュデータとして抽出して記憶するキャッシュメモリである。MAC601において、LLC206の追い出し制御が実施される場合に、MRQ203のキューイング状態に基づいて近い将来ロウバッファ102にどのDIMMアドレスのデータが記憶されるかを予測する。MACにおいて、LLC上の追い出し対象範囲702のキャッシュデータデータの各物理アドレスをDIMMアドレスに変換する。変換された各アドレスと予測されたデータのアドレスとが一致した場合に、その一致アドレスに対応するキャッシュデータを優先してLLCから追い出す。

(もっと読む)

同時保留中データアクセスリクエストのためのデータハザード処理

【課題】イニシエータデバイスではなく、コヒーレンシコントローラでデータハザードを管理する、データ処理システムを提供する。

【解決手段】2つの部分形式で書き込みリクエストを処理する。同じアドレスに対し同時保留の読み出しおよび書き込みが存在する時、書き込みの第1の部分に応答しないことでコヒーレンシコントローラにより延期され、イニシエータデバイス10は、書き込みが保留中に関係なく、書き込みのアドレスに受信されたいずれのスヌープリクエストも処理するように進行する。保留中の読み出しが完了すると、コヒーレンシコントローラは、書き込みの第1の部分に応答し、イニシエータデバイスは、データおよびスヌープ後のデータの状態のインジケータを送信することによって、書き込みを完了する。コヒーレンシコントローラは、必要に応じてメモリを更新するためにこの情報を使用して潜在的なデータハザードも回避することができる。

(もっと読む)

画像形成装置および画像形成プログラム

【課題】 画像形成装置において、ファイルアクセスに非OS管理領域を使用することに起因するプロセッサーの負荷を軽減する。

【解決手段】 画像形成装置において、拡張I/O処理部34は、RAM内の非OS管理領域における、ユーザープロセス12からの指令により物理アドレスで指定された領域を使用して、ファイルシステム31上のファイルへのファイルアクセスを行う。

(もっと読む)

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

情報処理装置およびキャッシュ制御方法

【課題】演算速度が遅い制御部を用いても、アクセス速度の低下を抑制することが可能な情報処理装置のキャッシュ制御方法を提供すること。

【解決手段】実施形態によれば、情報処理装置は、記憶装置と、揮発性メモリと、プロセッサとを具備する。記憶装置は、制御部と、第1の不揮発性記憶部と前記第1の不揮発性記憶部よりアクセス速度が速い第2の不揮発性記憶部とを有する。プロセッサは、前記揮発性メモリにロードされた、オペレーティングシステムとキャッシュドライバとを実行する。キャッシュドライバは前記第2の不揮発性記憶部の少なくとも一部の領域を第1の不揮発性記憶部のキャッシュとして用いる。

(もっと読む)

プログラム生成装置、プログラム生成方法及びプログラム

【課題】コンパイル及びリンクによりプログラムを生成する際に、複数のメモリにおけるアクセス速度の違いを考慮した最適化を実現するプログラム生成装置、プログラム生成方法及びプログラムを提供する。

【解決手段】アクセス速度の異なる複数のメモリを有するコンピュータで動作されるプログラムを生成するプログラム生成装置であって、1回目のコンパイル及びリンクによりプログラムを生成し、そのプログラムをコンピュータ上で動作させた際のメモリに対するアクセスの監視結果と、複数のメモリのアクセス速度を示す情報とに基づいて、頻繁にアクセスされるデータを優先的にアクセス速度が速い方のメモリに配置するようにして、2回目のコンパイル及びリンクによりプログラムを生成することを特徴とする。

(もっと読む)

データ処理装置及びデータ処理方法

【課題】 データ処理の領域を分割して複数のプロセッサに並列処理させる際に、分割の最小単位を小さくする。

【解決手段】 データ処理装置が、第一のデータ処理を複数のプロセッサに並列処理させ、並列処理されたデータを記憶部に格納する際に、複数のプロセッサのデータキャッシュのサイズに基づいて記憶部のアドレスを変換して格納する。そして、記憶部に格納されたデータを読み出し、読み出したデータに対して第二のデータ処理を行う。

(もっと読む)

画像処理装置、画像処理システム及び画像処理方法

【課題】シングルポートのSRAMを用いて画像処理装置の処理効率を改善する。

【解決手段】画像処理装置10は、複数の変換前画素値を記憶するメインメモリ30と、複数のキャッシュブロックを有するキャッシュメモリ20とに接続される。カウンタと、座標決定部と、メモリコントローラと、キャッシュアクセス部と、画素値計算部と、出力部とを備える。メモリコントローラは、メインメモリ30に記憶された複数の変換前画素値をそれぞれ、変換前座標に応じたキャッシュブロックへ転送する。キャッシュアクセス部は、複数のキャッシュブロックから、変換後画素値の計算に必要な全ての変換前画素値を1回のキャッシュアクセスで読み出す。画素値計算部は、キャッシュアクセス部が読み出した変換前画素値を参照して、変換後画素値を計算する。出力部は、変換後画素値を出力する。

(もっと読む)

通信装置、通信プログラム、及び通信システム

【課題】サーバの処理負荷を削減でき、処理性能が向上する

【解決手段】送受信部と記憶部と抽出部と指示部と作成部とを備える。送受信部は、ネットワークを介してサーバへの要求メッセージを送信、及びサーバからの応答メッセージを受信する。記憶部は、複数の通信装置に割り当てられている識別子、及び通信装置の識別子を含む識別情報を記憶する。抽出部は、受信した応答メッセージから通知情報及びコマンドを抽出する。指示部は、抽出された通知情報に応じてコマンドを指示する。作成部は、通知情報に応じて識別情報を含む要求メッセージを作成する。

(もっと読む)

キャッシュシステムおよび処理装置

【課題】 動作が速い低消費電力なキャッシュシステムを提供する。

【解決手段】 本発明の実施形態によるキャッシュシステムは、揮発性キャッシュメモリーと、不揮発性キャッシュメモリーと、前記揮発性キャッシュメモリーに記憶される各データに対応付けて、その揮発性キャッシュメモリーに記憶されるデータよりも未使用時間の長い(もしくは短い)データが前記不揮発性キャッシュメモリーに記憶されている数に応じたデータを記憶する順序保存部と、前記揮発性キャッシュメモリーに記憶された第1のデータを他のアドレスを有する第2のデータで上書きするときに、前記第1のデータと対応付けて前記順序保存部に記憶されたデータに基づいて、前記第1のデータの未使用時間が前記不揮発性キャッシュメモリーに記憶されているいずれかのデータの未使用時間よりも短いと判断できる場合、前記第1のデータを前記不揮発性キャッシュメモリーに記憶させる制御部を有する。

(もっと読む)

キャッシュメモリおよびキャッシュシステム

【課題】キャッシュメモリの面積の増大を抑制しつつ、高速化する。

【解決手段】キャッシュメモリ2はタグメモリ103と、第1のダーティビットメモリ106と、有効ビットメモリ107と、データメモリ105と、を含む複数のキャッシュラインを有する複数のウエイを備える。また、キャッシュメモリ2は、前記キャッシュラインを特定するためのラインインデックスメモリ101を備える。また、キャッシュメモリ2は、前記ウエイを特定する第1のビットデータおよび前記ラインインデックスを特定する第2のビットデータを記憶するローメモリ202と、前記データメモリへのバイト単位のライトに対応したビット単位の第2のダーティビットを記憶する第2のダーティビットメモリ203と、登録された順番を規定するFIFO情報を記憶するFIFOメモリ204と、を含む複数のラインを有するDBLBシステム201と、を備える。

(もっと読む)

メモリ制御装置、メモリ装置、メモリ制御方法、及びプログラム

【課題】ライトバック処理の実行に起因して他の処理の処理速度が低下することを抑制することが可能な、新規かつ改良されたメモリ制御装置、メモリ装置、メモリ制御方法、及びプログラムを提供する。

【解決手段】主記憶部へのデータの書き込み又は読み出しと、キャッシュブロックを複数有するキャッシュ部へのデータの一時的な書き込み又は読み出しと、を実行するデバイスドライバと、前記主記憶部又は前記キャッシュ部へのファイルシステムのデータの書き込み又は読み出しを、前記デバイスドライバに命令する制御部と、を備え、前記制御部は、前記キャッシュブロックに記憶されているデータを前記デバイスドライバによって前記主記憶部に移動させるデータ移動処理を実行可能なタイミング情報を、前記デバイスドライバに通知する、メモリ制御装置。

(もっと読む)

リプレースメントデータメモリ装置、中央演算装置及びリプレースメントデータ処理方法

【課題】キャッシュ・ミス発生時の主記憶装置へのアクセス回数を低減する。

【解決手段】キャッシュメモリでリプレースメントが発生した時に主記憶装置にストアされるリプレースメントデータのうち前記リプレースメントの起因となったキャッシュミスに係る、前記キャッシュメモリのアドレスに記憶されていたデータのみを記憶し、別のキャッシュミスが発生した時に、該別のキャッシュミスに係るデータが自装置に記憶されているならば、自装置に記憶されている前記別のキャッシュミスに係るデータをロードデータとする。

(もっと読む)

メモリ制御装置

【課題】任意の数のアクセス装置に対して高いアクセス性能を提供し、任意のメモリ構成に対して高効率な制御を施し、さらに一貫性を保証しつつ柔軟なコンフィグレーションが可能なメモリシステムを提供すること。

【解決手段】SDRAMなどメモリバンクと同数もしくは整数倍のキャッシュを搭載し、バスマトリクスによってマスターのアクセスを並列かつ同時にキャッシュに分配し、メモリバンクに最適なキャッシュアクセスをスケジューリングし制御する。

(もっと読む)

並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラム

【課題】並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラムを提供する。

【解決手段】第1プロセッサの第1ローカル・キャッシュに関連する第1ローカル・キャッシュ・コントローラは、プログラム・コードを実行中の第2プロセッサによる第1キャッシュ・ラインの偽共有(false sharing)の発生を検出し且つ第2プロセッサによる第1キャッシュ・ラインの偽共有を許可する。第1キャッシュ・ラインの偽共有が発生するのは、第1ローカル・キャッシュ・コントローラによって第1ローカル・キャッシュ内の第1キャッシュ・ラインの第1部分を更新し、その後に、第2ローカル・キャッシュ・コントローラによって第2ローカル・キャッシュ内の第1キャッシュ・ラインの第2部分を更新する場合である。

(もっと読む)

1 - 20 / 567

[ Back to top ]