Fターム[5B005KK15]の内容

階層構造のメモリシステム (9,317) | 適用環境 (907) | 要求元 (807) | チャネル (96)

Fターム[5B005KK15]の下位に属するFターム

DMA (49)

Fターム[5B005KK15]に分類される特許

1 - 20 / 47

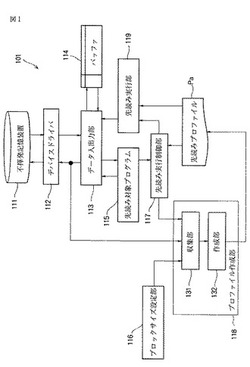

メモリ管理装置、メモリ管理方法、制御プログラム、および、記録媒体

【課題】適切なブロックサイズでデータの先読みを行う。

【解決手段】データ入出力部は、ページ単位で不揮発記憶装置からのデータの読み出しを要求し、読み出されたデータをバッファに記憶させる。プロファイル作成部は、先読み対象プログラムからの要求に従ってデータ入出力部により発行される不揮発記憶装置からのデータの読み出し要求の履歴を、先読みブロックサイズのブロック単位の読み出し位置およびサイズに変換した先読みプロファイルを作成する。先読み実行部は、先読みプロファイルに基づいて、不揮発記憶装置からバッファへの先読み対象プログラムのデータの先読みをデータ入出力部に要求する。本技術は、例えばメモリ管理装置に適用できる。

(もっと読む)

通信装置、通信方法、およびプログラム

【課題】ディスク記憶媒体のデータを、複数のサーバにインストールさせる作業に、長い時間を要しない通信装置を提供する。

【解決手段】通信装置5は、プロトコルシリアライザ10と、キャッシュコントローラ11とを備える。プロトコルシリアライザ10は、ディスク記憶媒体Kに記憶されたデータの読取要求を、サーバA1〜A3から受信するとともに、該受信した読取要求を、ディスク記憶媒体Kへの一つのアクセス権に係る命令にシリアライズする。キャッシュコントローラ11は、シリアライズされた読取要求の順序に従って、読取要求に係る要求データを、ディスク記憶媒体Kに記憶されたデータの中から取得する。また、プロトコルシリアライザ10は、キャッシュコントローラ11が取得した要求データを、該要求データに対応する読取要求の送信元サーバAに送信する。

(もっと読む)

仮想計算機システムにおけるメモリ割り当て方法

【課題】 アドレス変換機構を持ったIOデバイスを含む仮想計算機システムにおいて、IOデバイスのハードウェア上の制限を回避し、柔軟なゲストメモリ割り当てを可能とする。

【解決手段】 IOデバイス内のアドレス変換機構とチップセット内のアドレス変換機構を併用し、ゲスト物理アドレスからホスト物理アドレスへの変換を行う際には、仮想的なアドレスである仮アドレスを経由する。仮アドレスでゲストメモリ領域の分散を抑え、IOデバイス内のアドレス変換テーブルエントリを節約することで、フラグメント化によるゲストメモリ割り当て失敗を抑える。また、仮アドレスからホスト物理アドレスへの変換にチップセット内のアドレス変換機構を用いることで、仮想計算機に割り当てるメモリサイズを細かく指定できるようになる。

(もっと読む)

データ転送装置

【課題】PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、システム装置内の大幅な変更無しにスループットの向上が実現できるデータ転送装置を提供する。

【解決手段】チャネルから主記憶を参照する場合に、実際の主記憶参照と並行してプリフェッチ動作を行い、参照の対象となるデータを先行してキャッシュに登録する。本発明によれば、PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、データを先行してキャッシュに登録することでデータ転送のスループット低下を防止することができ、且つ主記憶内のデータ更新を反映することが可能なデータ転送装置を提供できる。

(もっと読む)

TLBサポート設計のIOMMU

【解決手段】

実施形態は、ページテーブルの構造及びフォーマットに依存しない改良されたトランスレーション挙動を有する入力/出力メモリ管理ユニット(IOMMU)のより小さくより単純なハードウエア実装を可能にする。実施形態はまた、デバイスに依存しない構造及び実装の方法を提供し、ソフトウエアのより大きな一般性を可能にする(より少ない特定のソフトウエアバージョンは同時に開発コストを低減する)。

(もっと読む)

キャッシュ制御装置及び方法

【課題】I/O状況の変化によってI/O性能が低下してしまうことを防ぐ。

【解決手段】アクセス元とストレージ装置とを有する計算機システムにキャッシュ制御装置が備えられる。その装置が、アクセス元からのI/Oコマンドに従うI/Oの状況を表す情報であるI/O状況情報を基に、アクセス元からのI/Oの性能が低下するか否かを判断する。その判断の結果が肯定的の場合、キャッシュ制御装置は、キャッシュ領域に関するキャッシュ使用状況を表す情報であるキャッシュ使用状況情報から特定されるキャッシュ使用状況をI/O性能が向上するようなキャッシュ使用状況に変更する。

(もっと読む)

システムコントロール装置、情報処理システムおよびアクセス処理方法

【課題】ローカルスヌープで処理できるケースを追加し、記憶装置へのアクセスを高速化

すること。

【解決手段】ローカルスヌープ制御部32は、キャッシュミスケースであってもリクエストの宛先がローカルの記憶装置である場合には、宛先アドレスをアドレスロック制御部33に登録してアドレスをロックし、メモリアクセス処理部36にメモリアクセスを実行させる。グローバルスヌープ制御部34は、ブロードキャストされたアクセス要求のうち、宛先がローカルの記憶装置であるものについてロック制御を行なう。

(もっと読む)

メモリ管理装置

【課題】不揮発性メモリへの高速アクセス性とキャッシュ構成の柔軟性とを高めたメモリ管理装置を提供する。

【解決手段】ストレージ30aとNVM60とからなるメモリ管理装置10は、NVM60に直接接続されてストレージ30a及びNVM60のDMA転送を制御するDMAコントローラ40を備え、DMAコントローラ40は、DMA転送がNVM60及びストレージ30aのいずれと行われるかを切り分けるDMA転送先切り分け機能部45と、NVM60にストレージ30aからキャッシュする情報を転送するディスクキャッシュ初期化機能部43と、NVM60にキャッシュされた情報を削除するディスクキャッシュ解放機能部44とを有する。これによりDMA転送時に転送対象が自動的に切り分けられてNVM60への高速アクセスを図り、NVM60の容量を可変にでき、キャッシュ構成の柔軟性を高める。

(もっと読む)

データ記憶システム

【課題】1台以上のHDDを備えてなるディスクシステム等のレスポンス性能を大幅なコストアップを招くことなく向上させることを実現したデータ記憶システムを提供する。

【解決手段】本ディスクサブシステムは、制御部21が、ホストシステム1から論理HDD22に格納されたデータの読み出しを要求された際、読み出し対象のデータが(論理HDD22よりも読み出し速度の速い)SSD23に格納されている場合、このSSD23に格納されているデータを読み出してホストシステム1に転送し、読み出し対象のデータがSSD23に格納されていない場合、当該読み出し対象のデータを論理HDD22から読み出してホストシステム1に転送すると共に、当該読み出したデータをSSD23に格納しておくリード制御手段を備える。

(もっと読む)

情報処理装置及びその制御方法

【課題】仮想メモリ領域を管理するオペレーティングシステムを実行する第1制御手段と第1制御手段と通信可能な第2制御手段を有する情報処理装置において、オペレーティングシステムにより管理される仮想メモリ領域の管理外の記憶手段に記憶されたデータ対して、第1制御手段が高速にアクセスする。

【解決手段】第1のCPU201は、キャッシュに対応する物理メモリの仕様情報を作成して第2のCPU221へ転送し(S904)、第2のCPU221は、その仕様情報に従って第1のCPU201が参照するキャッシュに対応する物理メモリ203に対して、デバイスに記録されているデータを転送する(S910)。

(もっと読む)

フラッシュキャッシュコマンドでキャッシュデータの完全性を保全する方法およびシステム

【課題】ディスクドライブの書込キャッシュおよびフラッシュキャッシュ領域間のデータの完全性を保全する。

【解決手段】 ディスクドライブ内の不揮発性記憶域は、ホストコンピュータからのフラッシュキャッシュコマンドの受信に伴い、書込キャッシュ100内にあるデータを保存するために利用される。後続のフラッシュキャッシュコマンドが所定時間内に発行されなければ、書込キャッシュ100内に存在し不揮発性記憶領域に保存されてディスク上の正当な領域にまだ書き込まれていないどのデータもディスク上の正当な領域に書き込まれることになる。

(もっと読む)

キャッシュメモリシステム及びキャッシュメモリの制御方法

【課題】データ保全性とキャッシュヒット率、及びフラッシュ効率を向上させるキャッシュメモリシステム、及びキャッシュメモリの制御方法を提供する。

【解決手段】空きのチャンクへ一旦データ書き込みを行い、データ転送に成功したチャンクのみをキャッシュ上のデータチャンクとすり替える。またチャンクヘッダにストレージ装置30上のアドレスと有効データサイズを記憶することにより、一部データが有効なチャンクもキャッシュ上に存在させる。更にはストレージ装置30にフラッシュする際の順序を、LBAオーダーのソートを行って決める範囲を限定する。

(もっと読む)

直列インターフェースバスにまたがってキャッシュコヒーレンシを維持するシステム及び方法

【課題】メモリに格納されたデータを使用して処理動作を実行する方法を提供すること。

【解決手段】この方法は、ローカルメモリに格納された第1データがデータキャッシュに格納された第2データに対して相対的にコヒーレントであるかどうかを判定するように構成されたスヌープ要求であって、バス上のデータキャッシュを識別する宛先情報と、データキャッシュ内で第2データが配置される場所を識別するキャッシュラインアドレスとを含むスヌープ要求を生成するステップと、スヌープ要求の、バスを介しての第2プロセッサへの送信ステップと、スヌープ要求からキャッシュラインアドレスの抽出ステップと、第2データがコヒーレントであるかの判定ステップと、完了情報を含む完了メッセージを生成するステップと、完了メッセージの、バスを介しての第1プロセッサへの送信ステップとを含む。

(もっと読む)

ブロック・アドレスの可能な大容量ストレージ・システムのためのインターフェイス

【課題】ストレージ装置(高分子強誘電性メモリ装置)のメモリのセルが現在の状態に刻印(imprinted)または膠着されるのを防止するためのリフレッシュ・サイクルを発行するシステムおよび方法を提供する。

【解決手段】ホスト制御インターフェイス(HCI)は、大容量ストレージに周期的なメモリ・リフレッシュ・サイクルを提供し、セルの状態が固定化されるのを防止する。時間に基づいたリフレッシュは、キャッシュ・ストレージ装置20,22,・・・,24,26中の高分子メモリ装置が現在の状態に「刻印される(imprinted)」または膠着されるのを防止する。HCI18は、電源投入時にすべてのアドレスを経由する最初のループを提供し、規則的な時間間隔で通常のアクセス時間の読み出しが後続し、電源オン中にセルが刻印されないことを保証する。

(もっと読む)

ストレージ装置及びその制御方法

【課題】ストレージシステムに制御モジュールを順次追加できるように設計されても、上位装置に対して、統一された制御資源として管理できるようにしたストレージ装置及びその制御方法を提供する。

【解決手段】複数の制御モジュールのそれぞれに存在する管理部のうち、複数のモジュールに対して統一的な管理を実行する管理部を設定し、この管理部に管理ユーザがアクセスし、管理ユーザがこの管理部を介して複数のモジュールを統一的に管理するようにした。

(もっと読む)

記録装置及びその制御方法

【課題】ディスク全面において一定のデータ転送速度を実現することができ、ディスクの内周側を使用して高速記録することを可能にする。

【解決手段】記録装置10は、ハードディスクアセンブリ(HDA)11と、フラッシュメモリ12と、キャッシュとして機能するSDRAM13と、これらのメディアを制御するハイブリッドコントローラ14と、ホストインターフェース15とを備えている。ハイブリッドコントローラ14は、HDA11やフラッシュメモリ12に対する書き込み/読み出し制御を個別に行う他、HDA11及びフラッシュメモリ12に一つの大容量データを分割記録するための制御機能を備えている。ハイブリッドコントローラ14は、記録データが所定のデータ量以上である場合にHDA11及びフラッシュメモリ12への分割記録を実行し、HDA11の記録位置がディスクの内周側に行くほどフラッシュメモリ12への分割記録の割合を高める。

(もっと読む)

メモリシステム

【課題】リセット要求を受けてから実際にリセット処理に移るまでに要する時間を従来に比して短縮することが可能なメモリシステムを提供する。

【解決手段】WC21を有するDRAM20と、ページ単位で読み出し/書き込みを行い、ブロック単位で消去を行うFS12と、トラック単位で読み出し/書き込みを行い、ブロック単位で消去を行うMS11と、FS12の入力バッファであるFSIB12aと、MSの入力バッファであるMSIB11aと、データの保存処理を行うコントローラと、を備え、MSIB11aは、WC21に書込まれたデータを保存するFSBB12acを有し、コントローラは、ホスト装置からのリセット要求を受けた場合に、WC21に書込まれたデータをFSBB12acに退避する。

(もっと読む)

記憶装置、情報端末装置及びデータ先読み方法

【課題】見掛け上のデータアクセス時間を短縮し、データアクセスに必要なシステム負荷を軽減することができるようにしたディスク装置及びデータの先読み方法を提供することにある。

【解決手段】データ読み出し命令を拡張して、コントローラ100がデータを読み出すだけでなく、HDD101内のキャッシュメモリ106へのデータの複製もコントローラが指示できるようにする。あわせて、キャッシュメモリ106におけるデータの有効期間の設定、最低限コントローラからのアクセスが発生しない時間の通知、用いるインターフェイスの指定を行えるようにすることで、HDD101内のデータの移動を直接制御可能にする。

(もっと読む)

ストレージ装置、データ回復方法及び計算機システム

【課題】容易且つ迅速にオリジナルデータを管理する論理ボリュームのデータを回復することのできる技術を提供する。

【解決手段】P−Vol10pのLU#と、S−Vol10sのLU#とを対応付けて記憶するLU管理テーブル61を備え、CPU53が、磁気テープ74へのデータの退避元のS−Vol10sのLU#を特定し、特定したLU#に対応付けられたP−Vol10pのLU#をLU管理テーブル61から取得し、磁気テープドライブ71により、データを格納した磁気テープ74から、退避されたデータを読み出させ、取得したLU#のP−Vol10pに、磁気テープ74から読み出したデータを格納させる。これにより、容易且つ適切にP−Vol10pにデータをリストアすることができる。

(もっと読む)

IPTVネットワークにおける最適なキャッシュ割当の方法およびシステム

IPTVネットワークでは、帯域幅要件を低減するために、ビデオコンテンツを記憶するための1つまたは複数のキャッシュがネットワークノードにおいて設けられ得る。キャッシュメモリの最適なサイズおよび位置を決定し、IPTVネットワークのユニキャストサービスに関するキャッシュメモリの最適な分割を決定するために、キャッシュ有効性やキャッシュ可能性などのキャッシュ関数を定義し、最適化することができる。  (もっと読む)

(もっと読む)

1 - 20 / 47

[ Back to top ]