Fターム[5B005KK22]の内容

階層構造のメモリシステム (9,317) | 適用環境 (907) | 要求元 (807) | 並行処理 (68)

Fターム[5B005KK22]の下位に属するFターム

パイプライン処理 (43)

Fターム[5B005KK22]に分類される特許

1 - 20 / 25

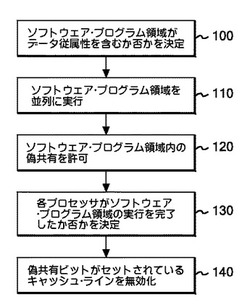

並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラム

【課題】並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラムを提供する。

【解決手段】第1プロセッサの第1ローカル・キャッシュに関連する第1ローカル・キャッシュ・コントローラは、プログラム・コードを実行中の第2プロセッサによる第1キャッシュ・ラインの偽共有(false sharing)の発生を検出し且つ第2プロセッサによる第1キャッシュ・ラインの偽共有を許可する。第1キャッシュ・ラインの偽共有が発生するのは、第1ローカル・キャッシュ・コントローラによって第1ローカル・キャッシュ内の第1キャッシュ・ラインの第1部分を更新し、その後に、第2ローカル・キャッシュ・コントローラによって第2ローカル・キャッシュ内の第1キャッシュ・ラインの第2部分を更新する場合である。

(もっと読む)

情報処理装置及びデータアクセス方法

【課題】メモリに格納されたストリームデータに対するアクセス効率を向上することができる情報処理装置及びデータアクセス方法を提供すること。

【解決手段】本発明にかかる情報処理装置は、ストリーム識別情報によって識別されるストリームデータを複数格納するメモリ2と、複数のストリームデータのストリーム識別情報に応じて、当該複数のストリームデータに割り当てられ、当該割り当てられたストリームデータをメモリ2から先読みする複数のチャネルユニット21、22、23、24であって、異なるストリーム識別情報によって示されるストリームデータに対して異なるチャネルユニットが割り当てられる複数のチャネルユニット21、22、23、24と、チャネルユニットが先読みしたストリームデータにアクセスするプロセッサ1と、を備える。

(もっと読む)

データキャッシュとメインメモリ間の一貫性の保証

プロセッサコア、複数のスレッドの各々によってアクセス可能なデータを記憶するキャッシュメモリ、複数のスレッドによってアクセス可能なデータを記憶するメインメモリ、非一貫性検出モジュール、及びメモリアービターを含み、複数のスレッドをサポートするマルチスレッドプロセッサにおいてメモリアクセスを制御するための装置を提供し、非一貫性検出モジュールは、プロセッサコアとメモリアービターの間に接続され、メモリアービターは、非一貫性検出モジュールとメインメモリの間に接続され、キャッシュメモリからメモリアービターに送信された読取及び書込要求に対する各スレッドのための個別の要求待ち行列が存在し、使用においては、非一貫性検出モジュールは、キャッシュメモリからメインメモリに送信された各書込要求に対するメモリアドレスの指示を書込アドレスメモリに記憶し、更に、キャッシュメモリから送信された各次の読取要求のアドレスを書込アドレスメモリ内の指示と比較し、次の読取要求のアドレスが指示に適合した場合に、読取要求に対応する障壁を適合指示が属するスレッドの要求待ち行列内に挿入し、メモリアービターは、対応する障壁がメモリアービターによって受信されるまで読取要求がメモリバスにアクセスしないように阻止する。 (もっと読む)

並列処理プロセッサシステム

【課題】 複数のプロセッサを備え、処理するデータを所定の単位に分割し、各データに対して、各プロセッサで並列に処理を行う構成において、命令キャッシュ容量を低減しながら所望のパフォーマンスを得る構成を提供する。

【解決手段】 並列処理プロセッサシステム203は、それぞれDSP301、命令キャッシュ302、画像用ローカルメモリ303を含む複数のプロセッサエレメント(PE1〜PE3)と、共有メモリ304とを備える。共有メモリには、DSPが実行するファームウェアが格納される。並列処理プロセッサシステムは、画像用ローカルメモリに処理対象の画像データを転送し、DSPにより画像処理を施す。キャッシュミスが発生した場合の命令キャッシュの更新は例えば、DSPがアクセスしたアドレスに対応する共有メモリの内容を命令キャッシュにコピーすることによって実現される。

(もっと読む)

メモリ管理装置、メモリ管理方法、および、プログラム

【課題】CPUリソースの配分が管理されたコンピュータシステムにおいて、ミッシングページ例外の発生頻度を抑える。

【解決手段】各仮想マシンの状態を監視し、各仮想マシンのCPU配分率の逆数を格納する仮想マシン監視手段と、ミッシングページが発生した仮想マシンのCPU配分率の逆数を取得して既定値との積または該積の定数倍を算出し、ページインされたページのカウンタ初期値として格納するカウンタ初期値設定手段と、ワーキングセットに含まれるページの参照または更新の有無を一定間隔で検査し、参照または更新があったページに対応する仮想マシンのCPU配分率の逆数を取得して既定値との積または該積の定数倍を該ページのカウンタ初期値として格納し、参照または更新がなかったページのカウンタから定数値を減算してカウンタが所定値になると該ページをページアウトさせるワーキングセット管理手段と、を備える。

(もっと読む)

プロセッサ

【課題】複数のプログラムを同時に実行するプロセッサにおいて、キャッシュミスによる影響をより効果的に抑える。

【解決手段】複数のプログラムを同時に実行するプロセッサにおいて、主記憶装置またはキャッシュから第1と第2のプログラムの命令語が読み出され、読み出された命令語は第1の記憶手段にキューイングされる。第2と第3の記憶手段は、それぞれ、第1と第2のプログラムに含まれる命令語の実行に要するサイクル数見積りのための実行サイクル数見積り情報を記憶し、第1と第2のキャッシュミス予測器は、それぞれ、実行サイクル数見積り情報をそれぞれ読み出す。命令語のスケジューリング位置は、この実行サイクル数見積り情報の内容に従って決定される。好ましくは、実行サイクル数見積り情報は、キャッシュミスの検出/非検出に応じて動的に変更される。

(もっと読む)

キャッシュメモリシステム、CPUコア及びキャッシュメモリ制御方法

【課題】本発明は、メモリアクセスのオーバーヘッドを削減すると共に、メモリやCPU、メモリにデータ供給する外部デバイス等の利用効率を上げ、システム全体の性能を向上させることの出来るキャッシュメモリシステム、CPUコア及びキャッシュメモリ制御方法を提供することを課題とする。

【解決手段】上位メモリデータ格納装置24は、CPUコア11が参照したデータが前記更新されるデータであるとき、更新されたデータを下位メモリ階層12から読み出し、上位メモリ階層15にデータを格納する。メモリロック装置23は、上位メモリ格納部24が上位メモリ階層15にデータを格納したとき、上位メモリ階層15をロックする。

(もっと読む)

分散型レベル1キャッシュシステム及び集中型レベル2キャッシュを有するシェーダ複合体

【解決手段】

シェーダパイプテクスチャフィルタは、レベル1キャッシュシステムを記憶の主要方法として用いるが、レベル2キャッシュシステムに対する読み出し及び書き込みを必要に応じてレベル1キャッシュシステムにさせる能力を有している。レベル1キャッシュシステムはワイドチャネルメモリバスを介してレベル2キャッシュシステムと通信する。また、レベル1キャッシュシステムは、デュアルシェーダパイプテクスチャフィルタを支持するように構成されてよい一方で、レベル2キャッシュシステムへのアクセスを維持する。レベル1キャッシュシステムを記憶の主要方法として用い、レベル2キャッシュシステムに対しする読み出し及び書き込みを必要に応じてレベル1キャッシュシステムにさせる能力を有する方法もまた提示される。更にレベル1キャッシュシステムは、他のリソースの間で共有可能に画定されるメモリ領域を割り当てることができる。

(もっと読む)

情報処理装置およびロード制御方法

【課題】割り込み信号が発生されてからプロセッサが割り込み要因に対応する処理ルーチンをコールするまでのタイムラグ中に割り込み要因に対応する処理ルーチンをキュッシュに効率よくロードすることができる情報処理装置を実現する。

【解決手段】ある割り込み要因(例えばINT3)が発生した時、割り込み制御部121は、割り込み信号INTを発生する。CPU11は割り込みハンドラの実行を開始する。キャッシュロード制御部123は、割り込み信号INTの発生を検出すると、発生した割り込み信号に対応する割り込み要因に関連付けられたアドレスを用いて、キャッシュ制御部122にロード要求を発行する。これにより、割り込み要因弐対応する処理ルーチンの命令群をメモリ13からキャッシュ202にロードする処理が、割り込みハンドラによる処理と並行して実行される。

(もっと読む)

マルチスレッドおよびマルチコア・システムのためのキャッシュ、および、その方法

一実施例に従って、本発明は一般にプロセッサのキャッシュの性能を改善する方法を提供する。本方法は、データ・ランダム・アクセス・メモリ(RAM)内に複数のデータを格納することを含む。本方法は、さらに、次のレベルのメモリ・サブシステムへ転送された全ての未処理の要求のための情報を保持することを含む。本方法は、さらに、要求が実行された後、サービスされた要求に関連する情報をクリアすることを含む。本方法は、さらに、後続の要求が、次のレベルのメモリ・サブシステムに既にインフライトしている1またはそれ以上の要求に提供されたアドレスと一致するかどうかを決定することを含む。本方法は、さらに、次のレベルのメモリ・サブシステムによってサービスされた実行済みの要求を、オリジナルの要求が次のレベルのメモリ・サブシステムへインフライトしていた間に要求を出した少なくとも1つのリクエスタと一致させることを含む。本方法は、さらに、各要求に特有の情報を格納することを含み、その情報は設定属性および経路属性を含み、設定および経路属性は、データが戻されると直ちに、戻されたデータがデータRAM内のどこに保持されるべきかを識別するために形成され、各要求に特有の情報は、さらに、スレッドID、命令待ち行列の位置、およびカラーのうちの1つを含む。本方法は、さらに、ヒットおよびミス・データの戻りをスケジュールすることを含む。もちろん、これ以外の様々な実施例も、本発明の範囲内である。  (もっと読む)

(もっと読む)

信号処理装置

【課題】マルチコアシステムを備えた信号処理装置の性能向上。

【解決手段】キャッシュ用の複数の第1メモリと、各ステージを実行するためのプログラム103H〜103I、第1メモリに記憶されたデータ及び前記各ステージプログラム103H、Iの起動の予約情報を記憶する第2メモリ103と、各ステージプログラム103H〜Lを起動することによって、第1メモリ又は第2メモリに記憶されたデータに対してインバリデート処理、信号処理及びライトバック処理を行うステージを実行する複数のプロセッサと、を備え、各プロセッサは、第1ステージにおいて、前記第2ステージプログラム103Iの起動の予約情報103B、Cを前記第2メモリに記憶し、第2ステージにおいて、前記第2メモリに記憶された予約情報103B、Cに従ってインバリデート処理又はライトバック処理を省略する。

(もっと読む)

ベクトル処理装置及びベクトル処理システム

【課題】プロセッサ−メモリ間のデータ転送遅延を抑制し、処理の迅速化を図る。

【解決手段】ベクトルプロセッサ31、32、…、3nとメモリ制御部41、42、…、4mとを備えるベクトル処理装置であって、ベクトルプロセッサ31、32、…、3nは、命令種別と、ベースアドレス、ディスタンス、及び要素数からなる命令内容とに基づいて、メモリアクセスに関する制御情報を生成するメモリアクセス制御部(制御情報生成回路9)33とを有してなるとともに、生成された前記制御情報に基づいて、キャッシュ登録有無、又は/及び登録サイズを切り替えるポートキャッシュ36とを有すると共に、前記メモリ制御部41、42、…、4mは、生成された前記制御情報に基づいて、キャッシュ登録有無、又は/及び登録サイズを切り替えるバンクキャッシュ44と、メモリアクセス単位を切り替えるメモリバンク44とを備えている。

(もっと読む)

複数制御装置からなるシステムにおけるシステムプログラムデータメモリアクセス方式

【課題】本発明は複数の制御装置からなるシステムにおけるシステムプログラムデータメモリ(SPM)アクセス方式に関し,SPMを備えたシステムの機能を拡張して制御装置を整数倍した場合に低コストでプログラムの改版時の更新動作を迅速に行うことを目的とする。

【解決手段】一定個数の制御装置により群を構成し,一つの群の1つまたはその予備を含む2つの制御装置にだけシステム内制御装置全体のソフトウェアを格納するSPMを設け,複数群の中のSPMを設けた制御装置及び他の各群のそれぞれの中の1つまたは2つの制御装置にSPMの一部のコピーを保持するキャッシュメモリを設ける。各群に属する複数の制御装置の間でデータを転送するグローバルバスを設け,キャッシュメモリを設けた各群の制御装置の間でデータを転送するシリアル・グローバルバスを設け,プログラムデータを制御装置間でコピーするよう構成する。

(もっと読む)

デマンドページング技法を適用したシステムでページ置換実行時間を短縮させる方法および装置

【課題】 フラッシュメモリのような不揮発性格納装置の特性を考慮して、ページング技法を提供する。

【解決手段】ページング技法を適用したシステムでページ置換実行時間を短縮させる方法は、(a)ページフォールトの発生を知らせる信号を受信するステップ、(b)前記ページフォールトが生じたページを不揮発性メモリから読み取るステップ、および(c)前記フォールトが生じたページを格納する空間をメモリから検索して確保するステップを含み、前記(c)ステップは予め計算された限界時間以内に行われ、前記システムのメモリにロードされるデータの一部は前記不揮発性メモリに格納されているページング技法を適用する。

(もっと読む)

有限トランザクションメモリシステム

有限トランザクションメモリシステムを提供する方法及び装置が記載される。一実施例では、ソフトウェアトランザクションメモリ(STM)アクセスに対応する処理は、先行するハードウェアトランザクションメモリ(HTM)アクセス処理が失敗する場合に実行される。  (もっと読む)

(もっと読む)

描画装置及びデータ転送方法

【課題】ハードウェアコストを削減出来る描画装置及びデータ転送方法を提供すること。

【解決手段】描画装置10は、メインメモリ13と、メインメモリ13との間で画像データの授受を行うキャッシュメモリ41と、メインメモリ13とキャッシュメモリ41との間のデータ転送を管理すると共に、キャッシュメモリ41の状態に関する情報を保持する転送制御装置45と、キャッシュメモリ41内の画像データを用いて画像処理プログラムを実行するプログラム実行部26とを具備し、キャッシュメモリ41は、各々が画像データを保持可能な複数のエントリを含み、転送制御装置45は、メインメモリ13からキャッシュメモリ41のエントリに転送される画像データの識別情報Tと、画像データがエントリに転送済みか否かを示す転送情報Rとをエントリ毎に保持する。

(もっと読む)

効率的かつ柔軟なメモリ・コピー動作

【課題】メモリ・コピー動作のあいだにプロセッサが後続の命令を実行し続けられるようなメモリ・コピー動作を提供し、不必要なプロセッサ・ダウンタイムを回避する。

【解決手段】半同期メモリ・コピー動作実行のためのメモリ・コピー命令を受信するステップを含む。半同期メモリ・コピー動作は、フラグ・ビットを設定することによりメモリ内のソース位置に対応する仮想ソース・アドレス及びメモリ内のターゲット位置に対応する仮想ターゲット・アドレスに関する妥当性の一時的な永続性を保つ。メモリ・コピー命令は、少なくとも仮想ソース・アドレス、仮想ターゲット・アドレス、及びコピーされるバイト数を識別する標識を含む。メモリ・コピー命令は、メモリ・コントローラによりメモリ・コピー動作を実行するために、メモリ・コントローラに結合されたキューに入れられる。後続の命令が命令パイプラインから利用可能になったときの実行が続行される。

(もっと読む)

プロセッサシステム

【課題】チップ内異種マルチプロセッサの使い勝手および性能を向上させることができるプロセッサシステムを提供する。

【解決手段】プロセッサとメモリとを有するプロセッサシステムであって、プロセッサ1は、プログラムを読み出す1つの制御ユニット10と、制御ユニットが読み出したプログラムのうちSIMD命令を送信する複数の演算ユニット20,30,40と、制御ユニットがメモリから読み出したプログラムを格納し、制御ユニットおよび複数の演算ユニットがデータの読出しおよび書込みを行うことができる共有キャッシュ50とから構成され、制御ユニットが複数の演算ユニットに対して送信する命令は、複数の演算ユニットが命令を実行する過程において、命令を実行している演算ユニットとは異なる演算ユニットからの外部信号受信まで該命令の実行を中断するか否かを指定する。

(もっと読む)

クリティカルセクションをトランザクション的に実行することによるロックの回避

クリティカルセクションをトランザクション的に実行することでロックを回避するシステムは、以下のようにプログラムを修正する。(1)クリティカルセクションのトランザクション的実行中に、プログラムはまずクリティカルセクションに関連するロックが別の処理によって保持されているか否かを決定し、保持されている場合にはトランザクション的実行を打ち切る。(2)トランザクション的実行が別の処理からの干渉的データアクセスに遭遇することなく完了する場合には、プログラムはトランザクション的実行中に作成された変更をコミットし、クリティカルセクションの後のプログラムの通常の非トランザクション的実行を任意で再開する。(3)トランザクション的実行中に別の処理からの干渉的データアクセスに遭遇する場合には、プログラムはトランザクション的実行中に作成された変更を破棄し、クリティカルセクションの再実行を試みる。  (もっと読む)

(もっと読む)

マイクロタイル方式がイネーブルされたメモリの自動検出

【課題】マイクロタイル方式がイネーブルされたメモリを自動的に検出する。

【解決手段】本発明の一実施形態において、一意的なビットパターンを持った書き込みキャッシュラインがメモリチャネルのメモリの開始アドレスに書き込まれる。メモリチャネルのメモリモジュールの各メモリ用集積回路に対してマイクロタイルメモリアクセスのイネーブルを試みる。メモリチャネルのメモリの開始アドレスから読み出しキャッシュラインを読み出す。読み出しキャッシュラインのビットパターンと、書き込みキャッシュラインのビットパターンを比較する。比較の結果、読み出しキャッシュラインのビットパターンが書き込みキャッシュラインのビットパターンとは異なることが分かった場合、メモリチャネルのメモリモジュールの各メモリ用集積回路に対してマイクロタイルメモリアクセスがイネーブルされている。比較の結果、読み出しキャッシュラインのビットパターンが書き込みキャッシュラインのビットパターンと同一であることが分かった場合、マイクロタイルメモリアクセスは、メモリチャネルのメモリモジュールの各メモリ用集積回路において、サポートされておらず、したがってイネーブルされ得ない。

(もっと読む)

1 - 20 / 25

[ Back to top ]