Fターム[5B005LL04]の内容

階層構造のメモリシステム (9,317) | データの種類 (402) | 命令 (106) | プログラムの種類 (46) | アプリケーションプログラム (24)

Fターム[5B005LL04]に分類される特許

1 - 20 / 24

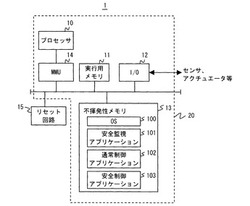

情報処理装置およびメモリ管理装置の動作確認方法

【課題】仮想アドレスを物理アドレスに変換するメモリ管理装置が正常に動作しているか否かを確認可能とする。

【解決手段】情報処理装置1は、メモリ11と、メモリ11の物理アドレス又はそれに対応する仮想アドレスを指定することで、メモリ11の物理アドレスに対してデータの読み出し又は書き込みを行うためのシステムプログラムと、システムプログラムを実行するプロセッサ10と、プロセッサ10からのメモリ11に対する仮想アドレスを指定した読み出し及び書き込みにおいて、仮想アドレスを物理アドレスに変換するメモリ管理装置14を備える。プロセッサ10は、システムプログラムによって、物理アドレスを指定してデータの書き込みを実施した後、その物理アドレスに対応する仮想アドレスを指定してデータの読み出しを実施して、書き込んだデータと、読み出したデータが一致するか否かを判定する。

(もっと読む)

メモリ管理方法、計算機及びメモリ管理プログラム

【課題】ソースプログラム又はオブジェクトコードの修正やコンパイル環境を必要とすることなく、システムの動作中に動的にメモリ上の命令の配置を最適化する。

【解決手段】プログラムを格納するメモリと、メモリに格納されたプログラムを実行するプロセッサと、メモリに格納されたプログラムを一時的に格納するキャッシュと、を備えた計算機におけるメモリ管理方法であって、プロセッサが、所定のタイミング毎にプログラムカウンタが示す値を取得する手順と、取得されたプログラムカウンタが示す値の履歴を、メモリ上のプログラムカウンタ履歴領域に記録する手順と、記録されたプログラムカウンタが示す値の履歴に基づいて、プログラムの実行状況に関する統計情報を生成する手順と、生成された統計情報に基づいて、メモリ上におけるプログラムの命令の配置を最適化する手順と、最適化に基づいて配置されたプログラムの命令をキャッシュに格納する手順とを含む。

(もっと読む)

限定された誤りによる遅延した更新によるソフトウェアキャッシュ処理

【課題】限定された誤りを可能にしながら、十分なデータコヒーレンシを維持するためのマルチコアシステム又はマイクロプロセッサにおけるソフトウェアキャッシュ方法を提供する。

【解決手段】キャッシュ値の遅延更新によって引き起こされるエラーに耐性のある最適化されたアプリケーション命令を実行する複数のプロセッサ要素を有するシステムと、メインメモリの一部を更新する最適化更新モジュールと、メインメモリの一部を抽出する最適化ロードモジュールとを有し、メインメモリの一部の変化を示す更新フラグは、メインメモリの一部の抽出前に閾値504に基づき定期的な間隔でチェックされ、変更を示し、閾値504に到達するまで、利用可能な場合はキャッシュメモリから抽出され、メインメモリの一部は、予め最適化されたアプリケーション命令のIPA(InterProcedual Analysis)の結果に基づき選択される。

(もっと読む)

翻訳ルックアサイドバッファと拡張ページングテーブルとの同期化

【課題】仮想マシンにおける効率的なアドレス変換が可能な手法を提供する。

【解決手段】プロセッサ318は、仮想化に基づくシステムのゲストの物理アドレス(ゲスト物理アドレス)から仮想化に基づくシステムのホストの物理アドレス(ホスト物理アドレス)までの翻訳ルックアサイドバッファ(TLB)323に格納されたマッピングを仮想化に基づくシステムの拡張ページングテーブル(EPT)328に格納された対応するマッピングを同期させる命令を実行するロジック322を含む。

(もっと読む)

移転元処理回路と移転先処理回路との間で作業負荷を移転するためのデータ処理装置および方法

移転刺激に応答して、移転に続いて移転元処理回路が電力節約状態に入れられる準備として、処理作業負荷の実施が移転元処理回路から移転先処理回路へ移転される。移転に続いて移転先処理回路によって必要となる、メモリ取得回数を削減するために、移転元処理回路のキャッシュは、スヌープ期間中、駆動状態に維持される。スヌープ期間中、キャッシュスヌープ回路は、移転元キャッシュのデータ値をスヌープし、移転先処理回路のためにスヌープデータ値を呼び出す。  (もっと読む)

(もっと読む)

メモリアクセス調査装置、メモリアクセス調査方法、及びプログラム

【課題】少ない負荷で、高速に、プログラムによるメモリへのアクセス状況を調査する。

【解決手段】仮想記憶方式に対応したオペレーティングシステムと、当該オペレーティングシステムにより所定のブロック単位で分割して管理されるメモリとを有するメモリアクセス調査装置において、実行される対象プログラムから前記メモリにアクセスがあったか否かを示すフラグ情報を、ブロック毎に保持するテーブル情報を格納するメモリ情報格納手段と、前記テーブル情報におけるフラグ情報を、所定のブロック毎に参照することにより、前記メモリへのアクセス状況を表す情報を取得し、当該情報を記憶手段に格納するメモリアクセス調査手段とを備える。

(もっと読む)

所与の範囲のページのキャッシュフラッシュおよび所与の範囲のエントリのTLB無効化を行なうシステム、方法、および装置

【解決手段】 複数のキャッシュラインのフラッシュ、および/または、複数のトランスレーション・ルックアサイド・バッファ(TLB)エントリの無効化を実行するシステム、方法および装置を記載する。このような方法の1つでは、プロセッサの複数のキャッシュラインをフラッシュするべく、プロセッサの複数のキャッシュラインをフラッシュする旨を示す第1のフィールドを含む単一の命令に応じて、プロセッサの複数のキャッシュラインをフラッシュする。 (もっと読む)

キャッシュメモリ結合性を伴うプロセッサコアの割当

複数のプロセッサコアとプロセッサコアの少なくともいくつかによって共有されるキャッシュメモリとを有するマルチコアプロセッサに関係する技法を全体的に説明する。マルチコアプロセッサを、キャッシュメモリ結合性のそれぞれのレベルを処理コアのそれぞれに別々に割り当てるように構成することができる。  (もっと読む)

(もっと読む)

プロセス状態検知プログラム、情報処理装置、プロセス状態検知方法

【課題】プログラムの生成、消滅の状態を判定することができるプログラム状態検知プログラムを提供する。

【解決手段】プログラムの切替えの際にオペレーティングシステムがトランスレーション・ルックアサイド・バッファの無効化を計測でき、無効化があると割り込みを発生させる機構を持つCPUを有するコンピュータに、プログラムの識別情報をオペレーティングシステムから取得してリストに記憶し、プログラムの切替えが生じた場合に発生する、CPUからの割り込みを検知した場合、オペレーティングシステムまたは機構から切替え先のプログラムの識別情報を取得し、リストと取得した識別情報を比較して、切替え先のプログラムが生成または消滅されるプログラムであるかを判定する処理を実行させるためのプログラム状態検知プログラムを提供する。

(もっと読む)

投機的バージョニング・キャッシュにおけるチェックポインティングのための方法、コンピュータ・プログラム、およびデータ処理システム(投機的バージョニング・キャッシュにおけるチェックポインティング)

【課題】 データ処理システム(100)の投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1030)を生成するための機構を提供する。

【解決手段】 機構は、データ処理システム(100)内でコードを実行し、コードは、投機的バージョニング・キャッシュ(310、1210)内のキャッシュ・ラインにアクセスする。さらに機構は、投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1030)を生成する必要性を示す第1の条件が発生するかどうかを決定する(1350)。チェックポイント(1310)は、投機的キャッシュ・ラインに対応するキャッシュ・ラインへの変更のロールバックを必要とする第2の条件の発生に応答して、非投機的となる、投機的キャッシュ・ラインである。機構は、第1の条件が発生した旨の決定に応答して、投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1310)も生成する。

(もっと読む)

I/Oのための多重レベルアドレストランスレーションを含むI/Oメモリ管理ユニット及び計算負荷軽減

【解決手段】

I/Oデバイスによるシステムメモリへの要求を制御するように構成される入力/出力メモリ管理ユニット(IOMMU)は、システムメモリ内に記憶されるトランスレーションデータを用いてI/Oデバイス生成の要求に関連するアドレスをトランスレートするために2レベルのゲストトランスレーションを行い得る制御論理を含む。トランスレーションデータは、幾つかのエントリを有するデバイステーブルを含む。制御論理は、所与の要求を生成するI/Oデバイスに対応するデバイス識別子を用いることによって、その要求に対するデバイステーブルエントリを選択してよい。トランスレーションデータはまた、ゲストページテーブルのセットと、入れ子にされたページテーブルのセットとを含むI/Oページテーブルの第1のセットを含んでいてよい。所与の要求に対して選択されたデバイステーブルエントリは、ゲストトランスレーションテーブルのセットへのポインタを含んでいてよく、そして最後のゲストトランスレーションテーブルは、入れ子にされたページテーブルのセットへのポインタを含む。

(もっと読む)

周辺相互接続におけるI/O及び計算負荷軽減デバイスのための2レベルのアドレストランスレーションを用いるIOMMU

【解決手段】

コンピュータシステムのシステムメモリへのI/Oデバイスによる要求を制御するためのIOMMUは、制御論理及びキャッシュメモリを含む。制御論理は、I/Oデバイスからの要求において受信されるアドレスをトランスレートしてよい。要求が処理アドレス空間識別子(PASID)プレフィックスを伴うトランザクション層プロトコル(TLP)パケットを含む場合には、制御論理は2レベルのゲストトランスレーションを実行してよい。従って、制御論理は、ゲストページテーブルのセットにアクセスして、要求において受信されるアドレスをトランスレートしてよい。最後のゲストページテーブル内のポインタは、入れ子にされたページテーブルのセット内の第1のテーブルを指し示す。制御論理は、入れ子にされたページテーブルのセットにアクセスしてシステムメモリ内の物理ページに対応するシステム物理アドレス(SPA)を得るために、最後のゲストページテーブル内のポインタを用いてよい。キャッシュメモリは完了したトランスレーションを記憶する。

(もっと読む)

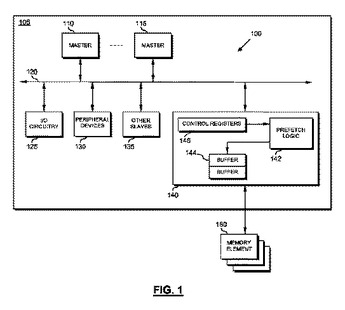

プリフェッチ・モジュールを備える信号処理システムおよび集積回路、並びにそのための方法

信号処理システム(100)は、少なくとも1つのマスタ・デバイス(110、115)と、少なくとも1つのメモリ素子(160)とを備え、さらに、少なくとも1つのマスタ・デバイス(110、115)から少なくとも1つのメモリ素子(160)へのメモリアクセス要求に応じて、少なくとも1つのメモリ素子(160)からのプリフェッチを実行するように構成されたプリフェッチ・モジュール(142)を備える。プリフェッチ・モジュール(142)は、少なくとも1つのマスタ・デバイス(110、115)からメモリアクセス要求を受信すると、メモリアクセス要求が関連するアドレスに少なくとも部分的に基づいて、そのメモリアクセス要求に関連する命令情報およびデータ情報の少なくとも一方のプリフェッチの許可を設定するように構成されている。  (もっと読む)

(もっと読む)

データマップ読み取り装置、データマップ読み取り方法

【課題】高速メモリを用いたMAP引きによる演算を高速に実行するデータマップ読み取り装置及びデータマップ読み取り方法を提供すること

【解決手段】検索用データ24を記憶する第1の記憶手段15と、第1の記憶手段15のアドレスに従い、検索用データ24を一様方向に読み出す読み出し手段23と、読み出し手段が読み出した、検索用データ24の複製を記憶する第2の記憶手段13と、第2の記憶手段13に複製された検索用データ24を被検索値xinに基づき検索する検索手段25が、検索用データを24インクリメントサーチするかデクリメントサーチするかによって、検索用データ24の複製を読み出す方向を、第1の記憶手段15のアドレスの降順方向又は昇順方向のいずれかに切り替える切り替え手段21と、を有することを特徴とするデータマップ読み取り装置100を提供する。

(もっと読む)

プリフェッチ生成プログラムおよびコンパイラ装置

【課題】キャッシュメモリ上の必要なデータの上書きを防ぎ、キャッシュの利用効率を向上することを課題とする。

【解決手段】コンパイラ装置10は、ソースプログラムを解析し、アクセスするメモリ領域を所定のブロックに分割するループブロッキングのパターンにソースプログラムが該当するか判定する。そして、コンパイラ装置10は、ループブロッキングのパターンに該当すると判定された場合には、次に処理するブロックに対してプリフェッチ命令を生成する。

(もっと読む)

プログラムのメモリ空間への配置方法、装置、およびプログラム

【課題】命令キャッシュ競合の回数を効果的に削減する。

【解決手段】関数を単位で構成されるプログラムに対し、ターゲットプロセッサの命令キャッシュラインサイズをCSとすると、各関数をサイズがCSの命令コードブロック(=ICB)に分割し、各関数Fの先頭から数えてX番目のICBを(F,X)とした場合に、関数プログラムの実行プロファイルより(F,X)を識別名とするノードのフロー情報を抽出する。識別名毎にフロー情報におけるその出現ノード毎の近傍内に、自分と異なる関数に属する各識別名の出現頻度を考慮した情報を、自分からみた他の各識別名の近傍重みとして求める。近傍重み情報に基づいて、命令キャッシュ競合回数が少なくなるように、複数の関数をメモリ空間に配置する。

(もっと読む)

プログラム、コンピュータ及び制御方法

【課題】中断後に再度起動する場合に迅速に希望するアプリケーションを使用することが可能なプログラム、コンピュータ及び制御方法を提供する。

【解決手段】VM2上で動作する複数のアプリケーション212が使用するRAM12の各使用領域を領域ファイル151に記憶する。運転中のVM2に対する中断命令を受け付けた場合、複数のアプリケーション212が使用するRAM12上の情報をHD15へ保存する。そして、中断中のVM2に対する起動命令を受け付けた場合、複数のアプリケーション212の内、HD15からRAM12の使用領域へ優先的に復元するアプリケーション212を選択する。

(もっと読む)

メモリスワップ管理方法、装置およびプログラム

【課題】次のプロセス実行開始までの時間を短縮する。

【解決手段】実行待ちのジョブキューがある場合は、ジョブキュー500からジョブキューチェックテーブル1200を作成し、これと、DRAM38の実メモリに記憶されているプロセスの種類とに基づいてスワップアウト/イン候補のプロセスを決定する。実行待ちのジョブキューがない場合は、プロセス実行履歴テーブル600と、直前に実行されたプロセスの種類とに基づいてプロセス実行頻度テーブル1300を作成し、次に実行されるプロセスを予測すると共に、該予測に基づいてスワップアウト/イン候補のプロセスを決定する。上記決定に従って、スワップアウト候補を実メモリからスワップアウトし、それによって空いた実メモリの領域に、スワップイン候補をスワップインする。

(もっと読む)

ソフトウェア実行システムおよびソフトウェアの実行方法

【課題】新しいソフトウェア実行方法とソフトウェア実行システムを提供する。

【解決手段】当該ソフトウェア実行システムは、クライアント側(C側)の実行モジュールと、サーバ側(S側)の制御・データ分配モジュールとを含む。前者は、ソフトウェアパッケージの定義ファイルを取得、ロードすると共に、C側でアプリケーションの実行に必要な環境を構築し、実行したいアプリケーションに対応するプロセスを生成するようにOSを制御するプロセスロードサブモジュールと、アプリケーションからのI/Oリクエストを監視、捕捉するI/O監視・処理サブモジュールと、S側とネットワーク通信を行うネットワーク通信サブモジュールとを含む。後者は、S側の他のサブモジュールとC側の間の動作を調整する制御サブモジュールと、C側にソフトウェアパッケージ内の具体的なデータを提供するデータ分配サブモジュールを含む。

(もっと読む)

アドレス変換装置

【課題】 ページ・フォールトの発生を抑制し、パフォーマンスを改善したアドレス変換装置を実現する。

【解決手段】 CPUから提供される論理アドレスを、変換テーブルにより前記CPUの主メモリの物理アドレスに変換するアドレス変換装置において、

前記主メモリのデータ領域内の特定領域に専用にアクセスするための専用エントリーを前記変換テーブルに固定配置する。

(もっと読む)

1 - 20 / 24

[ Back to top ]