Fターム[5B005NN12]の内容

階層構造のメモリシステム (9,317) | W/R制御 (1,413) | 転送制御 (519) | 階層メモリ間の転送 (205)

Fターム[5B005NN12]の下位に属するFターム

Fターム[5B005NN12]に分類される特許

1 - 20 / 170

半導体記憶装置

複数の状態のプロセッサのための命令のキャッシング

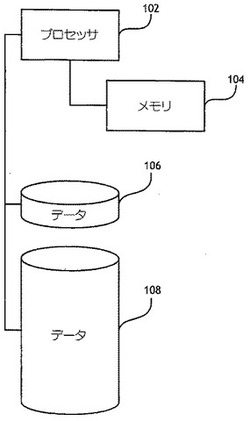

階層間の効率的なデータ移行を管理する装置

【課題】低速階層及び高速階層を有するデータストレージシステムにおいて、階層間でデータを効率的に移行させる。

【解決手段】高速データストレージデバイス106のリザーブスペースを備えている。プロセッサ102は、メモリ104に記憶されたリザーブスペーステーブルを参照して、低速データストレージデバイス108に記憶されたデータへのアクセスが高頻度となることによりホットデータとなると、該データを高速データストレージデバイス106のリザーブスペースに移し、該ホットデータを高速データストレージデバイス106上に保持する。データ移行は、一方向性であることが多く、データは低速階層から高速階層へ移行し、通常動作中のオーバーヘッドを低減することができる。

(もっと読む)

キャッシュ装置、メモリシステム及びデータ転送方法

【課題】キャッシュデータを効率的にメインメモリへライトバックすることができるキャッシュ装置、メモリシステム及びデータ転送方法を提供すること

【解決手段】本発明にかかるキャッシュ装置は、複数のキャッシュデータが、メインメモリ80に格納されている複数のデータと一致しているか否かを判定するライトバック制御部60と、複数のキャッシュデータのうち、不一致と判定されたキャッシュデータであって、メインメモリ80において連続するアドレスへ書き込まれる複数のキャッシュデータを格納するデータバッファ部13と、データバッファ部13へ格納されたキャッシュデータを一括してメインメモリ80へ書き込むメモリライト部14と、を備えるものである。

(もっと読む)

キャッシュメモリ装置、プロセッサ、および情報処理装置

【課題】十分な消費電力の削減が図ることができるキャッシュメモリ装置を提供する。

【解決手段】キャッシュメモリ装置100aは、記憶装置のデータをキャッシュする。キャッシュメモリ装置100aは、記憶部110aと、制御部120aと、を備える。記憶部110aは、複数のキャッシュラインを有する。制御部120aは、前記複数のキャッシュラインのうち、前記記憶装置に書き込まれていないデータを含むダーティラインの数が予め定めた所定数を超える場合に、前記ダーティラインのデータを前記記憶装置に書き込む。

(もっと読む)

情報処理装置およびキャッシュ方法

【課題】コントローラに接続された第1の記憶装置をコントローラに接続された第2の記憶装置のリードキャッシュとして用いた場合に性能の低下を抑制すること。

【解決手段】実施形態によれば、情報処理装置は、コントローラと、キャッシュ手段とを具備する。コントローラは、第1の記憶装置および第2の記憶装置にコマンドを発行することによってデータの転送を行う。キャッシュ手段は、前記第1の記憶装置を前記第2の記憶装置のリードキャッシュとして用いる。キャッシュ手段は、前記コントローラが前記第1の記憶装置に対して設定数より大きい数のコマンドを発行している場合、キャッシュデータを前記第1の記憶装置に書き込むためのライトコマンドを、発行しているコマンド数が前記設定数以下になるまで前記コントローラへの発行を保留する。

(もっと読む)

処理パイプラインの制御

【課題】処理パイプライン内の処理バブルの低減が可能なデータ処理装置を提供する。

【解決手段】グラフィクス処理ユニットは、第1パイプライン部分18と第2パイプライン部分20とを有するテクスチャパイプライン6を含む。第1パイプライン部分18内の主題命令は、その主題命令によりメモリからロードされる記述子データが、共有記述子キャッシュ内に貯えられるまで、第1パイプライン部分18内で再循環される。記述子が、共有キャッシュ内に保存されている場合、主題命令は、追加の処理操作が実行される第2パイプライン部分20に渡され、それらの追加の処理操作が完了するまで再循環される。記述子データは、その記述子データを利用するのに必要とされるテクスチャパイプライン6内の係属中の主題命令がなくなるまで、共有記述キャッシュ内に固定される。

(もっと読む)

メモリ制御装置及びメモリ制御方法

【課題】メモリアクセスにおいてECCの方式変更を自動的に行う技術を提供する。

【解決手段】バッファメモリと、このバッファメモリを単位データ毎にキャッシュするキャッシュメモリと、この単位データにバイトECCを付加する付加手段とを備えたメモリ制御装置。また、バッファメモリを備えたメモリ制御装置におけるメモリ制御方法であって、このバッファメモリを単位データ毎にキャッシュし、この単位データにバイトECCを付加するメモリ制御方法。

(もっと読む)

通信装置、通信方法、およびプログラム

【課題】ディスク記憶媒体のデータを、複数のサーバにインストールさせる作業に、長い時間を要しない通信装置を提供する。

【解決手段】通信装置5は、プロトコルシリアライザ10と、キャッシュコントローラ11とを備える。プロトコルシリアライザ10は、ディスク記憶媒体Kに記憶されたデータの読取要求を、サーバA1〜A3から受信するとともに、該受信した読取要求を、ディスク記憶媒体Kへの一つのアクセス権に係る命令にシリアライズする。キャッシュコントローラ11は、シリアライズされた読取要求の順序に従って、読取要求に係る要求データを、ディスク記憶媒体Kに記憶されたデータの中から取得する。また、プロトコルシリアライザ10は、キャッシュコントローラ11が取得した要求データを、該要求データに対応する読取要求の送信元サーバAに送信する。

(もっと読む)

システムパフォーマンスを改善するための外部メモリデバイスの使用

【課題】回転式ストレージデバイス(例えば、ハードドライブ)のセクタをキャッシュするために外部メモリデバイスを利用して、システムパフォーマンスを改善するためのシステムおよび方法を提供すること。

【解決手段】外部メモリデバイス(EMD)が、コンピューティングデバイス、またはコンピューティングデバイスが接続されたネットワークに接続されたとき、システムは、EMDを認識し、ディスクセクタによってEMDをポピュレートする。システムは、ディスクセクタに対するI/O読取り要求を、実際のディスクセクタの代わりにEMDキャシュに向けて送る。EMDの使用は、コンピューティングデバイスにメモリを追加するコストに対してわずかのコストで、コンピューティングデバイスシステムにおけるパフォーマンスおよび生産性を向上させる。

(もっと読む)

メモリシステムおよびその動作方法

【課題】動作速度を低下させることなくシステムの信頼性を向上させることが可能なメモリシステムおよびその動作方法を提供する。

【解決手段】不揮発性メモリシステム2は、ブロック(ページ)単位でデータのアクセスが行われるNAND型フラッシュメモリ21(第1の不揮発性メモリ)と、ワード単位でデータのランダムアクセスが行われるNVRAM22(第2の不揮発性メモリ)と、NAND型フラッシュメモリ21およびNVRAM22の動作の制御を行うNVMコントローラ23(制御部)とを備えている。NVRAM22のデータに適用されるエラー訂正コードECC2が、NAND型フラッシュメモリ21内に保持されている。NVRAM22に対するアクセス速度の低下が回避されつつ、このNVRAM22におけるデータ保持特性が改善される。

(もっと読む)

プロセッサシステム

【課題】メインメモリから同じデータを2度読み出さない形で画像処理を実行可能な、大容量のキャッシュメモリを内蔵させることなく低消費電力で実現できるプロセッサシステムを、提供する。

【解決手段】プロセッサシステム10は、或るブロックのデータの掃き出し時にそのデータの書戻要求を発行するキャッシュメモリ12と、キャッシュメモリ12からの書戻要求に基づき、再度キャッシュメモリ12内に読み込ませることが必要なデータをローカルメモリ14上に用意し、キャッシュメモリ12からのリード要求にローカルメモリ14上のデータを利用して応答するインターコネクト13とを備える。

(もっと読む)

メモリシステム

【課題】

実施形態は、複数のバッファ部それぞれに保持されたデータを交換可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、データを保持可能なページバッファを含むNAND型フラッシュメモリと、前記NAND型フラッシュメモリとデータバスを介して電気的に接続された複数の記憶部と、前記NAND型フラッシュメモリ、前記複数の記憶部を制御する制御部とを備え、前記データバスの幅は、前記データの容量よりも小さく、前記制御部は、前記NAND型フラッシュメモリに書き込み又は読み出しを行うとき、前記ページバッファに保持するデータと前記複数の記憶部のうち1の記憶部に保持するータとを交換することを特徴とする。

(もっと読む)

キャッシュ装置、及び情報処理装置

【課題】簡単な構成で各プロセッサが特定のデータを排他的に処理できるキャッシュ装置、及び情報処理装置を提供することを課題とする。

【解決手段】プロセッサP1,P2に個別に対応する複数のキャッシュメモリC1,C2と、各キャッシュメモリC1,C2間でデータを転送するデータ転送部Tと、を備え、データ転送部Tは、第1のプロセッサP1が処理し更に第2のプロセッサP2が処理を加えるデータであって下位の記憶階層4の特定アドレスにある特定データを第1のプロセッサP1が処理した後、処理された特定データを第2のプロセッサP2に対応するキャッシュメモリC2へ転送し、第2のプロセッサP2に対応するキャッシュメモリC2は、データ転送部Tから特定データが転送されるまでは第2のプロセッサP2による特定アドレスのデータへのアクセスを保留し、データ転送部Tから特定データが転送された後アクセスを再開する。

(もっと読む)

記憶効率の高いセクタ化されたキャッシュ

電源回復後のリロード機能付きキャッシュ

キャッシュを再配置する方法および機器が開示される。キャッシュの内容の少なくとも部分が、キャッシュから分離した場所に格納される。電源がキャッシュから切られ、いくぶんかの時間の後に回復される。電源がキャッシュに回復された後、それは、キャッシュから分離して格納されたキャッシュの内容の部分で再配置される。 (もっと読む)

移転元処理回路と移転先処理回路との間で作業負荷を移転するためのデータ処理装置および方法

移転刺激に応答して、移転に続いて移転元処理回路が電力節約状態に入れられる準備として、処理作業負荷の実施が移転元処理回路から移転先処理回路へ移転される。移転に続いて移転先処理回路によって必要となる、メモリ取得回数を削減するために、移転元処理回路のキャッシュは、スヌープ期間中、駆動状態に維持される。スヌープ期間中、キャッシュスヌープ回路は、移転元キャッシュのデータ値をスヌープし、移転先処理回路のためにスヌープデータ値を呼び出す。  (もっと読む)

(もっと読む)

アドレススヌープ方法及びマルチプロセッサシステム

【課題】本発明は、アドレススヌープ方法及びマルチプロセッサシステムに関し、多数のI/Oブロックをプロセッサブロックから独立させてマルチプロセッサシステムに容易に実装可能とすると共に、マルチプロセッサシステムの性能の上限の低下(レイテンシの増加)を防止可能とすることを目的とする。

【解決手段】複数のプロセッサと複数のメモリからなるプロセッサブロックが複数個アドレス結合装置を介して複数のI/Oブロックと接続された構成のマルチプロセッサシステムにおけるアドレススヌープ方法において、任意の1つのプロセッサブロックからアクセスリクエストが発生したときに、前記アクセスリクエストに対して応答するか否かを判断するアドレススヌープ処理を、各I/Oブロックに代わって前記アドレス結合装置において行うように構成する。

(もっと読む)

情報処理装置

【課題】キャッシュメモリからメインメモリへのデータの書き戻し時間を短縮することができる情報処理装置を提供する。

【解決手段】 情報処理装置1は、キャッシュメモリ7,8を有するコア2,3が内蔵されたマルチコアCPU4と、マルチコアCPU4と接続されたDRAM6とを備えている。キャッシュメモリ7,8には、キャッシュデータを含む情報と当該情報をコア2,3の何れに移動させるかを示すバランス情報とがキャッシュライン毎に記憶されている。マルチコアCPU4は、バランス情報を参照してキャッシュメモリ7,8のキャッシュ使用量を平均化するようにキャッシュメモリ7,8間で情報を移動させるキャッシュバランス制御部13と、その情報の移動が行われた後に、キャッシュメモリ7,8に記憶されたキャッシュデータをDRAM6に書き戻すキャッシュ書き戻し制御部14とを有している。

(もっと読む)

動的なシステムの再構成

【解決手段】 一部の実施形態によると、複数のプロセッサコアを含むシステムの動的ハードウェア再構成を実行するために用いられるシステム再構成用のコードおよびデータをキャッシュして、動的ハードウェア再構成の間、直接メモリアクセスまたは間接メモリアクセスを禁止する。複数のプロセッサコアのうち一のプロセッサコアが、キャッシュされたシステム再構成用のコードおよびデータを実行して、ハードウェアを動的に再構成する。他の実施形態も説明および請求している。 (もっと読む)

1 - 20 / 170

[ Back to top ]