Fターム[5B011LL01]の内容

電源 (19,167) | 節電(オートパワーオフを除く) (3,178) | 漏れ電流の防止 (57)

Fターム[5B011LL01]に分類される特許

41 - 57 / 57

半導体集積回路装置

【課題】本発明は、IPの電源を動的または静的に遮断し、リーク電流を削減する半導体集積回路の提供を課題とする。

【解決手段】本発明は、複数のIPを含む半導体集積回路において、IPの処理終了を示す割込み信号を用いて、電源供給と遮断の制御を行う。電源制御レジスタ5はIP単位で電源供給と遮断を制御するビットを持ち、割り込み信号による動的あるいは、ソフトウェアによる静的な電源制御を行うことができる。既存の割込みコントローラ3を利用するため、小さいハードウェア規模で電源遮断制御が実現可能である。

(もっと読む)

半導体集積回路装置および信号処理システム

【課題】リーク電流を抑制する方法の一つとしてソース線にバイアス電圧を印加する手法があるが、待機モードから通常モードに遷移する際に放電時間を確保する必要がありシステムの応答速度に問題がある。

【解決手段】バイアス電圧制御回路103はタイミング設定情報104とカウンタ回路105を使って、バイアス電圧出力回路102が出力するバイアス電圧の放電動作を回路動作が行われる前に実施することで放電時間の隠蔽を行いシステムの応答速度の影響をなくし、低消費電力の半導体集積回路装置を実現する。

(もっと読む)

集積回路およびそれを搭載した電子機器

【課題】 回路の信頼性を保ちながら、消費電力を抑制する。

【解決手段】 コア部20は、所定の機能を実現する。I/O部10は、外部との入出力制御を行う。それぞれ独立に電源制御され、コア部20の電源を落とした際、I/O部10の電源を保ちながら、I/O部10からコア部20に出力される信号をローレベルに固定する。第1レベルシフタ14および第2レベルシフタ16は、コア部20とI/O部10コア部との間に設けられ、それらの電源電圧レベルの差異を吸収する。コア部20の電源を落とした際、第1レベルシフタ14および第2レベルシフタ16の電源を落とす。

(もっと読む)

選択的なパワー・ゲーティングを用いて電力消費を低減する装置及び方法

トランジスタ・ベースの回路の電力消費を低減する方法(200)であって、低電力モード指示を受け取るステップ(230)と、トランジスタ・ベースの回路のリセット値と、低電力モード指示を受け取る前のトランジスタ・ベースの回路の状態とに応答して、電力をトランジスタ・ベースの回路の少なくとも一部分に供給すべきかどうか決定するステップ(240)と、電力をトランジスタ・ベースの回路の少なくとも一部分に選択的に与えるステップ(250)とを含む。トランジスタ・ベースの回路(100)の電力消費を低減する装置(200)であり、当該装置は、トランジスタ・ベースの回路に結合され、低電力モード指示を受け取るよう適合されている。当該装置は、低電力モード指示を受け取る前の前記トランジスタ・ベースの回路の状態に応答して、電力を前記トランジスタ・ベースの回路の少なくとも一部分に供給すべきかどうか決定する手段(38)と、上記の決定に応答して、電力をトランジスタ・ベースの回路の少なくとも一部分に選択的に与えるよう適合されているパワー・ゲーティングするための手段(40,42)とを含む。  (もっと読む)

(もっと読む)

情報処理装置

【課題】 割り込み資源の有効活用と省電力化。

【解決手段】 キーとACアダプタの割り込み資源を共有する。キー状態を検出するポートを別に用意する。

AC駆動ではキーの割り込みが取れとれなくとも、キー状態のポーリングを行うことによりキーの取り込みができるのでACアダプタ検出の割り込みポートをキー検出と共用させることで割り込みポートを節約できる。電池駆動の場合はキーの取得を割り込み処理で行うことにより、プロセッサの動作時間を節約し、省電力が可能となる。

(もっと読む)

電子機器、省電力モード制御方法およびプログラム

【課題】プログラム作成工数を削減することができると共に、省電力モード用データテーブル作成時の人為的なミスを防ぐことができる電子機器、省電力モード制御方法およびプログラムを提供する。

【解決手段】 電子機器100は、省電力モードを有するICの各入出力ポートを入力モードにするモード切り換え手段と、モード切り換え手段により入力モードにされた各入出力ポートのレベルを判別する判別手段と、判別手段の判別結果に基づいて、入出力ポートをハイレベル出力またはローレベル出力にするように制御する制御手段とを備え、一定時間、継続してキー入力操作がなかったとき、入出力ポートを入力モードにし、入力モードにされた各入出力ポートのレベルを判別し、その判別結果に基づいて、ハイレベルであると判別された入出力ポートをハイレベル出力にし、ローレベルであると判別された入出力ポートをローレベル出力にするように制御する。

(もっと読む)

半導体集積回路装置

【課題】

CPUに対する複雑な電源供給シーケンスに対応でき、かつ消費電力の削減効果が高い半導体集積回路装置を提供すること。

【解決手段】

本発明にかかる半導体集積回路装置は、演算回路を備えたCPU10と、CPU10の電源制御を電源IC200を介して実行するPMU1とを備えている。このPMU1は、演算回路を有しない。また、PMU1は、複数のコマンドを格納するRAM1bと、RAM1bに格納されたコマンドに基づいてCPU10の電源制御を実行する制御部1aとを備えている。

(もっと読む)

マイクロコントローラ

【課題】 マイクロコントローラの待機時のオフリーク電流削減のために電源遮断を行うと重要レジスタのデータが失われ、待機時からの復帰はコールドスタートのみになるが、重要レジスタのデータを保持することで、ホットスタートを可能にする構成を提供する。

【解決手段】 マイクロコントローラ100の電源系を電圧VDD1、VDD2の2系統に分け、内部状態を保持しておきたい最低限のブロックにのみ常に電圧VDD2の系統から常時電源を供給し、それ以外のブロックは、電圧VDD1の系統から電源を供給することで待機時に電源を遮断する。これによって、内部状態を失うことなく待機時のリーク電流をほぼゼロにでき、ストップレギュレータ230の自己消費電流分と合わせても待機時電流の削減が可能である。

(もっと読む)

供給電圧及びボディバイアスのダイナミック制御を通して電力消費を削減するための一つの方法及び装置

【解決手段】 一つの集積回路デバイスの電力削減についての一つの取組み法。一つの集積回路デバイスに結び付く一つの動作強度が、一つの第一動作強度から一つの第二動作強度へ一つの変化をするのが検知されるのに応答して、前記第二動作強度に基づき前記集積回路デバイスに結び付く一つの供給電圧及び一つのボディバイアスを調整して、電力消費を削減する。一つの様態において、前記供給電圧及びボディバイアスは、前記集積回路デバイスに対し一つの実質的に定常な動作周波数を維持するように調整される。  (もっと読む)

(もっと読む)

半導体回路

【課題】 LSIのパワーオルエリアの電源投入・遮断時に貫通電流や誤動作を発生させることなく、確実に電源遮断状態に移行させる。

【解決手段】 パワーオフエリアにマスクレジスタ19を設け、電源遮断の前にこのマスクレジスタ19に“L”のマスク信号をセットする。バックアップエリア側では、パワーオフエリアから与えられるマスク信号を保持すると共に、このマスク信号が無電圧状態となったときには“L”を保持するラッチ回路33Aを設け、このラッチ回路33Aで保持したマスク信号を用いて、パワーオフエリア側との間の入出力信号をマスクする。

(もっと読む)

情報処理装置および電力制御方法

【課題】 情報処理装置における電力制御をより適切に行うこと。

【解決手段】 情報処理装置1は、各機能部に電力を供給しない状態を基本とし、動作が必要な場合にのみ電力を供給して処理を行わせ、処理の終了後には、再び電力の供給を停止するように電力制御を行うことが可能である。したがって、特に、リーク電流が問題となるCPU20についても、電力を供給しない状態を基本とすることができる。また、各機能部それぞれを対象として電力制御を行うより、回路規模および制御の容易性の面で有利なものとなる。さらに、各機能部に電力を供給しない状態を基本としているため、状態の遷移に関する処理が軽減され、サスペンドモード等を用いる場合に比べて操作を行った場合の応答を速くすることができる。即ち、情報処理装置1における電力制御をより適切に行うことが可能となる。

(もっと読む)

マイクロコントローラ、およびマイクロコントローラの電源供給方法

【課題】 複数の回路ブロックの動作状態に応じて個別に電源電圧を可変して供給することが可能なマイクロコントローラ、及びその電源供給方法を提供すること。

【解決手段】 回路ブロック51乃至54にはレギュレータ部(1)11乃至(4)14から内部電源電圧VR1乃至VR4が給電される。内部電源電圧VR1乃至VR4は電圧設定レジスタ部2において設定される設定信号SVR(1)乃至SVR(4)に応じて設定される。各回路ブロック51乃至54および電圧設定レジスタ部2とバス線56との間には、レベルコンバータ(0)30乃至(4)34が配置され、両者間の信号振幅レベルが異なる場合、電圧値がレベルシフトされてインターフェースされ、両者間が同電位である場合、レベルシフト機能をバイパスする機能を有している。動作状態に応じて内部電源電圧を可変として高速・高機能動作と低消費電流動作とを両立することができる。

(もっと読む)

情報処理システム及び画像形成装置

【課題】待機電力の低減を図り、内部の回路デバイス相互間の電源の回り込みを防止して使用デバイスの長寿命化を図り、待機状態から高速に起動、復帰させるようにする。

【解決手段】 画像情報の処理を行うシステムコントローラASIC A1と、CPU A2と、ROM/RAM A3と、RESET IC A5と、プルアップ抵抗A6とにより構成される画像処理部、プリンタ、スキャナ等の制御を行うエンジンコントローラASIC B2と、CPUB1と、ROM/RAM B3とにより構成される画像形成部により構成され、各部位に対して電源供給ユニットC0からの電源の供給を制御するレギュレータC1〜C5が備えられている。ASIC A1は、レギュレータC1、C2、C4、C5を制御し、起動、待機、復帰の制御を行うと共に、接続されている入出力装置の入出力インタフェースの出力部に対するハイインピーダンス制御を行い、入出力インタフェースの入力を含む部分における貫通電流防止制御を行う。

(もっと読む)

低電力デバイスの待機電力制御

電力管理を行うシステム及び方法は、電圧調整器からの電圧を計算システムの構成要素に印加すること、及び構成要素に専用の省電力パラメータに基づいてその電圧を低下させることを提供する。この低電圧化は、構成要素が待機状態又はオフ状態などの低電力状態に入ることに連動され、省電力パラメータはその構成要素の、それぞれ、最小動作電圧又は最小持続可能電圧などの電圧を定めるものとされる。一実施形態においては、この構成要素は中央演算処理ユニットである。

(もっと読む)

(もっと読む)

半導体集積回路

【課題】本発明は、プロセッサの動作電圧を動的に変動させる場合にプロセッサがハングアップ等の異常動作をすることがないように、チップ毎の動作特性及び現在の動作条件での動作特性に応じた最適な電圧設定が可能な半導体集積回路を提供することを目的とする。

【解決手段】半導体集積回路は、クロック信号に基づいて動作して命令を実行するコア回路と、コア回路に供給される電源電圧を変更する電圧制御部と、クロック信号をコア回路に供給するクロック生成部と、クロック信号及び電源電圧で動作してコア回路の動作を模擬することによりコア回路が電源電圧で正常に動作するか否かをテストするテスト回路を含み、電圧制御部が電源電圧を変更している間においてクロック生成部はクロック信号の代わりに別の信号をコア回路に供給する。

(もっと読む)

集積回路を備えるモバイル装置およびそのような回路をパワーダウンする方法

本発明は、所定の機能を動作させるための集積回路を備えるモバイル装置に関し、前記集積回路は、当該回路が所定の遅延時間内に動作を再開できる待機動作モードに設定可能である。回路は、当該回路が待機モードに入り前に記憶される必要がある所定の状態を有するコンフィギュレーション順序論理を備えている。モバイル装置は、待機モード中にコンフィギュレーション順序論理の状態を漏れの低い記憶領域に記憶して待機電流をかなり減少させるパワーダウンユニットを更に備えている。  (もっと読む)

(もっと読む)

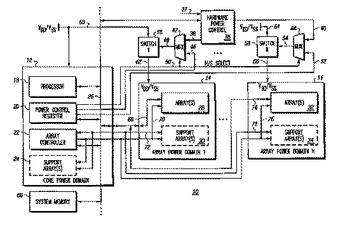

回路アレイの漏れ電流を低減するための集積回路電力管理及びそのための方法

漏れ電流は、メモリ・アレイ(28)とインターフェースするプロセッサ(18)を有する処理システム(12)の低電力モードの間に当該メモリ・アレイの中で排除される。2つの電力プレーンが生成されるので、プロセッサ(18)は、アレイがパワーダウンされるときメモリ・アレイ(28)をバイパスしながら、システム・メモリ(80)を用いて命令を実行し続け得る。スイッチ(56)が、命令の実行から、又はプロセッサ以外のどこかのシステムで発生するソースから結果として生じるプロセッサにより開始された制御に応答して電圧供給端子に対する電気接続を選択的に取り去る。メモリ(28)への電力が回復すると直ぐに、データは、メモリ・アレイに対する2つの電力プレーン・サポート・アレイのうちのどちらが配置されるかに依存して使用不能として印をされることが必要であっても、又はなくてもよい。所定の判定基準を用いて、電力の回復のタイミングを制御し得る。多重アレイが、漏れ電流を独立に低減するため実行され得る。  (もっと読む)

(もっと読む)

41 - 57 / 57

[ Back to top ]