Fターム[5B013DD00]の内容

先行制御 (1,991) | 並列処理 (600)

Fターム[5B013DD00]の下位に属するFターム

Fターム[5B013DD00]に分類される特許

1 - 11 / 11

VLIWプロセッサと命令構造と命令実行方法

【課題】VLIWプロセッサにおいて、小さな回路規模で複雑な条件判定処理を効率良く実行する。

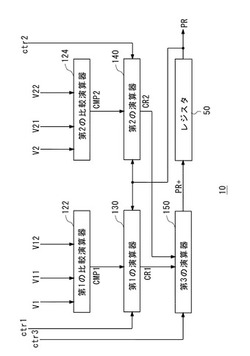

【解決手段】第1の演算器130は、第1の制御信号ctr1に応じて、第1の比較演算器122の出力、該出力とレジスタ50が既に保持している値の論理積、論理和のうちの1つを第1の演算結果CR1として出力する。第2の演算器140は、第2の制御信号ctr2に応じて、第2の比較演算器124の出力と、該出力とレジスタ50が既に保持している値の論理積、論理和の3つのうちの1つを第2の演算結果CR2として出力する。第3の演算器150は、第3の制御信号ctr3に応じて、第1の演算結果CR1、第1の演算結果CR1と第2の演算結果CR2の論理積、論理和のうちの1つを実行結果としてレジスタ50に出力する。レジスタ50は、第3の演算器150からの実行結果を新たに保持し、出力する。

(もっと読む)

マルチステージデータ処理パイプラインにおける命令実行システム及び方法

命令を実行するための複数のステージをもつ命令実行パイプラインを含む装置が開示される。該装置は、また、該命令実行パイプラインに連結された制御ロジック回路を含む。該制御ロジック回路は、該命令の実行の間に該命令実行パイプラインの少なくとも1つのステージをスキップする。該制御ロジック回路は、また、該デコードされた命令の実行の間に少なくとも1つのスキップされないステージを実行する。 (もっと読む)

マイクロプロセッサ

【課題】 プロセッサモジュールの挙動をトレース可能であり、且つアプリケーション処理回路の挙動をも選択的にトレースできるマイクロプロセッサを提供する。

【解決手段】 命令を実行して命令の種類及び命令の命令長の情報を生成するプロセッサモジュール3と、プロセッサモジュール3と協調して動作し、特定のアプリケーションを処理するアプリケーション処理回路5と、命令長の情報から命令の実行アドレスを算出するアドレス算出回路43と、算出された実行アドレスが指定アドレス区間内である場合にアプリケーション処理回路5からデータを取得するデータ取得回路44と、取得されたデータを実行状況の情報と共に格納するトレースメモリ46とを備える。

(もっと読む)

局所キャッシュとしてシフトレジスタを使用する論理シミュレーション用のハードウェア加速システム

シミュレーションプロセッサは、複数のプロセッサユニット、およびプロセッサユニットを互いに通信可能に結合する相互接続システムを備える。各々のプロセッサユニットは、少なくとも1つの論理動作をシミュレートするように構成されるプロセッサ要素と、論理シミュレーション時に生成される中間値を記憶するためのシフトレジスタとを備える。各々のプロセッサユニットは、シフトレジスタのエントリの1つを、相互接続システムに結合される出力として選択するための1つまたは複数のマルチプレクサをさらに備える。各々のプロセッサユニットは、シフトレジスタをバイパスして、プロセッサ要素の出力を相互接続システムに直接供給するための経路を提供するために、プロセッサ要素の出力と相互接続システムとの間に結合される1つまたは複数のバイパスマルチプレクサを備えても良い。  (もっと読む)

(もっと読む)

データ推測マイクロプロセッサにおいて実行中のオペレーションのインスタンスがオペレーションのリプレイの割込みを防ぐためのシステム及び方法

オペレーションを実行するように構成された1つ又はそれ以上のファンクショナルユニット(126)、実行のためにファンクショナルユニット(126)へオペレーションを発行するように構成されたスケジューラ(118)、及び少なくとも1つの検出ユニットを含むマイクロプロセッサ(100)である。スケジューラ(118)は各オペレーションに対して状態情報(606)を維持するように構成可能である。そのような状態情報は特に、関連のオペレーションが実行を完了しているかどうかを示す。リプレイ検出ユニットは、スケジューラ内のオペレーションのうちの1つをリプレイする必要があることを検出するように構成可能である。オペレーションはリプレイを必要とすると検出されたとき、ファンクショナルユニット(126)のうちの1つによってそのオペレーションのインスタンスが現在実行中であると、リプレイ検出ユニットは、実行中のオペレーションのインスタンスの実行に応答して、そのオペレーションに対する状態情報(606)への更新を禁止するように構成される。コンピュータシステム(900)のさまざまな実施形態はこのようなマイクロプロセッサ(900)を含む。  (もっと読む)

(もっと読む)

クラスタ化されたILPプロセッサを有するデータ処理システム

本発明は、異なる複数のサイクルからの動作を1つの命令で特定し、その結果、離れたクラスタに対する制御接続をパイプライン化するという考えに基づいている。したがって、データ処理システムが提供される。上記システムは、それぞれが少なくとも1つのレジスタファイルと少なくとも1つの機能ユニットとを備える複数のクラスタを有するクラスタ化されたILPプロセッサと、上記プロセッサのクラスタに対して制御信号を発する命令ユニットとを備えている。命令ユニットは、対応する制御接続を介して上記各クラスタに対して接続されている。また、上記制御接続には、上記命令ユニットと上記クラスタとの間の距離にしたがって、1または複数の更なるパイプラインレジスタを配置することができる。  (もっと読む)

(もっと読む)

VLIWアーキテクチャを拡張させるデータ処理ユニットの効率的及び柔軟性のあるシーケンス動作のための方法及び装置

【課題】シーケンス制御を有する改良した超長命令語プロセッサの提供。

【解決手段】各サイクル期間中に、本プロセッサは命令のフィールド内の値に基づいて機能ユニットに対し制御信号を発生する。各命令はその制御信号がその命令に基づいて発生されるべきサイクル数を特定する繰り返しカウントを包含している。命令セットは、単一命令の繰り返し実行、複数の命令からなるブロックの繰り返し実行、又はプログラム内の分岐を可能とする流れ制御命令を包含している。プロセッサはコンピュータのハードドライブ用のディスク制御器に関連して使用することが可能である。柔軟性のあるシーケンス動作は、ハードドライブ制御器を異なるタイプの媒体に関連して使用すべく容易に再プログラムすることを可能とし、又はディスク制御器がディスクからのデータを回復する能力を増加させるためにディスク読取エラーが検知される場合に動的に再プログラムすることを可能とする。

(もっと読む)

マルチスレッドハードウェアシステム及び方法

【課題】ハードウェアスレッドの数は、ダイエリア及びパフォーマンスによって制限される。

【解決手段】

本発明にかかるマルチスレッドプロセッサシステムは、N個(Nは1以上の整数)のハードウェアスレッドを有するレジスタファイルと、M個(Mは1以上の整数)のハードウェアスレッドを有するオフラインストレージ構造と、N個のハードウェアスレッドのうち少なくとも1つに関連するレジスタ値をM個のハードウェアスレッドのうち少なくとも1つのレジスタに転送し、M個のハードウェアスレッドのうち少なくとも1つのレジスタ値をN個のハードウェアスレッドのうち少なくとも1つのレジスタに転送するスレッド制御機構と、を備える。

(もっと読む)

マルチスレッド・プロセッサにおけるレジスタ・ファイルのポートを削減するための方法および装置

マルチスレッド・プロセッサによるスレッド・ベースのレジスタ・ファイル・アクセスのために技法が開示されている。マルチスレッド・プロセッサは、特定のプロセッサ・スレッドに関連付けられたスレッド識別子を決定し、対応するプロセッサ・スレッドによってアクセスされる関連のレジスタ・ファイルの特定部分を選択するためにスレッド識別子の少なくとも一部分を使用する。例示的な実施形態では、レジスタ・ファイルが偶数部分と奇数部分に分割され、スレッド識別子の最下位ビットまたは他の部分が、所与のプロセッサ・スレッドで使用されるその偶数または奇数部分を選択するために使用される。スレッド・ベースのレジスタ・ファイル選択は、トークン・トリガ・スレッディングおよび命令パイプライン化と共に使用することができる。有利には、本発明は、並行性の所望レベルを維持しつつ、レジスタ・ファイル・ポートの必要数を削減し、したがってプロセッサの電力消費を低減する。  (もっと読む)

(もっと読む)

複数の入力命令をベクトル化する方法及び装置

要約すると、命令トレースの2以上の候補命令を検索し、該2以上の候補命令のトレース依存性の深さ及び共通のオペレーションコードに従って、2以上の候補命令をSIMD(Single Instruction Multiple Data)にマージする最適化ユニット。

(もっと読む)

(もっと読む)

プログラミング可能なモジュールを高度集積システムにおいて階層的および分散的に制御するための装置

本発明は多数の制御モジュール(C1〜C6)を有する装置に関する。この制御モジュールには多数の処理モジュールが制御のために配属されており、独立した制御モジュールは上位の制御装置(DSP)によって制御され、そして共通の同期ユニット(SYNC)によって同期される。この同期ユニットは、例えばハンドシェークやセマフォに基づいて構成される。このような装置は、外部の命令メモリと高度集積システムの間の伝送帯域幅を低減し、今不要な処理モジュールを一時的に遮断することによって総消費電力を低減させることによって可能になる。さらに、このような構造は、個々の制御モジュールに対する制御プログラムを独立して開発する際に有利である。 (もっと読む)

1 - 11 / 11

[ Back to top ]