Fターム[5B015JJ07]の内容

Fターム[5B015JJ07]に分類される特許

1 - 20 / 63

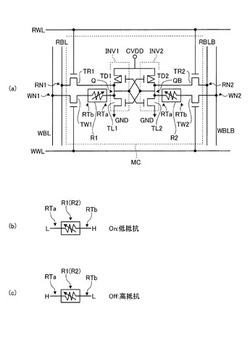

半導体記憶装置

【課題】1つの実施形態は、例えば、電源オフ時における消費電力を低減することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルは、第1の駆動トランジスタと第1の負荷トランジスタと第1の読み出し転送トランジスタと第1の書き込み転送トランジスタと第2の駆動トランジスタと第2の負荷トランジスタと第2の読み出し転送トランジスタと第2の書き込み転送トランジスタと1以上の抵抗変化素子とを有する。1以上の抵抗変化素子は、両端に印加されるバイアスの方向に依存して抵抗が変化する。1以上の抵抗変化素子は、第1の記憶ノード及び第1の書き込み転送トランジスタの間と第2の記憶ノード及び第2の書き込み転送トランジスタの間との少なくとも一方に配される。

(もっと読む)

半導体記憶装置、および、ビット線の充電方法

【課題】低消費電力モードから通常動作モードへの復帰時におけるビット線の充電時間を適切に設定することで、復帰動作で消費される電力を低減する。

【解決手段】半導体記憶装置10は、複数のビット線2a,2b…のそれぞれを充電する充電回路4と、帰還経路5aの配線にダミービット線3が用いられているリングオシレータ5と、リングオシレータ5の発振回数が、複数のビット線2a,2b…の数に基づいて設定された所定の回数に達すると、検出信号を出力するカウンタ6と、低消費電力モードから通常動作モードへの復帰を指示する復帰信号に応じて、充電回路4による複数のビット線2a,2b…の充電を開始させるとともにリングオシレータ5の発振を開始させ、カウンタ6から出力された検出信号に応じて、充電回路4による複数のビット線2a,2b…の充電を終了させる制御回路7と、を有する。

(もっと読む)

半導体装置

【課題】消費電流を低減させる。

【解決手段】半導体装置は、外部端子から供給された外部電源電圧より低い第1内部電圧を第1出力端子から出力する第1降圧回路、外部電源電圧より低い第2内部電圧を第2出力端子から出力する第1モードと第2出力端子から第1及び第2内部電圧より低い第3内部電圧を出力する第2モードとが切替えられる第2降圧回路、第1出力端子に接続され接地電圧が供給される第1SRAMを含む第1内部回路、第2出力端子に接続され接地電圧が供給される第2SRAMを含む第2内部回路とを備え、スタンバイ時に第2降圧回路は第2モードに制御され、第1内部回路の高位電源電圧として第1降圧回路から第1内部電圧が供給されて第1SRAMの記憶内容は保持され、第2内部回路の高位電源電圧として第2降圧回路から第3内部電圧が供給されて第2SRAMの記憶内容は消失される。

(もっと読む)

半導体記憶装置

【課題】SRAM面積の増加を抑制しつつ、サブスレッショルド電流を削減しながらデータ保持が可能となる技術を提供する。

【解決手段】上記の課題を解決するために、メモリセル(3)と、メモリセル(3)のデータを伝達するディジット線(DT0、DB0)と、メモリセル(3)にデータを書き込む書込み回路(17、18)と、書込み回路(17、18)の動作を制御する制御回路(9、11)と、メモリセル(3)のドライバトランジスタのソースに接続されるソース線(SL)と、ディジット線(DT0、DB0)とソース線(SL)との間に設けられたスイッチ回路(21、22)とを具備する半導体記憶装置を構成する。そして、書込み回路(17、18)を、GND電圧を供給する接地線とソース線(SL)と間のダイオードとして機能させる。

(もっと読む)

半導体装置

【課題】複数のメモリモジュールに対する低消費電力モードの解除に際して突入電流の発生を緩和する。

【解決手段】制御信号により低消費電力モードの設定と解除が制御される複数個のメモリモジュール(MDLij)の全部または一部がメモリブロック(BLK0〜BLKm)に属し、同じメモリブロックに属する複数個のメモリモジュールに並列的に前記制御信号を入力してモジュール内経路を伝播させ、その一部のメモリモジュールが前記モジュール内経路から後段のモジュール外経路(EXR_0〜EXR_m)に前記制御信号を出力させるように、制御信号の伝播経路を構成する。このとき、前記一部のメモリモジュールは、これと同一メモリブロック内における他のメモリモジュールよりも大きな記憶容量を有するメモリモジュールとする。

(もっと読む)

半導体装置、それを用いた無線通信端末、及び電源制御方法

【課題】従来の半導体装置は、消費電力が大きくなる問題があった。

【解決手段】半導体装置1は、プログラムとプログラムによって利用されるデータとの少なくとも一方が格納される記憶領域部16と、プログラムを実行して記憶領域部16にバスを介してアクセス要求を発行する機能ブロック11と、バス23上に流れる、記憶領域部16に対するアクセス要求を示す第1の信号REQと、記憶領域部16によるバス23の占有状態を示す第2の信号GNTと、を監視して記憶領域部16へのアクセスが発生していない期間は記憶領域部16をスタンバイ状態に制御し、記憶領域部16へのアクセスが発生している期間は記憶領域部16を活性状態に制御するバス状態監視回路20と、を有し、記憶領域部16は、プログラム又はデータを記憶する記憶セルの低電位側電源電圧と高電位側電源電圧との電圧差を前記スタンバイ状態において活性状態よりも小さくする。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

半導体装置

【課題】ロジックと揮発メモリが混載されたシステムLSIのスタンバイ状態の消費電力を低減する。

【解決手段】システムLSI中のロジック回路と第1電源線の間に第1スイッチを設けるとともに、揮発メモリの少なくとも一部と第1電源線の間に第2スイッチを設ける。スタンバイ時には該第1スイッチと第2スイッチをオフして電源を遮断する。同時に揮発メモリの少なくとも他の一部では、スタンバイ時の基板バイアスを制御してリーク電流を低減する。

(もっと読む)

半導体記憶装置

【課題】消費電力低減が図られた新規な構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ワード線と、ワード線にワード線選択信号を供給するワードドライバと、ワード線に接続されたメモリセルと、メモリセルに電源電圧を供給するセル電源線と、セル電源線への電源電圧の供給状態を制御する電源制御回路とを有し、電源制御回路は、セル電源線に電源電圧が供給されるオン状態と、セル電源線に電源電圧が供給されないオフ状態とを切り替えるスイッチ回路と、ワードドライバからワード線選択信号を供給され、ワード線選択信号が供給される前、スイッチ回路をオフ状態に保持し、ワード線選択信号が供給されると、スイッチ回路をオン状態に切り替え、ワード線選択信号の供給が終了した後も、オン状態を保持するスイッチ制御回路とを有する。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体集積回路装置

【課題】低電圧でSRAM回路を動作させるために構成するトランジスタのしきい値電圧を下げると、トランジスタのリーク電流の増加により、データを記憶しながら動作していない状態での消費電力が増加するという問題がある。

【解決手段】SRAMメモリセルMC内の駆動MOSトランジスタのソース線sslの電位を制御することでメモリセル内のMOSトランジスタのリーク電流を低減する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体集積回路装置

【課題】低電圧でSRAM回路を動作させるために構成するトランジスタのしきい値電圧を下げると、トランジスタのリーク電流の増加により、データを記憶しながら動作していない状態での消費電力が増加するという問題がある。

【解決手段】SRAMメモリセルMC内の駆動MOSトランジスタのソース線sslの電位を制御することでメモリセル内のMOSトランジスタのリーク電流を低減する。

(もっと読む)

半導体装置

【課題】 電源遮断機能付きで記憶容量の増減変更を伴う設計が容易なSRAMマクロを有する半導体装置を提供する。

【解決手段】 本発明の半導体装置では、SRAMのメモリセルが複数配置されているメモリアレイと、メモリアレイへのデータの書き込みおよびメモリアレイからのデータの読み出しを行う第1の周辺回路と、メモリアレイおよび第1の周辺回路と電源線との接続を遮断するスイッチ群とを含むレイアウトの単位が複数配置されている。

(もっと読む)

半導体装置

【課題】レジュームモードからノーマルモードに復帰する際のラッシュカレント(突入電流)のピーク電流を低減することができる半導体装置を提供する。

【解決手段】半導体装置は、複数のディジーチェン接続されたメモリモジュールを備える。各メモリモジュール77−iは、メモリアレイ4と、レジュームモードにおいて、メモリモジュール内の構成要素への電源電圧の供給を制御するスイッチ16と、レジュームモードからノーマルモードへの移行を指示するレジューム制御信号を受けて、次段のメモリモジュールへ、入力されたレジューム制御信号よりもタイミングが遅延したレジューム制御信号を次段のメモリモジュールへ出力する遅延回路42とを含む。

(もっと読む)

スタティック・ランダム・アクセス・メモリ、二次電池装置および車両

【課題】センサの分解能を高めることなく、充電量が均等化に近づくよう調整することを可能とする。

【解決手段】 アクセス判定記憶回路(38)は電源が供給されていないラインへのデータの書き込みを示すアドレス(300)およびコマンド(301)が入力されたとき、この書き込み先アドレスに対応するメモリセルのライン(41)に電源を供給するライン電源回路(37)へ電源回路イネーブル信号(304)をアサートし、ライン電源回路(37)を起動し、このラインについてのステータスデータを<有効なデータが記憶されている>に更新する。また同時に、アクセス判定記憶回路(38)は、書き込みアクセスバッファ(39)に書き込み先アドレスと書き込まれるべきデータを格納させる。ライン電源回路(37)は、書き込み先のライン(41)へ電源を供給する。このデータがラインへ書き込まれたことを確認したら、書き込みアクセスバッファ(39)からこのデータを削除する。

(もっと読む)

半導体集積回路

【課題】書き込み回数に制限がなく、回路規模の増加に対して消費電力を抑制することができる半導体集積回路を提供する。

【解決手段】ルックアップテーブル101とフリップフロップ102Aのラッチ回路以外の回路構成部との電源供給経路を分離し、ルックアップテーブル101とラッチ回路以外の回路構成部とを別個に電源制御する電源コントローラ109及び電源制御回路111を備える。

(もっと読む)

半導体記憶装置

【課題】メモリセルを駆動する周辺回路に電源を供給するスイッチの実装面積を削減することが可能な半導体記憶装置を提供することである。

【解決手段】本発明にかかる半導体記憶装置は、メモリセル12、22、32と当該メモリセルを駆動する周辺回路13、23、33とを備える複数のメモリマクロ10、20、30と、メモリセルへの電源供給を制御する第1の電源スイッチ11、21、31と、周辺回路への電源供給を制御する第2の電源スイッチ40と、を備える。第1の電源スイッチはメモリマクロ内にそれぞれ配置されると共に、メモリセルへ電源を供給する電源線とメモリセルとの間にそれぞれ設けられている。第2の電源スイッチはメモリマクロ外に配置されると共に、電源線61と複数のメモリマクロの周辺回路の共通の電源配線63との間に設けられている。

(もっと読む)

選択的バイアスによって高容量メモリにおけるメモリアレイリークを低減するためのシステムおよび方法

SRAMセルが複数のセクタに配置されたSRAMにおけるリーク低減のためのソースバイアス機構。スタンバイモードでは、複数のセクタ内のセクタ内のSRAMセルは非選択状態にされ、ソースバイアス電位が複数のセクタのSRAMセルに供給される。動作モードでは、複数のセクタ内の選択されたセクタのSRAMセルに供給されるソースバイアス電位は非アクティブにされ、選択されないセクタ内の残りのSRAMセルはソースバイアスされ続けながら、選択されたセクタ内の物理行内のSRAMセルは読み出される。スタンバイモードにあるSRAMセルに供給されるソースバイアス電位は、制御信号の論理状態に基づいて異なる電圧に設定することができる。  (もっと読む)

(もっと読む)

SRAM(StaticRandomAccessMemory)、及びSRAMへのアクセス方法

【課題】保持データを破壊することなくデータの読み出し及び書き込みを行なうSRAMの消費電力を低減する。

【解決手段】本発明によるSRAMは、メモリセル1、列アドレスデコーダ14、プリチャージ制御回路15、プリチャージ回路121を具備する。プリチャージ制御回路15は、外部クロック信号CLKに応じて複数の読み出し用ビット線対RDT0、RDB0〜RDTn−1、RDBn−1に対するプリチャージのタイミングを決定する。プリチャージ回路121は、非選択読み出し用ビット線対RDTj、RDBjをプリチャージせずに、選択読み出し用ビット線対RDTi、RDBiをプリチャージする。

(もっと読む)

1 - 20 / 63

[ Back to top ]