Fターム[5B015JJ11]の内容

Fターム[5B015JJ11]の下位に属するFターム

Fターム[5B015JJ11]に分類される特許

1 - 20 / 148

半導体メモリおよびシステム

半導体記憶装置

【課題】動作速度の低下を抑制しつつ、動作マージンを向上させることが可能な半導体記憶装置を提供する。

【解決手段】速度検知部16は、メモリセルMCの読み出し速度を検知し、電圧制御部17は、メモリセルMCの読み出し速度に基づいてワード線WL1〜WLnの電圧VWLまたはメモリセルMCのセル電源電圧VCSのいずれか少なくとも一方を制御する。

(もっと読む)

半導体記憶装置

【課題】SRAMセルやセンスアンプの駆動トランジスタのしきい値電圧(Vth)を補正することを可能とする技術を提供する。

【解決手段】データを保持するラッチ回路と、データを伝送する信号線とを備える半導体装置を構成する。ラッチ回路は、第1インバータと、第2インバータとを具備する。第1、第2インバータのそれぞれの出力からビット線(BL0、BL1)やセンスアンプ信号線(SA0、SA0B)を経由してGNDへ至る電気的経路を備え、その電気的経路は、第1のトランジスタを備えるものとする。そして、Vt補正モードには、第1インバータまたは第2インバータの一方のHighレベルを供給し他方にLowレベルを供給することで、第1のトランジスタにより電気的経路を導通する。

(もっと読む)

半導体記憶装置

【課題】メモリセルのサブスレッショルド・リーク電流の影響によって不良となるデバイスを選別検査で確実にリジェクトする。

【解決手段】行列状に配置された複数のメモリセルMEMと、メモリセルの行に対応して設けられた複数のワード線WL0〜WL4と、メモリセルの列に対応して設けられた複数のビット線対BT0、BB0及びBT1、BB1と、前記複数のワード線のうち、検査対象の注目メモリセル以外の非注目メモリセルが接続された非注目ワード線をフローティングとするスイッチMN1と、前記非注目ワード線がフローティングのときに、当該非注目ワード線を昇圧するポンピング回路POC0とを備える。

(もっと読む)

半導体記憶装置およびそのテスト手法

【課題】短時間でライト動作不良をテストすることができる、半導体記憶装置、及びそのテスト方法を提供すること。

【解決手段】非テスト対象ポートに対応するワード線を活性化させ、非テスト対象ポートに対応するプリチャージ信号を非活性にすることにより、非テスト対象ポートに対応する前記ディジット線対の一方を放電させる。放電後の前記ディジット線対の電位差が保たれた状態で、複数のワード線を活性化させ、テスト対象ポートに対応するディジット線対を駆動することにより、メモリセルにテストデータを書き込む。その後、メモリセルからデータを読み出し、テストデータが正しく書き込まれていたか否かを判定する。

(もっと読む)

半導体記憶装置

【課題】データ読み出し速度の低下を抑制しつつ、記憶データの破壊を抑制できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルが行列状に配置されたSRAMセルアレイ102と、ワード線WL_1〜WL_mと、ワード線WL_1〜WL_mをそれぞれ駆動するワード線ドライバ104_1〜104_mと、電源電圧VDDに対するMOSトランジスタの閾値電圧Vthの比率が高い場合には、Hレベルの判定結果信号ENを出力し、電源電圧VDDに対するMOSトランジスタの閾値電圧Vthの比率が低い場合には、Lレベルの判定結果信号ENを出力する閾値電圧判定回路105と、比較結果に応じた電源電圧VDRVをワード線ドライバ104_1〜104_mに供給する可変電圧源106と、を備える。

(もっと読む)

半導体記憶装置

【課題】トランスファMOSトランジスタが正常に動作しない場合の不良を検出する。

【解決手段】半導体記憶装置(31)は、スタティック型のメモリセル(MC)と、ワード線(WL1〜WLm)と、ビット線(BL1,/BL1〜BLn,/BLn)とを含む。また上記半導体記憶装置(31)は、上記ビット線を上記メモリセルに結合するためのトランスファMOSトランジスタ(11,14)と、上記ビット線をハイレベルに駆動するための第1駆動回路(17,18,21,22)と、上記ビット線をローレベルに駆動するための第2駆動回路(19,20,23,24)とを含む。このとき、テストモードにおいて、上記第1駆動回路によるビット線駆動機能を停止させるための制御論理(26)を設けることで、トランスファMOSトランジスタが正常に動作しない場合の不良を検出可能にする。

(もっと読む)

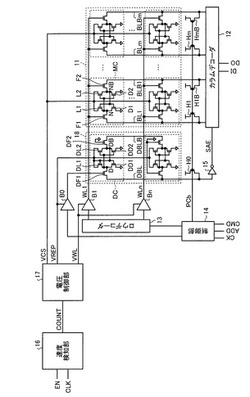

ワード線電位制御回路

【課題】製造バラツキや動作温度などに応じてワード線電位を適正化する。

【解決手段】複数のメモリセルMCがアレイ状に配列されたメモリセルアレイ1において、メモリセルMCの特定の特性を制御し、メモリセルMCの特定の特性が制御された時の特性の分布に基づいて、ワード線wl_0〜wl_mの電位を調整する。リード/ライト回路7を介してメモリセルアレイ1の全てのメモリセルMCからデータが読み出される。そして、カウンタ8において、メモリセルMCから読み出されたデータの反転数がカウントされ、コンパレータ11に出力される。また、セレクタ10において、期待値N2が選択され、コンパレータ11に出力される。そして、コンパレータ11において、メモリセルMCから読み出されたデータの反転数と期待値N2が比較され、その比較結果がソース電位制御部13に送られる。

(もっと読む)

半導体記憶装置

【課題】リーク電流に起因した半導体記憶装置の誤動作を抑制する。

【解決手段】半導体記憶装置1は、グローバルビット線50及びそれに接続された複数の回路ブロック30を有する。各回路ブロック30は、メモリセル部11、センスアンプ22、及びセンスアンプ22の出力をゲート入力とし、ドレインがグローバルビット線50に接続されたプルダウントランジスタ23を含む。センスアンプ起動信号SAEに基づき、一の回路ブロック30が選択されたときには、選択された回路ブロック30のプルダウントランジスタ23のソースがHレベルになり、非選択の回路ブロック30のプルダウントランジスタ23のソースがLレベルになる。

(もっと読む)

半導体記憶装置

【課題】信号処理で重要となるマルチポート半導体記憶装置を提供する。

【解決手段】第1のビット線に接続される2つのデータ保持ノードを有してクロスカップル接続されたインバータからなるラッチ回路と、第1のビット線とインバータの各データ保持ノードとの間に設けられた第1のスイッチ部と、第1のスイッチ部の導通を制御する第1のワード線とを備えて構成されるメモリセルを備える。複数個のメモリセルの各データ保持ノードを各メモリセル毎にそれぞれ分離して1ビットが1個のメモリセルで構成される第1のモードと、複数個のメモリセルの各データ保持ノードを並列に接続して1ビットが複数個のメモリセルで構成される第2のモードを切り換える第2のスイッチ部とを備え、複数個のメモリセルの各データ保持ノードのうちの1つのデータ保持ノードを第2のビット線に接続するか否かを切り換える第3のスイッチ部をさらに含む。

(もっと読む)

半導体記憶装置とそのセルリーク検出方法

【課題】SRAM回路の製品信頼性が低下する問題があった。

【解決手段】セルリークの判定機能を有した半導体記憶装置であって、相補性ビット線対と、前記ビット線対に接続され、セル選択時に前記ビット線対に印加された値に応じた値をセルノードに記憶するメモリセルと、セルリークテスト期間において、選択状態の前記メモリセルに対し、前記ビット線対の一方に第1の値を印加させ、その後、非選択状態の前記メモリセルの駆動電源の供給を停止し、且つ、前記ビット線対の一方に対して前記第1の値と逆の第2の値を印加させ、前記ビット線対の一方に対応する側の前記メモリセルの第1のセルノードの値に応じて、当該半導体記憶装置のセルリークを判定するテスト制御回路と、を有する半導体記憶装置。

(もっと読む)

メモリ内のワード線電圧制御

【課題】メモリ内のワード線電圧制御。

【解決手段】メモリ回路2は、ワード線20上のワード線電圧で読み出すために選択されたビットセル4を含む。ワード線電圧制御回路26は、2ステップワード線電圧信号を生成する。ワード線電圧は、ワード線トランジスタ12がビットセル4をビット線8に弱く結合する中間レベルまで最初に増加する。この中間レベルは第1の遅延期間にわたって維持される。第1の遅延期間後に、ワード線電圧は、フルレール値まで増加され、このフルレール値は、第2の遅延期間にわたって維持される。ワード線電圧は、次いで、読み出し動作の終わりに低レベルに戻される。この2ステップワード線電圧信号は、ビットセル4に対してより良好なアクセス妨害マージンを提供する。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

半導体集積回路

【課題】トランジスタの性能の劣化の防止に有利な半導体集積回路を提供する。

【解決手段】実施形態によれば、半導体集積回路は、ワード線とビット線との交差位置にそれぞれ配置されデータを保持するデータ記憶部(SRAMセル)と前記データ記憶部に記憶された保持データを論理的に反転させる反転回路22と、前記データ記憶部が記憶するデータの論理反転の有無を識別するフラグをロウ単位で記憶するフラグビットカラム11−1とを備える、メモリセルアレイ11を具備する。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】ワード線ドライバ(WDK)をグループに分割し、各グループに対応して、ワード線ドライバにアレイ電源線から第1の電圧を生成して、選択グループのワード線ドライバに伝達するドライバプリチャージ回路(DPG)を配置するとともに、各ドライバプリチャージ回路毎にこの第1の電圧をシフトダウンさせるレベルシフト回路(LSFN)を設ける。

(もっと読む)

パルス幅制御回路及び半導体メモリ

【課題】トランジスタのプロセス依存と配線幅のばらつきとに応じて適切なパルス幅に制御することが可能なパルス幅制御回路及び半導体メモリを提供すること。

【解決手段】配線による遅延とインバータによる遅延とを比較する比較回路と、インバータ段数によりパルス幅を調整するパルス幅調整回路と、を備える。パルス幅調整回路は、比較回路の比較結果に基づいて、インバータによる遅延が配線による遅延よりも小さくなった場合に、インバータ段数を多くし、パルス幅を増加させる。

(もっと読む)

半導体回路装置及び誤り検出回路

【課題】データ書き込み時の方向と直交する方向に連続するメモリセルに記憶されたデータ列を該データ列単位で順次読み出すことが可能な半導体回路装置において、前記読み出したデータ列の誤り検出を行うのに好適な半導体回路装置を提供する。

【解決手段】半導体回路装置1の誤り検出回路43を、列誤り検出回路50_0〜50_nと、誤り検出用OR回路51とを含んだ構成とし、各列誤り検出回路において、LCDからのクロック信号LCD_CKに同期してメモリセルアレイ21から行単位に順に読み出される表示用データLCD_RDの、1ライン目の読み出し時において同じ1周期にパリティデータPTDを読み出し、行単位で順次読み出される各ラインにおける列方向に書き込まれた各ビットデータと1つ前の演算結果との排他的論理和演算を順次行い、表示用データCPU_WDに対する最終的な演算結果を誤り検出用OR回路51に出力する構成とした。

(もっと読む)

半導体記憶装置

【課題】ライトバック方式にて書き込みディスターブに対処することを可能としつつ、消費電力を低減する。

【解決手段】半導体記憶装置には、メモリセル2と、ライトバック判定部7と、読み出し制御部8とが設けられている。メモリセル2は、別個の経路を介して書き込みと読み出しとを行うことができる。ライトバック判定部7は、選択カラムの書き込み時に、非選択カラムについてのライトバックを行うかどうかを判定する。読み出し制御部8は、ライトバック判定部7の判定結果に基づいて、非選択カラムについてのライトバックに用いられるデータの読み出しを制御する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置のライトマージンの低下を抑制しつつ、ディスターブ不良を低減する。

【解決手段】実施形態によれば、メモリセル12と、ダミーセル16と、書き込み制御部と、ロウデコーダ13が設けられている。メモリセル12は、データを記憶する。ダミーセル16は、メモリセル12の動作を模擬する。書き込み制御部は、メモリセル12の書き込みタイミングに合わせてダミーセル16に書き込みを行わせる。ロウデコーダ13は、ダミーセル16の書き込み状況の監視結果に基づいて、メモリセル16のロウ選択を行うワード線WLの開閉を行う。

(もっと読む)

半導体記憶装置

【課題】高速動作可能なメモリセルにも適用できる、読み出しワード線RWL及び書き込みワード線WWLの信号を発生させるサブワードドライバーを有する半導体記憶装置を提供する。

【解決手段】読み出しワード線と、書き込みワード線と、メーンワード信号と反転読み出しブロック信号とにより前記読み出しワード線を選択し、前記メーンワード信号と反転書き込みブロック信号とにより前記書き込みワード線を選択するサブワードドライバーとを有することを特徴とする半導体記憶装置。

(もっと読む)

1 - 20 / 148

[ Back to top ]