Fターム[5B015KB00]の内容

S−RAM (6,838) | 周辺回路 (1,491)

Fターム[5B015KB00]の下位に属するFターム

データ線まわり (120)

センスアンプ回路 (274)

ライトアンプ回路 (33)

データ入出力まわり (141)

アドレス回路まわり (169)

電源供給回路 (391)

内部クロック信号作成回路 (167)

その他の回路 (194)

Fターム[5B015KB00]に分類される特許

1 - 2 / 2

半導体記憶装置

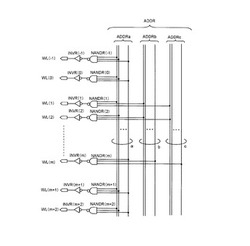

【課題】行選択回路の小面積化と製造時の露光、エッチング等の影響を解消する半導体記憶装置を実現する。

【解決手段】アドレス入力に応じて所望のワード線を選択するように行アドレス信号と接続されたワード線選択回路と、疑似メモリセルのワード線に接続された疑似ワード線電位固定回路とを備え、疑似ワード線電位固定回路をワード線選択回路と同様にNANDゲートNANDR(i)(i=−1〜m+2)とインバータINVR(i)(i=−1〜m+2)で構成し、疑似ワード線電位固定回路の入力は疑似メモリセルのワード線を常に非選択となるように行アドレス信号と接続されている。これにより全てのワード線を選択駆動する回路の構成を同一とすることが可能となり、行選択回路の小面積化と製造時の露光、エッチング等の影響を解消することが可能となる。

(もっと読む)

半導体集積回路

【課題】集積回路内では、それぞれの回路の事情により最適なゲート長とゲート酸化膜厚としきい値電圧があることになる。これらの回路を同一基板上に集積する半導体集積回路では、それぞれの回路の最適な値にするために製造工程が複雑化し、結果として歩留まりの低下、製造日数の増加に伴い製造コストの上昇をもたらす。

【解決手段】論理回路には高低2種類のしきい値のトランジスタを用い、メモリセルには高しきい値電圧と同じしきい値電圧のトランジスタにより構成し、入出力回路は上記の高しきい値電圧と同じチャネルの不純物濃度でゲート酸化膜厚を厚くしたトランジスタを用いて構成する。

(もっと読む)

1 - 2 / 2

[ Back to top ]