Fターム[5B016AA01]の内容

位取り記数法を用いた四則演算 (704) | 目的、効果 (145) | 高速化 (66)

Fターム[5B016AA01]に分類される特許

1 - 20 / 66

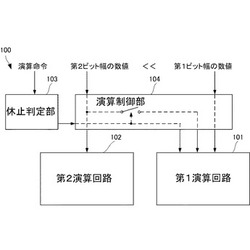

浮動小数点演算回路、浮動小数点演算回路を備えたコンピュータ及びその演算制御方法と演算制御プログラム

【課題】拡張精度演算回路と単・倍精度演算回路とにより単精度同士/倍精度同士の並列演算を実現し、演算処理を高速化して演算実行時間を短縮できること。

【解決手段】第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、演算命令に基づいて、第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定部と、休止判定部が前記第1演算回路が休止すると判定した場合に、第1演算回路を第2ビット幅の数値の演算を行なうよう制御し、第2ビット幅の数値の演算を、第1演算回路と第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御部と、を備えることを特徴とする。

(もっと読む)

乗算回路

【課題】乗算回路における電流発生を抑止するとともに演算時間を短縮する。

【解決手段】

入力値生成部は所定のデコード単位ごとに被乗数データおよび乗数データを区切って、区切られた被乗数データおよび乗数データの複数の部分乗算結果を、区切られた被乗数データおよび乗数データよりも広いデータ幅を有する固定値から所定ビット数だけ異なる値を示すデコードデータとして生成する。乗算部は、入力値生成部によって生成された複数の部分乗算結果のデコードデータを、対応する桁のデコード単位ごとに加算することによって、デコードされた乗算データを生成する。エンコーダは、乗算部によって生成されたデコードされた乗算データをデコード単位ごとにエンコードすることによって、被乗数データと乗数データとの間の乗算結果を出力する。

(もっと読む)

多倍長演算装置、暗号化装置、復号装置、演算方法、プログラムおよび記録媒体

【課題】 小さな回路規模で高速に多倍長演算を実現する多倍長演算装置を提供すること。

【解決手段】 本発明の多倍長演算装置110は、直列接続される複数の多ビット加算器120を含む。本多ビット加算器120は、各々が多倍長数の一部を構成する被加数および加数が入力される入力部A,Bと、被加数と加数との下位ビットを加算し、和の下位ビットを出力する下位ビット加算器122と、加数の上位ビットが被加数の上位ビットに対する減基数の補数であるという関係を満たすか否かを判定する判定回路124と、被加数および加数の上位ビットを加算する第1上位ビット加算器126と、被加数と加数との上位ビットを加算する第2上位ビット加算器128と、判定の結果に対応して第1上位ビット加算器126または下位ビット加算器122の桁上がりを当該多ビット加算器120の桁上がり出力として選択する選択回路130とを含む。

(もっと読む)

定数乗算装置

【課題】装置規模を小型化し、且つ演算速度を高速化することが可能な定数乗算装置を提供する。

【解決手段】2進6桁の被乗数Yの、各桁中に含まれる「1」の個数が4である場合に、12列、3段の複数の加算点を設定し、被乗数Yの最も下の位の「1」が第1桁に存在する場合に、第1段の、第1列から第6列までの加算点の各a入力にN桁の乗数Xの、第1桁から第N桁までの各数値を入力する。また、第2〜第3段の各加算点に、乗数Xを所定の桁だけシフトした数値を入力する。そして、各加算点の3つの入力のうち2以上が常時0となる場合は、この加算点に加算器を設置せず、1つの入力が常時0となる場合にはこの加算点に半加算器(HA)を設置し、それ以外の加算点に全加算器(FA)を設置する。このような構成により、装置規模を小型化し、更に演算速度を高速化することができる。

(もっと読む)

ロジスティック写像の演算装置

【課題】ロジステック写像の演算を高速で実行することが可能な演算装置を提供する。

【解決手段】ロジステック写像の桁数が6桁である場合に、6段、5列の加算器を備える配列型乗算器を用いてロジステック写像の漸化式を展開した「Xt*notXt+Xt」の演算を実行する。この場合、第1段の各加算器に「Xt」のビット列であるx0〜x5を入力することにより「Xt」の加算処理が実行さえる。従って、別途「Xt」を加算する処理を実行することなく、ロジステック写像を演算することができ、従来と対比して「Xt」を反転して「+1」とする処理が不要となるので、ロジステック写像の演算速度を高速化することが可能となる。

(もっと読む)

浮動小数点除算器、及びそれを用いた情報処理装置

【課題】演算TATを短縮して、性能向上と消費電力低減効果を実現できる浮動小数点除算器を提供する。

【解決手段】浮動小数点除算器は、2進数の減算シフト型である。この浮動小数点除算器は、仮数繰り返し処理部250と、演算実行制御部200とを具備する。仮数繰り返し処理部250は、入力オペランドにおける被除数の仮数の減算シフト処理により商と部分剰余とを生成する。演算実行制御部200は、部分剰余に関して、演算実行処理における基数によって一意に決定される特定の位置のビット値を判定する。仮数繰り返し処理部250は、演算実行制御部200の判定結果に基づいて、減算シフト処理の1回につき生成される商のビット数と部分剰余の左シフトビット数に対して、それぞれ2倍の商生成及び部分剰余の左シフト処理を行うことで、減算シフト処理回数を削減する。

(もっと読む)

演算処理装置、その制御方法および演算処理プログラム

【課題】簡易な手順で高基数除算を実行可能にする。

【解決手段】補正値算出部15は、被除数Aに基づく被除数ゼロカウント値と除数Bに基づく除数ゼロカウント値とnの値とに基づいて、ループカウント値の補正値を算出する。補正ループカウント値算出部16は、被除数ゼロカウント値と除数ゼロカウント値と補正値とに基づいて、補正ループカウント値を算出する。被除数シフト部17は、被除数Aの絶対値を、被除数ゼロカウント値と補正値とに基づく桁数だけシフトする。除数シフト部18は、除数Bの絶対値を、除数ゼロカウント値に基づいてシフトする。除算ループ処理部20は、被除数シフト部17からの出力値と除数シフト部18からの出力値と補正ループカウント値とに基づいて、除算演算を実行する。

(もっと読む)

計算装置、計算方法及びプログラム

【課題】格子を用いた計算において計算処理を高速化することを目的とする。

【解決手段】格子の横軸であるmの値が大きくなる方向に格子の接点の値を計算していく際に、m=n−1にダミーの接点を追加して、SIMD機能を利用してm=n−1の接点の値と追加したダミーの接点の値とを用いてベクトル演算することで、m=nの接点の値を求めることができるように、追加するダミーの接点を決定する決定手段と、決定手段で決定されたダミーの接点をm=n−1に追加する追加手段と、SIMD機能を利用してm=n−1の接点の値と追加手段で追加されたダミーの接点の値とを用いてベクトル演算することで、m=nにある接点の値を算出する算出手段と、を有することによって課題を解決する。

(もっと読む)

ガロア体上の元の除算演算回路

【課題】除数の制限がなく、標数Pと標数2の何れの除算演算処理も回路規模を増加させずに実現できるようにする。

【解決手段】シフトレジスタ12に格納された被除数Aの上位桁から順にシフトしていって、被除数Aの上位5ビットを見る。レジスタ30は、現在の最高次の値であり、これが「1」となった時に減算が実行される。レジスタ30の値が「1」になると、論理積素子32〜38は、レジスタ14〜22からの除数Bの値を出力し、排他的論理和素子40〜46において減算が実行される。レジスタ30の出力は、そのままシフトレジスタ48に格納され、これが商となる。このような処理動作は、被除数Aの全ビットが出力されるまで実行され、被除数Aがmビットであればmクロックで動作を止める。その時のレジスタ24〜30の値が剰余となり、レジスタ30の値が最上位桁(MSB)となる。

(もっと読む)

量子演算方法、量子演算装置、量子回路

【課題】補助キュービットを使うことなく、従来よりも効率的な量子演算技術を提供する。

【解決手段】2つの2進数a=an-1…a0及びb=bn-1…b0と、0または1のzとに対し、a+b=sn…s0と、z(+XOR)snとを算出する量子演算であって、n個のキュービットBiと、n+1個のキュービットAjを演算対象とし、キュービットBiの初期状態を|bi〉とし、キュービットAiの初期状態を|ai〉とし、キュービットAnの初期状態を|z〉として、キャリービットciが初期状態|ai〉を与えられたキュービットAiに蓄えられる。これは、MAJゲートを二つの制御NOTゲートを含む前段部と一つのToffoliゲートを含む後段部に分けて、MAJゲートの作用を複合的に利用することで達成される。

(もっと読む)

NAF変換装置

【課題】回路規模が小さくスケーラブルなw−NAF変換装置を提供する。

【解決手段】2進表現された整数をw−NAF表現された冗長2進表現に変換するNAF変換装置であって、前記2進表現された整数を下位から1ビットずつ受け付ける受付手段と、1ビットで表現される状態の値を記憶する記憶手段と、w−1ビットで表現される状態の値を記憶するシフトレジスタと、前記受付手段が受け付けた1ビットの値と、前記記憶手段の状態の値と、前記w−1ビットのシフトレジスタの状態の値を参照し、次の時刻における前記記憶手段の状態と前記w−1ビットのシフトレジスタの状態とを決定し、現時刻におけるwビットのパラレル出力を決定する更新手段と、を具備する。

(もっと読む)

半導体装置

【課題】演算の高速化を図り、また、小型化を図ることで並列度を高めることが可能な半導体装置を提供する。

【解決手段】半導体装置201は、乗数を示す3ビットの第1の乗数データを受けて、ブースのアルゴリズムに従い、シフトフラグ、反転フラグおよび演算フラグを出力するデコーダDEC1,DEC2と、被乗数を示す2ビットの第1の被乗数データと、シフトフラグ、反転フラグおよび演算フラグとを受けて、シフトフラグに基づいて第1の被乗数データの上位ビットおよび下位ビットのいずれかを選択し、選択したビットを反転フラグに基づいて反転または非反転し、反転または非反転されたデータおよび所定の論理レベルのデータのいずれかを演算フラグに基づいて選択し、第1の乗数データおよび第1の被乗数データの部分積を示す部分積データとして出力する第1の部分積算出部31〜38とを備える。

(もっと読む)

デジタル演算回路

【課題】算器の消費電力を削減すると共に、乗算器の演算速度の低下を抑制する。

【解決手段】乗算器20は、第1の端子22に乗数が入力され、第2の端子24に被乗数が入力される。制御回路30は、乗算されるAとBについて、いずれを乗数としたほうが乗算器20による乗算にキャリの発生回数が少ないかを判定すると共に、キャリの発生が少ない乗算が行われるように、AとBの片方を第1の端子22と第2の端子24の片方に入力し、AとBの他方を第1の端子22と第2の端子24の他方に入力する。

(もっと読む)

演算器及び演算器設計方法

【課題】入力データ数やビット幅が大きい場合の多入力加算、符号付のビット幅混合加算における高速な演算が可能な演算器、及び演算器の設計方法を提供することを目的とする。

【解決手段】演算器1は、レジスタ100と、入力信号102が入力される部分積展開部104と、部分積展開部104から信号106が入力されるカウンタ部110と、カウンタ部110から出力信号115が入力されるsum部レジスタ120と、カウンタ部110から出力信号115の桁の桁上げとして出力信号125が入力されるcarry部レジスタ130を備え、桁毎の遅延を予測し、予測した遅延に影響しない範囲でカウンタの適用とキャリーセーブのビット幅を最適化し、次の演算器を含めた演算器全体の遅延を最適化したことにより高速な演算器1及び演算器1の設計方法を得ることができる。

(もっと読む)

計算機

【課題】SIMD型計算機やベクトル型計算機に適用可能な、特定の初期値を検出して別処理を行うことを不要とする、ソフトウェアシーケンスによる高性能な除算を実行する。

【解決手段】符号および仮数と、指数とを分解し、2者を別々に計算する除算用の計算機において、符号および仮数を取り出す演算器と、2つの数の指数の差を取り出す演算器を設ける。

(もっと読む)

演算装置、画像表示装置、および演算方法

【課題】乗算における加算および減算の最大回数を低減することで、演算装置の小型化および演算速度の向上を図ることができる技術を提供する。

【解決手段】二進法に係る被乗数と乗数との乗算を行う演算装置において、乗数におけるビットの数値の下桁側からの配列に応じて、加算基調の演算を行った後に、該加算基調の演算および減算基調の演算のうちの少なくとも一方の演算を順次に行うことを決定する。ここで、加算基調の演算では、乗数におけるビットの数値が下桁側から順に1、0となる場合に被乗数に係る加算を行い、下桁側から順に1、1となる場合に減算基調の演算に移行しつつ被乗数に係る減算を行う。また、減算基調の演算では、符号拡張乗数におけるビットの数値が下桁側から順に0、1となる場合に被乗数に係る減算を行い、下桁側から順に0、0となる場合に加算基調の演算に移行しつつ被乗数に係る加算を行う。

(もっと読む)

信号処理プロセッサ及び半導体装置

【課題】複数のデータ語長への飽和処理を効率良く行える信号処理プロセッサ及び半導体装置を提供すること。

【解決手段】デコード部110とレジスタ部と命令実行部130とを含む信号処理プロセッサ100であって、命令実行部130は、読み出し処理部140と、演算部150と、飽和処理部160と、書き出し処理部170と、を含みレジスタ部は、飽和処理において飽和させる語長を特定する飽和語長調情報124を含む飽和情報が保持された飽和情報保持部120を含み、飽和処理部160は、飽和語長情報124によって特定される語長に対応した飽和処理を行う。

(もっと読む)

N桁減算器ユニット、N桁減算器モジュール、N桁加算器ユニット及びN桁加算器モジュール

【課題】基本となる桁数のモジュール内では桁借り、桁上げが伝搬しないN桁加減算器ユニット及びN桁加減算器モジュールを提供する。

【解決手段】本発明は、加減算器のうち特に加減算の規則性に基づき、被加減数と加減数の関係から加減算結果の出力パターンを予見し、基本となる桁数のモジュール内では桁借り、桁上げが伝搬しないN桁加減算器ユニット及びそれを用いたN桁加減算器モジュールを特徴とする。

(もっと読む)

量子回路、量子演算装置及び量子演算方法

【課題】補助量子ビットを用いず、近傍量子ビット演算だけを使い、線形サイズ、線形深さで二進数a,bの和a+bを計算する技術を提供する。

【解決手段】二進数bの各桁は小さい方から量子ビットQ2i+1(i=0,…,n−1)の初期状態にそれぞれ対応し、二進数aの各桁は小さい方から量子ビットQ2i+2(i=0,…,n−1)の初期状態にそれぞれ対応する。図20に示す量子演算操作が、量子ビットQ1,…,Q2n+1に対して図16から図19に示す量子操作を行う。n=5の場合の量子回路を図1から図5に示す。和a+bの各桁は小さい方から量子ビットQ2i+1(i=0,…,n)の操作後の状態にそれぞれ対応する。

(もっと読む)

除算器および除算方法、並びに除算器を用いた画像符号化装置

【課題】量子化処理のための除算演算処理の高速化を図る。

【解決手段】被除数のうち所定ビットよりも上位ビットの被除数が、除数よりも小さいか否か比較判定し、上位ビットの被除数が除数よりも小さい場合には、商のうち上位ビットに対応するビットの商をゼロとするとともに、所定ビット以下の下位ビットの被除数を除数で除算して、下位ビットに対応するビットの商を求めることにより、被除数を除数で除算した商を求める。

(もっと読む)

1 - 20 / 66

[ Back to top ]