浮動小数点演算回路、浮動小数点演算回路を備えたコンピュータ及びその演算制御方法と演算制御プログラム

【課題】拡張精度演算回路と単・倍精度演算回路とにより単精度同士/倍精度同士の並列演算を実現し、演算処理を高速化して演算実行時間を短縮できること。

【解決手段】第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、演算命令に基づいて、第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定部と、休止判定部が前記第1演算回路が休止すると判定した場合に、第1演算回路を第2ビット幅の数値の演算を行なうよう制御し、第2ビット幅の数値の演算を、第1演算回路と第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御部と、を備えることを特徴とする。

【解決手段】第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、演算命令に基づいて、第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定部と、休止判定部が前記第1演算回路が休止すると判定した場合に、第1演算回路を第2ビット幅の数値の演算を行なうよう制御し、第2ビット幅の数値の演算を、第1演算回路と第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御部と、を備えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スーパーコンピュータのベクトル演算などで高速な浮動小数点演算を行なうための演算技術に関する。

【背景技術】

【0002】

現在、スーパーコンピュータでは、単精度と倍精度と拡張精度の3種のデータを浮動小数点演算する必要がある。特に、ベクトル演算などでは、1つの演算処理が浮動小数点演算の多数回の繰り返しを含むため、各々の浮動小数点演算の短縮が演算処理の高速化に寄与する。また、回路構成を簡単にすることも演算処理の高速化に寄与する。たとえば、特許文献1では、128ビットの拡張精度データ幅の演算データを64ビット幅の上位と下位とに分け、64ビット幅の演算回路での2回の実行で1つの拡張精度データ幅の演算結果を求める。これにより、拡張精度データ幅の演算を少ないハードウェアにより実行できる。また、特許文献2では、16バイト幅(=128ビット幅)の演算器を2つの8バイト幅(=64ビット幅)に分割する。そして、分割した2つの8バイト幅の演算器で、8バイト幅(=64ビット幅)と4バイト幅((=32ビット幅))の演算データの演算を同時に実行できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平06−149544号公報

【特許文献2】特開平09−091118号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、単精度と倍精度と拡張精度の3種のデータを浮動小数点演算する場合にも、演算処理を高速化して演算実行時間を短縮するには、演算を並列に同時実行することが望ましい。また、限られたハードウェア資源を効率よく使用して演算処理を高速化して演算実行時間を短縮することで、業務の効率化とコンピュータシステムの消費電力が抑制できるハードウェアの提供が求められている。

【0005】

これに対して、上記特許文献1は、倍精度(64ビット=8バイト)の演算回路を使って拡張精度(128ビット=16バイト)の演算を実行するのみであり、いずれの演算もシーケンシャルにしか実行できない。一方、上記特許文献2は、拡張精度(16バイト=128ビット)の演算器を使って、単精度(4バイト=32ビット)と倍精度(8バイト=64ビット)の演算を同時に実行可能である。しかし、単精度同士/倍精度同士の並列演算はできない。

【0006】

本発明の目的は、上述の課題を解決する技術を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明に係る装置は、

第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、

演算命令に基づいて、前記第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定手段と、

前記休止判定手段が前記第1演算回路が休止すると判定した場合に、前記第1演算回路を前記第2ビット幅の数値の演算を行なうよう制御し、前記第2ビット幅の数値の演算を、前記第1演算回路と前記第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御手段と、

を備えることを特徴とする。

【0008】

上記目的を達成するため、本発明に係る装置は、

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

当該浮動小数点演算回路への演算命令が、拡張されたビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が拡張されたビット幅の数値に対する演算であると判定した場合は、前記拡張されたビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が拡張されたビット幅の数値に対する演算でないと判定した場合は、前記拡張されたビット幅より短いビット幅の数値の浮動小数点演算を実行する演算実行手段と、

を備えることを特徴とする。

【0009】

上記目的を達成するため、本発明に係る装置は、

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止するか否かを検出して、演算実行中フラグを生成する演算実行中フラグ生成回路と、

前記演算実行中フラグ生成回路が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、

入力される拡張されたビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第1レジスタ群と、

入力される拡張されないビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第2レジスタ群と、

前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を実行することを示す場合には前記第1レジスタ群を選択し、前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止することを示す場合には前記第2レジスタ群を選択する符号、指数及び仮数選択回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、演算結果の符号を生成する符号生成回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、被演算データの指数と演算データの指数とを調整して演算結果の指数を生成する指数生成回路と、

前記指数生成回路における前記被演算データの指数と演算データの指数との調整に対応して、被演算データの仮数と演算データの仮数との桁合わせを行なって演算結果の仮数を生成する仮数演算回路と、

前記演算結果の指数と仮数とを整合する整合回路と、

前記演算結果の符号と、前記整合回路で整合された前記演算結果の指数と仮数とを格納する演算結果格納レジスタとを備え、

前記実行中フラグ格納レジスタに格納された前記実行中フラグと、前記演算結果格納レジスタに格納された前記演算結果の符号、指数及び仮数とを、浮動小数点演算結果として出力することを特徴とする。

【0010】

上記目的を達成するため、本発明に係る装置は、

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータであって、

第1演算回路が、

当該第1演算回路への演算命令が、第1ビット幅の数値に対する演算であるか前記第1ビット幅より短い第2ビット幅の数値に対する演算であるかを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合に、前記第1ビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が前記第2ビット幅の数値に対する演算であると判定した場合に、前記第2ビット幅の数値の浮動小数点演算を実行する演算実行手段と、を有し、

第2演算回路が、前記第2ビット幅の数値の浮動小数点演算を実行する回路であって、

前記浮動小数点演算回路への演算命令が前記第1ビット幅の数値に対する演算が休止することを示す場合には、前記第2ビット幅の数値の浮動小数点演算を前記第1演算回路と前記第2演算回路とにより並列に実行することを特徴とする。

【0011】

上記目的を達成するため、本発明に係る方法は、

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御方法であって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、

を含むことを特徴とする。

【0012】

上記目的を達成するため、本発明に係るプログラムは、

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御プログラムであって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、をコンピュータに実行させることを特徴とする。

【発明の効果】

【0013】

本発明によれば、拡張精度演算回路と単・倍精度演算回路とにより単精度同士/倍精度同士の並列演算を実現し、演算処理を高速化して演算実行時間を短縮できる。

【図面の簡単な説明】

【0014】

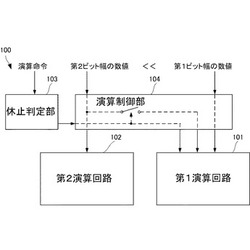

【図1】本発明の第1実施形態の浮動小数点演算回路の構成を示すブロック図である。

【図2A】本発明の第2実施形態に係る浮動小数点演算回路を含むコンピュータの構成を示すブロック図である。

【図2B】本発明の第2実施形態に係る浮動小数点演算回路を含むコンピュータの演算処理手順を示すフローチャートである。

【図3】本発明の第2実施形態に係る浮動小数点演算回路に含まれる浮動小数点加減算回路の構成を示すブロック図である。

【図4】本発明の第2実施形態に係る浮動小数点加減算回路に含まれる拡張精度データ幅演算回路の構成を示すブロック図である。

【図5】本発明の第2実施形態に係る浮動小数点加減算回路に含まれる単精度・倍精度データ幅演算回路の構成を示すブロック図である。

【図6】本発明の第2実施形態に係る科学演算データ形式の一例を示す図である。

【図7】本発明の第2実施形態に係る演算命令生成の論理を示す図である。

【図8】本発明の第2実施形態に係る符号データ選択の論理を示す図である。

【図9】本発明の第2実施形態に係る指数データ選択の論理を示す図である。

【図10】本発明の第2実施形態に係る仮数データ選択の論理を示す図である。

【図11】本発明の第2実施形態に係る指数大小比較信号生成の論理を示す図である。

【図12】本発明の第2実施形態に係る基準指数選択の論理を示す図である。

【図13】本発明の第2実施形態に係る仮数選択回路の構成を示すブロック図である。

【図14】本発明の第2実施形態に係る被加算仮数データ選択の論理を示す図である。

【図15】本発明の第2実施形態に係る加算仮数と反転データ選択の論理を示す図である。

【図16】本発明の第2実施形態に係る加算仮数データ選択の論理を示す図である。

【図17】本発明の第2実施形態に係る中間符号生成の論理を示す図である。

【図18】本発明の第2実施形態に係る符号生成の論理を示す図である。

【図19】本発明の第2実施形態に係る拡張精度データ幅演算回路における拡張精度加算時の各レジスタのデータ値例を示す図である。

【図20】本発明の第2実施形態に係る拡張精度データ幅演算回路における拡張精度加算時の各信号線のデータ値例を示す図である。

【図21】本発明の第2実施形態に係る拡張精度データ幅演算回路における倍精度加算時の各レジスタのデータ値例を示す図である。

【図22】本発明の第2実施形態に係る拡張精度データ幅演算回路における倍精度加算時の各信号線のデータ値例を示す図である。

【発明を実施するための形態】

【0015】

以下に、図面を参照して、本発明の実施の形態について例示的に詳しく説明する。ただし、以下の実施の形態に記載されている構成要素はあくまで例示であり、本発明の技術範囲をそれらのみに限定する趣旨のものではない。

【0016】

[第1実施形態]

本発明の第1実施形態としての浮動小数点演算回路100について、図1を用いて説明する。図1において、浮動小数点演算回路100は、第1演算回路101と、第2演算回路102と、休止判定部103と、演算制御部104とを含む。第1演算回路101は、第1ビット幅の数値と第1ビット幅より短い第2ビット幅の数値とのいずれかを選択可能に演算する回路である。第2演算回路102は、第2ビット幅を演算する回路である。休止判定部103は、演算命令を解析して、演算命令が第1演算回路101による第1ビット幅の数値の演算を休止することを判定する。演算制御部104は、休止判定部103からの判定が第1ビット幅の数値の演算を休止することを示す場合に、第2ビット幅の数値を第1演算回路101に入力すると共に、第1演算回路101を第2ビット幅の数値の演算を行なうようする。

【0017】

本実施形態によれば、第1演算回路101による第1ビット幅の数値の演算が休止している時には、第1ビット幅より短い第2ビット幅の数値の演算を第1演算回路101と第2演算回路102で並列して実行できる。したがって、演算処理を高速化して演算実行時間が短縮される。

【0018】

[第2実施形態]

第2実施形態は、本実施形態の浮動小数点演算回路の回路構成と、この浮動小数点演算回路を使用した科学演算回路及びコンピュータの構成を示す。本実施形態では、たとえば、スーパーコンピュータのベクトル演算において、演算処理を高速化して演算実行時間を短縮することで、業務の効率化とコンピュータシステムの消費電力が抑制できる。

【0019】

〈第2実施形態の浮動小数点演算回路を使用したコンピュータの構成〉

図2Aは、第2実施形態の浮動小数点演算回路41、第2実施形態の浮動小数点演算回路41を使用した科学演算回路40、第2実施形態の浮動小数点演算回路41を使用したコンピュータ200のそれぞれの構成を示すブロック図である。

【0020】

(コンピュータの概略構成)

図2Aにおいて、コンピュータ200は、科学演算回路40と、主記憶装置43と、入出力制御装置44と、外部記憶装置45とを含む。主記憶装置43は、科学演算プログラムと図6に標準指数データ方式で示した単精度601/倍精度602/拡張精度603の3種の科学演算データ及び科学演算命令を記憶する。主記憶装置43は、演算結果の一時記憶としても使用される。科学演算回路40は、主記憶装置43より科学演算プログラムを読み出し、命令を解析し、命令を実行し、前記実行結果を主記憶装置43へ出力する。入出力制御装置44は、科学演算回路40が解析した命令により外部記憶装置45への科学演算結果の入出力を制御する。外部記憶装置45は、入出力制御装置44から送られてくるデータを命令にしたがって保存し、入出力制御装置44へ記憶しているデータを送る。ここで、信号線L110は科学演算回路40と主記憶装置43との間の入出力信号のための信号線である。また、信号線L111は科学演算回路40と入出力制御装置44との間の入出力信号、L112は入出力制御装置44と外部記憶装置45との間の入出力信号である。

【0021】

(科学演算回路の構成)

図2Aにおいて、科学演算回路40は、浮動小数点演算回路41と命令発行制御回路42とを含む。命令発行制御回路42は、主記憶装置43から読み込んだ科学演算データ及び科学演算命令を解析する。そして、浮動小数点演算回路41に、演算精度と演算種類とを示す演算命令と、被演算データ、演算データを発行し、浮動小数点演算回路41による演算結果を受け取って主記憶装置43又は外部記憶装置45に記憶する。たとえば、演算がベクトル演算のように同じ演算を繰り返す場合は、科学演算回路40で繰り返される。ここで、信号線L100〜L106は命令発行制御回路42から浮動小数点演算回路41への入力信号用の信号線、信号線L400とL401は浮動小数点演算回路41から命令発行制御回路42への出力信号用の信号線である。信号線L100は、演算命令である。信号線L101〜L106のうち、信号線L101〜L103は、単・倍精度又は拡張精度の演算をシーケンスに実行する場合に入力される数値の符号、指数及び仮数である。信号線L104〜L106は、単・倍精度の演算を並列して(パラレルに)実行する場合に、信号線L101〜L103と並列に入力される単・倍精度の数値の符号、指数及び仮数である。L400には単精度・倍精度データ幅演算回路からの演算結果が出力され、信号線L401には拡張精度データ幅演算回路からの演算結果が出力される。本実施形態では、信号線L100の演算命令が拡張精度データ幅演算回路を休止する命令であった場合には、信号線L400とL401の両方から2つの単・倍精度の演算結果が並列に出力される。

【0022】

(命令発行制御回路の動作手順)

図2Bは、命令発行制御回路42の動作手順を示すフローチャートである。なお、かかる命令発行制御回路42の動作は、ハードウェア、ソフトウェア、ファームウエア、マイクロプログラムなど、どのように構成されてもよい。したがって、図2Bのフローチャートは、プログラムの流れを示すのみではなく、ハードウェアの処理をも含むものである。また、実際には命令発行制御回路42から信号線L101〜L106に被演算データと演算データとが順次出力されてそれぞれのレジスタに保持されるが、ここでは煩雑であるのでその詳細な説明は省いている。また、本例では信号線L100上の演算命令のデータ幅が2ビットとして、拡張精度演算休止の命令と単・倍精度の演算命令とを別個に発行している。しかし、信号線L100のデータ幅が3ビット以上であれば、拡張精度演算休止の命令と単・倍精度の演算命令とを組み合わせて信号線L100に同時に出力できる。

【0023】

まず、ステップS201において、主記憶装置43から演算プログラムを読み出す。次に、ステップS203において、演算プログラムの命令を解析する。ステップS205において、解析の結果が単・倍精度演算か/拡張精度演算かの演算判定を行なう。

【0024】

判定結果が単・倍精度演算である場合は、拡張精度演算回路は休止すると判断してステップS207に進む。ステップS207において、信号線L100に拡張精度演算休止を示す命令を提供する。ステップS209においては信号線L100に単・倍精度演算命令を発行して、信号線L104〜L106に信号線L101〜L103と並列に単・倍精度データを提供する。ステップS211においては、信号線L400とL401とから2つの単・倍精度演算結果を取得する。ステップS213においては繰り返し演算か否かを判定し、繰り返しならばステップS209に戻ってステップS209からS213を繰り返す。繰り返しで無ければステップS221に進む。

【0025】

一方、ステップS205の判定で判定結果が拡張精度演算であれば、ステップS215においては信号線L100に拡張精度演算命令を発行して、信号線L101〜L103に拡張精度データを出力する。ステップS217においては、信号線L401から1つの拡張精度演算結果を取得する。ステップS219においては繰り返し演算か否かを判定し、繰り返しならばステップS215に戻ってステップS215からS219を繰り返す。繰り返しで無ければステップS221に進む。

【0026】

ステップS221において演算結果を主記憶装置43に記憶する。あるいは入出力制御装置44を介して外部記憶装置45に記憶してもよい。ステップS223においては演算プログラムの終了か否かを判定し、終了でなければステップS203に戻って次の命令を処理する。演算プログラムの終了であれば処理を終了する。そして、次の演算プログラムの主記憶装置43からの読出しに始まる一連の流れが続く。

【0027】

なお、図2Bの手順は一例であって、これに限定されない。

【0028】

(浮動小数点演算回路の構成)

図2Aにおいて、浮動小数点演算回路41は、浮動小数点加減算回路46と、浮動小数点乗算回路47と、浮動小数点除算回路48と、浮動小数点演算結果選択回路49とを含む。浮動小数点加減算回路46は、命令発行制御回路42が浮動小数点演算回路41に出力する命令のうち加減算命令を実行する。浮動小数点乗算回路47は、命令発行制御回路42が浮動小数点演算回路41に出力する命令のうち乗算命令を実行する。浮動小数点除算回路48は、命令発行制御回路42が浮動小数点演算回路41に出力する命令のうち除算命令を実行する。浮動小数点演算結果選択回路49は、各演算回路からの演算結果を選択して命令発行制御回路42に出力する。ここで、信号線L300〜L305とL310は、それぞれの回路を接続する信号線を表している。信号線L300,L302,L304は単・倍精度の演算回路の演算結果を出力する信号線であり、信号線L301,L303,L305は拡張精度の演算回路の演算結果を出力する信号である。信号線L310は、信号線L100の演算命令を解析して得られた拡張精度の演算回路が休止するか否かを出力する信号線である。本例では、拡張精度の演算回路が休止する場合に信号線L310に"1(ハイ)"が出力され、拡張精度の演算回路が演算する場合に信号線L310に"0(ロー)"が出力される。浮動小数点演算結果選択回路49により演算結果が選択されて信号線L400とL401に出力される。浮動小数点演算結果選択回路49においては、拡張精度の演算回路が休止して信号線L310が"1"である場合、信号線L400には信号線L300,L302,L304からの単・倍精度の演算結果が出力される。同時に、信号線L401には信号線L301,L303,L305からの単・倍精度の演算結果が並列に出力される。一方、拡張精度の演算回路が演算を実行する信号線L310が"0"である場合、信号線L401に信号線L301,L303,L305からの拡張精度の演算結果が出力される。

【0029】

(浮動小数点加減算回路の構成)

図3は、第2実施形態に係る浮動小数点演算回路41に含まれる浮動小数点加減算回路46の構成を示すブロック図である。なお、本実施形態では、以下浮動小数点加減算回路46の構成と動作を代表して説明する。しかし、浮動小数点乗算回路47及び浮動小数点除算回路48においても、単精度・倍精度データ幅用と拡張精度データ幅用との2つの演算回路を備えている。そして、拡張精度データ幅用の演算回路が拡張精度演算の休止中に単精度・倍精度データ幅の演算を並列に行なうことは同様であり、演算の種類が異なるのみで構成の特徴は変わらない。従って、本明細書では、浮動小数点加減算回路46などをも浮動小数点演算回路と総称している。

【0030】

図3の浮動小数点加減算回路46は、単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12とを有する。図2Aに示したように、浮動小数点加減算回路46には、単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12とがそれぞれの加減算を行なう場合は、信号線L100に"00"や"11"でないそれぞれの演算命令が入力される。本例では、演算命令の"00"や"11"は、拡張精度データ幅演算回路12の休止を示す命令である。その場合には、信号線L101〜L103を使って、それぞれの被演算データと演算データとが入力される。単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12との演算結果は、それぞれ信号線L300又はL301から出力される。信号線L310からは信号線L100に"00"や"11"が入力されなかったことを示す"0(ロー)"が出力される。

【0031】

一方、拡張精度データ幅演算回路12が拡張精度演算を休止する場合は、信号線L100に"00"又は"11"(拡張精度データ幅演算回路12の休止を示す命令)が入力される。その場合には、信号線L101〜L103を使って、単精度・倍精度データ幅演算回路11に単精度・倍精度の被演算データと演算データとが入力される。同時に、信号線L104〜L106を使って、拡張精度データ幅演算回路12に単精度・倍精度の被演算データと演算データとが入力される。単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12との単精度・倍精度データの演算結果は、信号線L300及びL301から並列に出力される。信号線L310からは信号線L100に"00"又は"11"が入力されたことを示す"1(ハイ)"が出力される。この信号線L310の"1(ハイ)"は、図2Aの浮動小数点演算結果選択回路49に対して、信号線L400とL401に単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12とが並列に演算した演算結果を出力させる。

【0032】

(拡張精度データ幅演算回路の構成)

図4は、第2実施形態に係る浮動小数点加減算回路46に含まれる拡張精度データ幅演算回路12の構成を示すブロック図である。拡張精度データ幅演算回路12は、図6の603に示すフォーマットの拡張精度演算データの演算を行なうが、図6の601や602に示すフォーマットの単精度・倍精度演算データの演算を行なうことも可能である。従って、図4の拡張精度データ幅演算回路12の各レジスタや各回路は、拡張精度演算データの演算と単精度・倍精度演算データの演算とを実行可能に構成されており、その詳細は省略する。なお、以下の説明では、各回路の機能及び動作順を考慮している。また、拡張精度データ幅演算回路12の減算における動作は加算と符号を変えれば実質的に同様であるので、以下の説明は加算を中心に説明する。すなわち、以下で使用する文言「加算」は、特に図7〜図17において「加減算」を意味する。従って、本明細書では、特徴的な構成を有する拡張精度データ幅演算回路12をも浮動小数点演算回路と総称している。

【0033】

(A:入力データ用レジスタと出力データ用レジスタ)

拡張精度データ幅演算回路12は、命令発行制御回路42から信号線L100〜L106によって入力された信号を保持するレジスタ群を有する。レジスタ1は、信号線L100からの演算命令を保持する演算命令レジスタである。レジスタ2〜13は、信号線L101〜L106からの被演算データ及び演算データを保持するレジスタである。このうち、信号線L101〜L103に接続されたレジスタ2,4,6,8,10,12は、拡張精度データ幅演算回路12が拡張精度幅の加算を行なう場合に、拡張幅データを保持する第1レジスタ群である。第1レジスタ群は、さらに、被加算データの符号、指数、仮数を保持するレジスタ2,6,10と、加算データの符号、指数、仮数を保持するレジスタ4,8,12からなる。一方、信号線L104〜L106に接続されたレジスタ3,5,7,9,11,13は、拡張精度データ幅演算回路12が単精度・倍精度幅の加算を行なう場合に、単精度・倍精度幅データを保持する第2レジスタ群である。第2レジスタ群は、さらに、被加算データの符号、指数、仮数を保持するレジスタ3,7,11と、加算データの符号、指数、仮数を保持するレジスタ5,9,13からなる。

【0034】

一方、拡張精度データ幅演算回路12は、浮動小数点演算結果選択回路49に対して信号線L301,L310から出力する信号を保持するレジスタ14と15とを有する。レジスタ14は、演算結果の符号、指数、仮数を保持する演算結果格納レジスタである。レジスタ15は、信号線L100から入力されてレジスタ1に保持された演算命令から、演算実行中フラグ生成回路16によって生成された演算実行中フラグを保持する演算実行中フラグ格納レジスタである。この演算実行中フラグ生成回路16における、信号線L200のレジスタ1からの演算命令を入力とし、信号線L257の演算実行フラグを出力とする論理を含む、演算命令に基づく論理700を図7に示す。図7の演算命令701に基づいて演算実行フラグ702が生成される。図7に示すように、演算命令が"00"又は"11"の場合は演算実行フラグに"1"が出力されて、拡張精度データ幅演算回路12における拡張精度の演算休止が示される。したがって、レジスタ15は演算実行フラグ格納レジスタとして機能する。

【0035】

(B:単・倍精度/拡張精度の入力選択回路)

演算実行中フラグ生成回路16から出力する信号線L257の演算実行中フラグは、演算符号選択回路17、演算指数選択回路18及び演算仮数選択回路19に入力される。演算符号選択回路17、演算指数選択回路18及び演算仮数選択回路19は、信号線L257の演算実行中フラグに従って入力された符号、指数、仮数を選択して演算回路群に伝達する。

【0036】

演算符号選択回路17には、レジスタ2〜5からそれぞれ信号線L240〜L243に出力された被加算データ符号と加算データ符号とが入力される。演算符号選択回路17は、信号線L257の演算実行中フラグによる図8に示す論理800に従って、入力された符号を選択して信号線L253とL254とに出力する。演算実行中フラグが"0"の場合は、801で示すように、レジスタ2及び4からそれぞれ信号線L240及びL241に出力された拡張精度の被加算データ符号と加算データ符号とを選択して、信号線L253とL254に出力する。一方、演算実行中フラグが"1"の場合は、802で示すように、レジスタ3及び5からそれぞれ信号線L242及びL243に出力された単精度・倍精度の被加算データ符号と加算データ符号とを選択して、信号線L253とL254に出力する。

【0037】

演算指数選択回路18には、レジスタ6〜9からそれぞれ信号線L244〜L247に出力された被加算指数データと加算指数データとが入力される。演算指数選択回路18は、信号線L257の演算実行中フラグによる図9に示す論理900に従って、入力された指数データを選択して信号線L255とL256とに出力する。演算実行中フラグが"0"の場合は、901で示すように、レジスタ6及び8からそれぞれ信号線L244及びL245に出力された拡張精度の被加算指数データと加算指数データとを選択して、信号線L255とL256に出力する。一方、演算実行中フラグが"1"の場合は、902で示すように、レジスタ7及び9からそれぞれ信号線L246及びL247に出力された単精度・倍精度の被加算指数データと加算指数データとを選択して、信号線L255とL256に出力する。

【0038】

演算仮数選択回路19には、レジスタ10〜13からそれぞれ信号線L248〜L251に出力された被加算仮数データと加算仮数データとが入力される。演算仮数選択回路19は、信号線L257の演算実行中フラグによる図10に示す論理1000に従って、入力された仮数データを選択して信号線L258とL259とに出力する。演算実行中フラグが"0"の場合は、1001で示すように、レジスタ10及び12からそれぞれ信号線L248及びL249に出力された拡張精度の被加算仮数データと加算仮数データとを選択して、信号線L258とL259に出力する。一方、演算実行中フラグが"1"の場合は、1002で示すように、レジスタ11及び13からそれぞれ信号線L250及びL251に出力された単精度・倍精度の被加算仮数データと加算仮数データとを選択して、信号線L258とL259に出力する。

【0039】

(C:演算命令解析回路)

レジスタ1に保持された演算命令は、信号線L200により演算命令解析回路20に入力される。演算命令解析回路20は、図7の論理700に従って、信号線L200の演算命令と信号線L253の被加算データ符号と信号線L254の加算データ符号とに基づいて、演算命令解析結果を信号線L207から出力する。図7に示すように、演算命令解析結果の"0"は加算、"1"は減算であり、仮数選択回路25の制御に使用される。

【0040】

(D:指数選択回路と指数調整回路)

指数大小比較回路21は、演算指数選択回路18から信号線L255とL256に出力された被加算指数データと加算指数データとの大小を比較する。図11は、指数大小比較回路21における指数データと信号線L211に出力される値との論理1100を示す図である。信号線L255に出力された被加算指数データが信号線L256に出力された加算指数データよりも大きければ、信号線L211に"1"が出力される。信号線L255に出力された被加算指数データが信号線L256に出力された加算指数データよりも大きく無ければ、信号線L211に"0"が出力される。信号線L211の値は、基準指数選択回路22の選択と、中間符号生成回路24の中間符号生成と、仮数選択回路25の制御に使用される。

【0041】

基準指数選択回路22は、被加算仮数データと加算仮数データとの桁合わせをどちらに合わせて行なうかを決定する。図12は、基準指数選択回路22における信号線L211に出力される値に対応して信号線L209に出力される指数データの論理1200を示す図である。指数大小比較回路21からの信号線L211の出力値が"0"の場合は、被加算指数データが基準となり被加算指数データが信号線L209に出力される。指数大小比較回路21からの信号線L211の出力値が"1"の場合は、加算指数データが基準となり加算指数データが信号線L209に出力される。

【0042】

シフト量算出回路23は、演算指数選択回路18が選択したより大きい指数と選択されなかったより小さい指数の差を求めて、小さい仮数データを右シフトして桁合わせする右シフト量を求めて、信号線L210により桁合わせ右シフト回路27に送る。

【0043】

(E:仮数演算回路)

仮数選択回路25には、演算仮数選択回路19で選択されて信号線L258とL259に出力された被加算仮数と加算仮数とが入力されて、被加算仮数と加算仮数とを信号線L212とL213のいずれに出力するかを選択する。仮数選択回路25の選択は、指数大小比較回路21から信号線L211に出力された被加算指数と加算指数との大小比較結果と、演算命令解析回路20から信号線L207に出力された演算命令解析結果とに基づいて、行なわれる。すなわち、指数の小さい方を桁合わせが必要な仮数として出力し、他方を桁合わせが必要ない仮数として出力する。

【0044】

図13は、仮数選択回路25の内部構成を示す図である。仮数選択回路25は、仮数A選択回路50と、仮数B選択回路51と、仮数B反転選択回路52とからなる。

【0045】

仮数A選択回路50は、信号線L212に出力する仮数を、信号線L211の被加算指数と加算指数との大小比較結果に基づいて被加算仮数と加算仮数とのうち指数の小さい仮数を選択する。図14は、仮数A選択回路50の論理1400を示す図である。仮数B選択回路51と仮数B反転選択回路52とは、信号線L213に出力する仮数を、信号線L211の被加算指数と加算指数との大小比較結果と、信号線L207の演算命令解析結果とに基づいて被加算仮数と加算仮数とのうち指数の大きい仮数を選択する。図15は、仮数B選択回路51の論理1500を示す図である。仮数B選択回路51から出力される信号線L280には選択された仮数がそのまま出力され、信号線L281には選択された仮数を反転したデータが出力される。仮数B反転選択回路52は、仮数B選択回路51から出力された信号線L280の仮数と信号線L281の反転仮数とを信号線L211の演算命令解析結果に基づいて選択し、信号線L213に出力する。図16は、仮数B反転選択回路52の論理1600を示す図である。演算命令解析結果が"0"(加算)の場合は信号線L280の反転しない仮数を信号線L213に出力し、演算命令解析結果が"1"(減算)の場合は信号線L280の反転した仮数を信号線L213に出力する。

【0046】

桁合わせ右シフト回路27は、信号線L212から入力された指数の小さな仮数を、シフト量算出回路23から信号線L210に出力された大小指数の差だけ右シフトして、加減算回路29で演算する仮数の桁合わせを行なう。加減算回路29は、桁合わせ右シフト回路27の桁合わせした信号線L215の仮数データと桁合わせが必要ない信号線L213の仮数データとを加算した加減算結果を、信号線L216に出力する。同時に、指数が同じ数値で、小さい被加算仮数から大きい加算仮数を減算した場合を検出して、信号線L220にその結果を出力する。指数が同じ数値で、小さい被加算仮数から大きい加算仮数を減算した場合に、"1"が出力される。

【0047】

0桁数チェック回路28は、加減算回路29が信号線L216に出力する演算結果の上位における"0"データの有無を検出して信号線L217に出力する。そして、正規化左シフト回路31は、0桁数チェック回路28が信号線L217出力した数値分を左シフトして演算結果の仮数を正規化し、演算結果の仮数として信号線L218に出力する。信号線L218の正規化された演算結果の仮数は、レジスタ14に送られて保持される。

かかる正規化左シフト回路31と0桁数チェック回路28は、演算結果の仮数と指数とを整合する整合回路として機能する。

【0048】

(F:指数生成回路)

指数生成減算回路30は、基準指数選択回路22から信号線L209に出力された大きな指数を入力する。そして、0桁数チェック回路28が信号線L217に出力した数値分だけ演算結果が正規化左シフト回路31で左シフトされるのに合わせて、信号線L209の指数から信号線L217の数値を減算して、演算結果の指数として信号線L219に出力する。信号線L219の生成符号は、レジスタ14に送られて保持される。

【0049】

(G:符号生成回路)

演算符号選択回路17から信号線L253とL254に出力された被加算データ符号と加算データ符号とは、中間符号生成回路24に入力される。中間符号生成回路24は、指数大小比較回路21からの信号線L211の値に基づいて、信号線L253とL254から入力された被加算データ符号と加算データ符号とのいずれかを選択して、信号線L208に出力する。図17は、中間符号生成回路24の論理1700を示す図である。中間符号生成回路24は、大きなデータの符号を選択して出力する。すなわち、信号線L211の値が"0"(加算指数データが被加算指数データ以上)の場合は、加算データ符号を信号線L208に出力する。一方、信号線L211の値が"1"(加算指数データが被加算指数データより小さい)の場合は、被加算データ符号を信号線L208に出力する。

【0050】

符号生成回路26は、中間符号生成回路24が出力した信号線L208の中間符号を入力する。そして、加減算回路29の指数が同じ数値で、小さい被加算仮数から大きい加算仮数を減算した場合を検出して信号線L220に出力した結果に基づいて、中間符号を調整する。図18は、符号生成回路26の論理1800を示す図である。信号線L220の符号反転信号が"1"の場合に、中間符号が反転されて生成符号となる。符号生成回路26は、生成した生成符号を演算結果の符号として信号線L214に出力する。信号線L214の生成符号は、レジスタ14に送られて保持される。

【0051】

図4の拡張精度データ幅演算回路12の構成により、拡張精度データ幅演算回路12で拡張精度演算が休止中に単・倍精度演算が実行可能となる。すなわち、信号線L100から入力された演算命令が拡張精度演算であれば、信号線L101〜L103から入力された拡張精度データ幅の数値データが演算される。そして、レジスタ14に拡張精度の演算結果が保持され、レジスタ15に拡張精度演算を示す"0"が保持されて、信号線L301とL310から出力される。一方、信号線L100から入力された演算命令が拡張精度演算でなければ、信号線L104〜L106から入力された他・倍精度データ幅の数値データが演算される。そして、レジスタ14に単・倍精度の演算結果が保持され、レジスタ15に単・倍精度演算を示す"1"が保持されて、信号線L301とL310から出力される。

【0052】

(単精度・倍精度データ幅演算回路11の構成)

図5は、第2実施形態に係る浮動小数点加減算回路46に含まれる単精度・倍精度データ幅演算回路11の構成を示すブロック図である。図5の単精度・倍精度データ幅演算回路11は、図4の拡張精度データ幅演算回路12の構成とは以下の点が異なっている以外は、データ幅の違いはあるが同じ名称の構成要素の機能は同様であるので、詳細な説明は省く。各レジスタ、指数演算に係る回路及び仮数演算に係る回路のデータ幅が、図6に示す単精度・倍精度演算データのフォーマットに適応されるのみである。

【0053】

図5のレジスタ70は図4のレジスタ1に相当する。図5のレジスタ71〜76は、図4のレジスタ2,4,6,8,10,12に相当する。図5の演算命令解析回路77は、図4の演算命令解析回路20に相当する。図5の指数大小比較回路81は、図4の指数大小比較回路21に相当する。図5の基準指数選択回路79は、図4の基準指数選択回路22に相当する。図5のシフト量算出回路80は、図4のシフト量算出回路23に相当する。図5の仮数選択回路82は、図4の仮数選択回路25に相当する。図5の桁合わせ右シフト回路84は、図4の桁合わせ右シフト回路27に相当する。図5の加減算回路86は、図4の加減算回路29に相当する。図5の0桁数チェック回路85は、図4の0桁数チェック回路28に相当する。図5の正規化左シフト回路88は、図4の正規化左シフト回路31に相当する。図5の指数生成減算回路87は、図4の指数生成減算回路30に相当する。図5の中間符号生成回路78は、図4の中間符号生成回路24に相当する。図5の符号生成回路83は、図4の符号生成回路26に相当する。図5のレジスタ89は図4のレジスタ14に相当する。

【0054】

単精度・倍精度データ幅演算回路11は、拡張精度データ幅演算回路12の信号線L104〜L106の入力データを保持するレジスタ群、入力データを選択する演算符号選択回路17、演算指数選択回路18及び演算仮数選択回路19を有していない。また、選択信号である演算実行中フラグを生成する演算実行中フラグ生成回路16とそれを保持するレジスタ15を有していない。

【0055】

図4の拡張精度データ幅演算回路12と図5の単精度・倍精度データ幅演算回路11とを含む構成により、図3の浮動小数点加減算回路46は以下のように動作する。拡張精度演算であれば、拡張精度データ幅演算回路12の信号線L301から拡張精度の演算結果が出力される。一方、単・倍精度演算であれば、単・倍精度データ幅演算回路11の信号線L300から1つの単・倍精度演算結果が出力される。さらに並列に、拡張精度データ幅演算回路12の信号線L301からもう1つの単・倍精度の演算結果が出力される。拡張精度演算か単・倍精度演算かは信号線L310の信号により示される。

【0056】

図3の浮動小数点加減算回路46を含む構成により、図2Aの科学演算回路40は以下のように動作する。拡張精度演算か単・倍精度演算かは信号線L310の信号により示される。拡張精度演算であれば、拡張精度データ幅演算回路12の信号線L301から出力された拡張精度の演算結果が浮動小数点演算結果選択回路49で選択されて、信号線L401により命令発行制御回路42に戻される。一方、単・倍精度演算であれば、単・倍精度データ幅演算回路11の信号線L300から出力された1つの単・倍精度演算結果が信号線L400により命令発行制御回路42に戻される。さらに並列に、拡張精度データ幅演算回路12の信号線L301から出力されたもう1つの単・倍精度の演算結果が信号線L401により命令発行制御回路42に戻される。

【0057】

〈第2実施形態の拡張精度データ幅演算回路を有する浮動小数点演算回路の動作手順〉

以下、第2実施形態の浮動小数点演算回路の具体的動作として、浮動小数点加減算回路46の処理例を説明する。本実施形態では、拡張精度データ幅演算回路12が休止中であることを条件に、命令発行制御回路42から拡張精度データ幅演算回路12に単精度・倍精度演算命令と単精度・倍精度の32ビット幅又は64ビット幅のデータとを転送する。これにより、拡張精度データ幅演算回路12において単精度・倍精度の演算結果を得ることができる。なお、単精度・倍精度データ幅演算回路11の動作と拡張精度データ幅演算回路12の単精度・倍精度演算は類似であるので、拡張精度データ幅演算回路12の拡張精度演算と単精度・倍精度演算について説明する。

【0058】

(拡張精度データ幅演算回路12の拡張精度演算時における動作手順)

以下、拡張精度データ幅の演算、"1000000000000000000000000000×162"(被加算データ)+"7FFFFFFFFFFFFFFFFFFFFFFFFFFF×164"(加算データ)、を1回加算する動作を説明する。なお、取り扱う浮動小数点演算データは、所謂、標準指数データ形式と拡張指数データ形式とIEEE指数データ形式との内、図6に示す標準指数データ形式(符号データ1ビット、指数データ7ビットを2桁の16進数表記、仮数データ112ビットを28桁の16進数表記)を用いて説明する。

【0059】

図19と図20は、かかる動作の説明における各レジスタ値1900と各信号線の数値2000とを示す図である。

【0060】

命令発行制御回路42からの信号線L100の加算命令として、レジスタ1に加算命令の数値"01"が格納される。また、前述の拡張精度データ幅の被加算データと加算データとより、レジスタ2に被加算データの符号数値"0"(正符号)が、レジスタ4に加算データの符号数値"0"(正符号)が格納される。また、レジスタ6に被加算データの指数値"02"が、レジスタ8に加算データの指数値"04"が格納される。また、レジスタ10に被加算仮数データ値"1000000000000000000000000000"が、レジスタ12に加算仮数データ値"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"がそれぞれ格納される。

【0061】

演算実行中フラグ生成回路16は、図7の演算命令生成論理700からレジスタ1からの信号線L200の信号が"01"の拡張精度データ幅の加算命令であることから、演算テータ選択信号として"0"を信号線L257に出力する。信号線L257の"0"を条件として、演算符号選択回路17は、図8の符号データ選択論理800から信号線L240とL242の拡張精度データ幅の被加算符号データを選択して、信号線L253とL254に共に"0"(正符号)を出力する。演算指数選択回路18は、図9の指数データ選択論理900から信号線L244とL245の拡張精度データ幅の指数データを選択して、信号線L255に"02"、信号線L256"04"を出力する。演算仮数選択回路19は、図10の仮数データ選択論理1000から信号線L248とL249の拡張精度データ幅の仮数データを選択する。そして、それぞれ信号線L258に"1000000000000000000000000000"、信号線L259に"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"を出力する。

【0062】

演算命令解析回路20は、信号線L200の演算命令の数値"01"(加算命令)と、信号線L253の数値"0"(正符号)と、信号線L254の数値"0"(正符号)との条件から、図7の演算命令生成論理700から加算命令となることを解析し、信号線L207に数値"0"(加算命令)を出力する。

【0063】

指数大小比較回路21は、信号線L255の被加算指数データの数値"02"と信号線L256の加算指数データの数値"04"とを大小比較する。比較結果として、図11の指数大小比較論理1100から信号線L256の指数データを大きいと判定して、指数大小比較結果信号として信号線L211に数値"0"を出力する。基準指数選択回路22は、信号線L211の指数大小比較結果の数値"0"の条件から、図12の基準指数選択論理1200から大きい加算指数データである信号線L256の数値"04"を選択して、信号線L209に出力する。シフト量算出回路23は、信号線L255の被加算データの指数の数値"02"と、信号線L256の加算データの指数の数値"04"との差を求め、桁合わせのための右シフト量として信号線L210に数値"2"を出力する。

【0064】

仮数選択回路25は、信号線L211の指数大小比較結果信号が"0"で加算データの指数が大きいので、図10の被加算仮数データ選択結果論理1400から被加算データの仮数と加算データの仮数との入れ替えは必要ないと判断する。従って、信号線L258の被加算仮数データを選択し、信号線L212に被加算仮数データ"1000000000000000000000000000"を出力する。一方、図15の加算仮数データと加算反転仮数データの選択論理1500から、信号線L259の加算仮数データの数値、"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L280に出力する。また、信号線L259の補数、"1000000000000000000000000000"を信号線L281に出力する。そして、信号線L207の演算命令解析結果信号の"0(加算)"を条件に、図16の加算仮数データ選択論理1600から、信号線L280の加算仮数データ、"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L213の仮数選択信号として選択して出力する。桁合わせ右シフト回路27は、信号線L210の右シフト量信号の数値"2"に基づいて2桁右シフトをすることから、被加算データの仮数の数値として"0010000000000000000000000000"を信号線L215に出力する。加減算回路29は、信号線L215の数値"0010000000000000000000000000"と、信号線L213の数値"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"とを加算する。そして、加算結果の数値、"800FFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L216に出力する。

【0065】

0桁数チェック回路28は、信号線L216の加算結果信号の数値"800FFFFFFFFFFFFFFFFFFFFFFFFF"の"8"を先頭に上の桁に数値"0"の有無をチェックする。信号線L216の数値の先頭が"8"で先頭データに"1"の数値が存在することを確認すると、信号線L217に0桁数チェック信号の数値"0"を出力する。信号線L217の"0"は、正規化のための左シフトが不要であることから正規化左シフト回路31は正規化のための左シフトは行わず、結果として数値"800FFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L218に出力する。

【0066】

指数生成減算回路30は、信号線L209の基準指数選択結果の数値"04"から信号線L217の0桁数チェック信号の数値"0"を減算して、信号線L219に指数データの数値"04"を出力する。

【0067】

中間符号生成回路24は、信号線L211の指数大小比較結果信号の数値"0"と、信号線L253の被加算符号テータ及び信号線L254の加算符号データの"0"の条件から、図17の中間符号生成論理1700から、信号線L254の大きい指数の符号の数値"0"(正符号)を信号線L208に出力する。そして、符号生成回路26は、演算を実行する被加算仮数と加算仮数の数値から小さい被加算仮数データから大きい加算仮数データを減算することはないので、信号線L220に"0"を出力する。信号線L220の"0"の条件に基づき、図18の符号生成論理1700から符号を反転することなく信号線L214に数値"0"(正符号)を出力する。

【0068】

レジスタ14は、符号生成回路26で生成した信号線L214の符号値"0"(正符号)を格納する。また、指数生成減算回路30で求めた信号線L219の指数データ"04"と、正規化左シフト回路31が信号線L218に出力した仮数データ"800FFFFFFFFFFFFFFFFFFFFFFFFF"とを格納する。そして、演算結果として信号線L301により出力する。また、レジスタ15は、演算実行中フラグ生成回路16の信号線L257への出力"0"を格納し、信号L310により出力する。

【0069】

以上で、"1000000000000000000000000000×162"+"7FFFFFFFFFFFFFFFFFFFFFFFFFFF×164"の加算が完了し、この結果を、図2Aの浮動小数点加減算回路46から浮動小数点加減算結果を信号線L301により出力する。浮動小数点演算結果選択回路49は、信号線L301の拡張精度の加算結果を信号線L401により命令発行制御回路42に出力して、拡張精度の1回の演算が完了する。

【0070】

この加算の解は、"800FFFFFFFFFFFFFFFFFFFFFFFFF×164"である。このように、信号線L219の指数の数値が"04"であり、信号線L218に仮数の数値が"800FFFFFFFFFFFFFFFFFFFFFFFFF"であることから一致する。

【0071】

同様に、図2に示す浮動小数点演算回路41の浮動小数点乗算回路47は信号線L303に拡張精度の演算結果を、浮動小数点除算回路48は信号線L305に拡張精度の演算結果を出力する。これらの拡張精度の演算結果は、浮動小数点演算結果選択回路49から命令発行制御回路42に戻されて、加減算と乗算と除算の拡張精度の1回の演算は完了する。

【0072】

(拡張精度データ幅演算回路12の単・倍精度演算時における動作手順)

以下、倍精度データ幅の演算、"10000000000000xxxxxxxxxxxxxx×162"(被加算データ)"(被加算データ)+"7FFFFFFFFFFFFFxxxxxxxxxxxxxx×164"(加算データ)、を1回加算する動作を説明する。なお、取り扱う浮動小数点演算データは、所謂、標準指数データ形式と拡張指数データ形式とIEEE指数データ形式との内、図6に示した標準データ形式(符号データ1ビット、指数データ7ビットを2桁の16進数表記、仮数データ56ビットを14桁の16進数表記)を用いて説明する。なお、単精度の演算も同様であり、説明は省略する。

【0073】

図21と図22は、かかる動作の説明における各レジスタ値2100と各信号線の数値2200とを示す図である。

【0074】

まず、命令発行制御回路42からの信号線L100の演算命令として、レジスタ1に数値"00"または"11"が格納される。レジスタ1からの信号線L200は演算実行中フラグ生成回路16に入力され、図7の論理700に従って信号線L257には演算実行中フラグが"1"で出力される。この演算実行中フラグの"1"で信号線L104〜L106から入力される倍精度データが演算符号、演算指数、演算仮数として選択される。また、演算実行中フラグの"1"は、レジスタ15に格納されて信号線L310から出力され、図2Aに図示の浮動小数点演算結果選択回路49における演算結果の選択に使用される。

【0075】

次に、命令発行制御回路42からの信号線L100の加算命令として、レジスタ1に加算命令の数値"01"が格納される。また、前述の倍精度データ幅の被加算データと加算データとより、レジスタ2に被加算データの符号数値"0"(正符号)が、レジスタ4に加算データの符号数値"0"(正符号)が格納される。また、レジスタ10に被加算仮数データ値"10000000000000xxxxxxxxxxxxxx"が、レジスタ12に加算仮数データ値"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"がそれぞれ格納される。

【0076】

演算命令解析回路20は、拡張精度の演算時と同様に、信号線L200の演算命令の数値"01"(加算命令)と、信号線L253の数値"0"(正符号)と、信号線L254の数値"0"(正符号)との条件から、図7の演算命令生成論理700から加算命令となることを解析し、信号線L207に数値"0"(加算命令)を出力する。

【0077】

指数の処理も拡張精度の演算時と同様である。指数大小比較回路21は、信号線L255の被加算指数データの数値"02"と信号線L256の加算指数データの数値"04"とを大小比較する。比較結果として、図11の指数大小比較論理1100から信号線L256の指数データを大きいと判定して、指数大小比較結果信号として信号線L211に数値"0"を出力する。基準指数選択回路22は、信号線L211の指数大小比較結果の数値"0"の条件から、図12の基準指数選択論理1200から大きい加算指数データである信号線L256の数値"04"を選択して、信号線L209に出力する。シフト量算出回路23は、信号線L255の被加算データの指数の数値"02"と、信号線L256の加算データの指数の数値"04"との差を求め、桁合わせのための右シフト量として信号線L210に数値"2"を出力する。

【0078】

仮数選択回路25は、信号線L211の指数大小比較結果信号が"0"で加算データの指数が大きいので、図10の被加算仮数データ選択結果論理1400から被加算データの仮数と加算データの仮数との入れ替えは必要ないと判断する。 従って、信号線L258の被加算仮数データを選択し、信号線L212に被加算仮数データ"10000000000000xxxxxxxxxxxxxx"を出力する。

【0079】

一方、図15の加算仮数データと加算反転仮数データの選択論理1500から、信号線 L259の加算仮数データの数値、"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L280に出力する。また、信号線L259の補数、"10000000000000xxxxxxxxxxxxxx"を信号線L281に出力する。そして、信号線L207の演算命令解析結果信号の"0(加算)"を条件に、図16の加算仮数データ選択論理1600から、信号線L280の加算仮数データ、"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L213の仮数選択信号として選択して出力する。桁合わせ右シフト回路27は、信号線L210の右シフト量信号の数値"2"に基づいて2桁右シフトをすることから、被加算データの仮数の数値として"00100000000000xxxxxxxxxxxxxx"を信号線 L215に出力する。加減算回路29は、信号線L215の数値"00100000000000xxxxxxxxxxxxxx"と、信号線L213の数値"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"とを加算する。そして、加算結果の数値、"800FFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L216に出力する。

【0080】

0桁数チェック回路28のチェックは、拡張精度の場合と倍精度の場合で異なっている。0桁数チェック回路28は、信号線L216の加算結果信号の数値"800FFFFFFFFFFFxxxxxxxxxxxxxx"の"8"を先頭に上の桁に数値"0"の有無をチェックする。信号線L216の数値の先頭が"8"で先頭データに"1"の数値が存在することを確認すると、信号線L217に0桁数チェック信号の数値"0"を出力する。信号線L217の"0"は、正規化のための左シフトが不要であることから正規化左シフト回路31は正規化のための左シフトは行わず、結果として数値"800FFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L218に出力する。

【0081】

指数生成減算回路30は、信号線L209の基準指数選択結果の数値"04"から信号線L217の0桁数チェック信号の数値"0"を減算して、信号線L219に指数データの数値"04"を出力する。

【0082】

中間符号生成回路24は、信号線L211の指数大小比較結果信号の数値"0"と、信号線L253の被加算符号テータ及び信号線L254の加算符号データの"0"の条件から、図17の中間符号生成論理1700から、信号線L254の大きい指数の符号の数値"0"(正符号)を信号線L208に出力する。そして、符号生成回路26は、演算を実行する被加算仮数と加算仮数の数値から小さい被加算仮数データから大きい加算仮数データを減算することはないので、信号線L220に"0"を出力する。信号線L220の"0"の条件に基づき、図18の符号生成論理1700から符号を反転することなく信号線L214に数値"0"(正符号)を出力する。

【0083】

レジスタ14は、符号生成回路26で生成した信号線L214の符号値"0"(正符号)を格納する。また、指数生成減算回路30で求めた信号線L219の指数データ"04"と、正規化左シフト回路31が信号線L218に出力した仮数データ"800FFFFFFFFFFFxxxxxxxxxxxxxx"とを格納する。そして、演算結果として信号線L301により出力する。また、レジスタ15は、演算実行中フラグ生成回路16の信号線L257への出力"0"を格納し、信号L310により出力する。

【0084】

以上で、倍精度の"00100000000000xxxxxxxxxxxxxx×162"+"7FFFFFFFFFFFFFxxxxxxxxxxxxxx×164"の加算が完了し、この結果を、図2Aの浮動小数点加減算回路46から浮動小数点加減算結果を信号線L301により出力する。

【0085】

同様に、図2に示す浮動小数点演算回路41の浮動小数点乗算回路47は信号線L302とL303に並列に2つの倍精度の演算結果を、浮動小数点除算回路48は信号線L304とL305に並列の2つの倍精度の演算結果を出力する。これらの倍精度の2つの演算結果は、浮動小数点演算結果選択回路49から命令発行制御回路42に信号線L400とL401により並列に戻されて、加減算と乗算と除算の倍精度のそれぞれ2回の演算は完了する。

【0086】

以上、拡張精度データ幅演算回路12の拡張精度演算時または倍精度演算時における動作手順を示した。単精度・倍精度データ幅演算回路11の動作手順は、拡張精度演算の中止と演算データの選択が無い場合の拡張精度データ幅演算回路12の倍精度演算時における動作手順と類似である。

【0087】

本実施形態によれば、128ビットの拡張精度のデータ幅の演算回路で32ビットの単精度データ幅と64ビットの倍精度データ幅の演算が実行できる。従って、既存の単精度・倍精度データ幅の演算回路と同時に拡張精度の演算回路との2つの演算回路で並列に演算ができることで、演算時間が1/2に短縮できることにある。その理由は、拡張演算回路が演算実行中又は未使用であることを検出する回路を設けている。そして、拡張データ幅の演算回路が未使用である場合に単精度倍精度と拡張精度データ幅の演算データを拡張演算回路に振り向けて実行できる回路を設けていることにある。本実施形態は、特にスーパーコンピュータなどでのベクトル演算における多回数の繰り返し演算において、より顕著な効果を発揮する。

【0088】

[他の実施形態]

以上、本発明の実施形態について詳述したが、それぞれの実施形態に含まれる別々の特徴を如何様に組み合わせたシステム又は装置も、本発明の範疇に含まれる。

【0089】

また、本発明は、複数の機器から構成されるシステムに適用しても良いし、単体の装置に適用しても良い。さらに、本発明は、実施形態の機能を実現する演算制御プログラムが、システムあるいは装置に直接あるいは遠隔から供給される場合にも適用可能である。したがって、本発明の機能をコンピュータで実現するために、コンピュータにインストールされる演算制御プログラム、あるいはその演算制御プログラムを格納した記憶媒体、その演算制御プログラムをダウンロードさせるWWWサーバも、本発明の範疇に含まれる。

【0090】

[実施形態の他の表現]

上記の実施形態の一部又は全部は、以下の付記のようにも記載されうるが、以下には限られない。

(付記1)

第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、

演算命令に基づいて、前記第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定手段と、

前記休止判定手段が前記第1演算回路が休止すると判定した場合に、前記第1演算回路を前記第2ビット幅の数値の演算を行なうよう制御し、前記第2ビット幅の数値の演算を、前記第1演算回路と前記第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御手段と、

を備えることを特徴とする浮動小数点演算回路。

(付記2)

前記第1ビット幅の数値及び前記第2ビット幅の数値を前記休止判定手段の判定結果に応じて、前記第1演算回路に選択可能に入力する入力手段を有することを特徴とする付記1に記載の浮動小数点演算回路。

(付記3)

前記演算制御手段において前記第1演算回路が前記第2ビット幅の数値を演算した演算結果と前記第2演算回路が前記第2ビット幅の数値を演算した演算結果とを選択して出力する出力手段を含むことを特徴とする付記1又は2に記載の浮動小数点演算回路。

(付記4)

前記第1演算回路は、

前記第1演算回路への演算命令が、前記第1ビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合は、前記第1ビット幅の数値に対して浮動小数点演算を実行し、前記演算判定手段が前記第1ビット幅の数値に対する演算でないと判定した場合は、前記第2ビット幅の数値に対して浮動小数点演算を実行する演算実行手段と、

を有することを特徴とする付記1乃至3のいずれか1項に記載の浮動小数点演算回路。

(付記5)

前記演算判定手段は、

演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて前記第1演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記第1演算回路を休止するか否かの前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記第1ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記第2ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から得た浮動小数点演算結果を格納する演算結果格納レジスタと、を有することを特徴とする付記1乃至4のいずれか1項に記載の浮動小数点演算回路。

(付記6)

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

当該浮動小数点演算回路への演算命令が、拡張されたビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が拡張されたビット幅の数値に対する演算であると判定した場合は、前記拡張されたビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が拡張されたビット幅の数値に対する演算でないと判定した場合は、前記拡張されたビット幅より短いビット幅の数値の浮動小数点演算を実行する演算実行手段と、

を備えることを特徴とする浮動小数点演算回路。

(付記7)

前記演算判定手段は、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記拡張されたビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記拡張されたビット幅より短いビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から浮動小数点演算結果を格納する演算結果格納レジスタと、

を有することを特徴とする付記6に記載の浮動小数点演算回路。

(付記8)

前記浮動小数点演算回路が行なう演算が、加算又は減算である場合に、

前記演算実行手段は、

前記演算実行中フラグに基づいて指数のデータ幅に合った指数を選択する基準指数選択回路と、

前記演算実行中フラグに基づいて指数の差を求めて桁合わせ右シフト量を求めるシフト量算出回路と、

第1データの仮数が格納される第1レジスタと、

第2データの仮数が格納される第2レジスタと、

前記第1データの仮数及び前記第2データの仮数のうち、前記演算実行中フラグに基づいて指数の小さい方を桁合わせが必要な仮数として出力し、他方を桁合わせが必要ない仮数として出力する仮数選択回路と、

前記仮数選択回路から出力された桁合わせが必要な仮数を、前記第1データの仮数及び前記第2データの前記演算実行中フラグに基づく指数の差に応じたシフト量だけ右シフトして、シフトした結果を出力する桁合わせ右シフト回路と、

前記桁合わせ右シフト回路から出力される前記桁合わせが必要な仮数のシフトした結果と前記仮数選択回路から出力される桁合わせが必要ない仮数との加減算を行って、加減算結果を出力する加減算回路と、

前記加減算回路から出力された前記加減算結果を正規化する正規化左シフト回路と、

を備えることを特徴とする付記7に記載の浮動小数点演算回路。

(付記9)

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止するか否かを検出して、演算実行中フラグを生成する演算実行中フラグ生成回路と、

前記演算実行中フラグ生成回路が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、

入力される拡張されたビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第1レジスタ群と、

入力される拡張されないビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第2レジスタ群と、

前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を実行することを示す場合には前記第1レジスタ群を選択し、前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止することを示す場合には前記第2レジスタ群を選択する符号、指数及び仮数選択回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、演算結果の符号を生成する符号生成回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、被演算データの指数と演算データの指数とを調整して演算結果の指数を生成する指数生成回路と、

前記指数生成回路における前記被演算データの指数と演算データの指数との調整に対応して、被演算データの仮数と演算データの仮数との桁合わせを行なって演算結果の仮数を生成する仮数演算回路と、

前記演算結果の指数と仮数とを整合する整合回路と、

前記演算結果の符号と、前記整合回路で整合された前記演算結果の指数と仮数とを格納する演算結果格納レジスタとを備え、

前記実行中フラグ格納レジスタに格納された前記実行中フラグと、前記演算結果格納レジスタに格納された前記演算結果の符号、指数及び仮数とを、浮動小数点演算結果として出力することを特徴とする浮動小数点演算回路。

(付記10)

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータであって、

第1演算回路が、

当該第1演算回路への演算命令が、第1ビット幅の数値に対する演算であるか前記第1ビット幅より短い第2ビット幅の数値に対する演算であるかを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合に、前記第1ビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が前記第2ビット幅の数値に対する演算であると判定した場合に、前記第2ビット幅の数値の浮動小数点演算を実行する演算実行手段と、を有し、

第2演算回路が、前記第2ビット幅の数値の浮動小数点演算を実行する回路であって、

前記浮動小数点演算回路への演算命令が前記第1ビット幅の数値に対する演算が休止することを示す場合には、前記第2ビット幅の数値の浮動小数点演算を前記第1演算回路と前記第2演算回路とにより並列に実行することを特徴とするコンピュータ。

(付記11)

前記第1ビット幅の数値及び前記第2ビット幅の数値を前記休止判定手段の判定結果に応じて、前記第1演算回路に選択可能に入力する入力手段と、

前記演算制御手段において前記第1演算回路が前記第2ビット幅の数値を演算した演算結果と前記第2演算回路が前記第2ビット幅の数値を演算した演算結果とを選択して出力する出力手段とを含むことを特徴とする付記10に記載のコンピュータ。

(付記12)

前記コンピュータは、前記第1ビット幅の数値に対する演算が休止する場合に、前記第2ビット幅の数値に対する演算であることを示す演算命令を少なくとも前記第1演算回路に対して発行し、前記第2ビット幅の数値を前記第1演算回路及び前記第2演算回路に対して提供する命令発行制御手段をさらに有することを特徴とする付記10又は11に記載のコンピュータ。

(付記13)

前記命令発行制御手段に接続されて、前記演算命令と、前記浮動小数点演算回路において演算すべき前記第1ビット幅の数値及び前記第2ビット幅の数値とを前記命令発行制御手段に対して提供し、前記浮動小数点演算回路において演算した演算結果を一時記憶する主記憶手段と、

データの入出力を制御する入出力制御手段を介して前記命令発行制御手段に接続されて、前記浮動小数点演算回路において演算した演算結果を保存する外部記憶手段とを有することを特徴とする付記10乃至12のいずれか1項に記載のコンピュータ。

(付記14)

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御方法であって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、

を含むことを特徴とする演算制御方法。

(付記15)

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御プログラムであって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、をコンピュータに実行させることを特徴とする演算制御プログラム。

【技術分野】

【0001】

本発明は、スーパーコンピュータのベクトル演算などで高速な浮動小数点演算を行なうための演算技術に関する。

【背景技術】

【0002】

現在、スーパーコンピュータでは、単精度と倍精度と拡張精度の3種のデータを浮動小数点演算する必要がある。特に、ベクトル演算などでは、1つの演算処理が浮動小数点演算の多数回の繰り返しを含むため、各々の浮動小数点演算の短縮が演算処理の高速化に寄与する。また、回路構成を簡単にすることも演算処理の高速化に寄与する。たとえば、特許文献1では、128ビットの拡張精度データ幅の演算データを64ビット幅の上位と下位とに分け、64ビット幅の演算回路での2回の実行で1つの拡張精度データ幅の演算結果を求める。これにより、拡張精度データ幅の演算を少ないハードウェアにより実行できる。また、特許文献2では、16バイト幅(=128ビット幅)の演算器を2つの8バイト幅(=64ビット幅)に分割する。そして、分割した2つの8バイト幅の演算器で、8バイト幅(=64ビット幅)と4バイト幅((=32ビット幅))の演算データの演算を同時に実行できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平06−149544号公報

【特許文献2】特開平09−091118号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、単精度と倍精度と拡張精度の3種のデータを浮動小数点演算する場合にも、演算処理を高速化して演算実行時間を短縮するには、演算を並列に同時実行することが望ましい。また、限られたハードウェア資源を効率よく使用して演算処理を高速化して演算実行時間を短縮することで、業務の効率化とコンピュータシステムの消費電力が抑制できるハードウェアの提供が求められている。

【0005】

これに対して、上記特許文献1は、倍精度(64ビット=8バイト)の演算回路を使って拡張精度(128ビット=16バイト)の演算を実行するのみであり、いずれの演算もシーケンシャルにしか実行できない。一方、上記特許文献2は、拡張精度(16バイト=128ビット)の演算器を使って、単精度(4バイト=32ビット)と倍精度(8バイト=64ビット)の演算を同時に実行可能である。しかし、単精度同士/倍精度同士の並列演算はできない。

【0006】

本発明の目的は、上述の課題を解決する技術を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明に係る装置は、

第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、

演算命令に基づいて、前記第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定手段と、

前記休止判定手段が前記第1演算回路が休止すると判定した場合に、前記第1演算回路を前記第2ビット幅の数値の演算を行なうよう制御し、前記第2ビット幅の数値の演算を、前記第1演算回路と前記第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御手段と、

を備えることを特徴とする。

【0008】

上記目的を達成するため、本発明に係る装置は、

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

当該浮動小数点演算回路への演算命令が、拡張されたビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が拡張されたビット幅の数値に対する演算であると判定した場合は、前記拡張されたビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が拡張されたビット幅の数値に対する演算でないと判定した場合は、前記拡張されたビット幅より短いビット幅の数値の浮動小数点演算を実行する演算実行手段と、

を備えることを特徴とする。

【0009】

上記目的を達成するため、本発明に係る装置は、

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止するか否かを検出して、演算実行中フラグを生成する演算実行中フラグ生成回路と、

前記演算実行中フラグ生成回路が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、

入力される拡張されたビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第1レジスタ群と、

入力される拡張されないビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第2レジスタ群と、

前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を実行することを示す場合には前記第1レジスタ群を選択し、前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止することを示す場合には前記第2レジスタ群を選択する符号、指数及び仮数選択回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、演算結果の符号を生成する符号生成回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、被演算データの指数と演算データの指数とを調整して演算結果の指数を生成する指数生成回路と、

前記指数生成回路における前記被演算データの指数と演算データの指数との調整に対応して、被演算データの仮数と演算データの仮数との桁合わせを行なって演算結果の仮数を生成する仮数演算回路と、

前記演算結果の指数と仮数とを整合する整合回路と、

前記演算結果の符号と、前記整合回路で整合された前記演算結果の指数と仮数とを格納する演算結果格納レジスタとを備え、

前記実行中フラグ格納レジスタに格納された前記実行中フラグと、前記演算結果格納レジスタに格納された前記演算結果の符号、指数及び仮数とを、浮動小数点演算結果として出力することを特徴とする。

【0010】

上記目的を達成するため、本発明に係る装置は、

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータであって、

第1演算回路が、

当該第1演算回路への演算命令が、第1ビット幅の数値に対する演算であるか前記第1ビット幅より短い第2ビット幅の数値に対する演算であるかを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合に、前記第1ビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が前記第2ビット幅の数値に対する演算であると判定した場合に、前記第2ビット幅の数値の浮動小数点演算を実行する演算実行手段と、を有し、

第2演算回路が、前記第2ビット幅の数値の浮動小数点演算を実行する回路であって、

前記浮動小数点演算回路への演算命令が前記第1ビット幅の数値に対する演算が休止することを示す場合には、前記第2ビット幅の数値の浮動小数点演算を前記第1演算回路と前記第2演算回路とにより並列に実行することを特徴とする。

【0011】

上記目的を達成するため、本発明に係る方法は、

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御方法であって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、

を含むことを特徴とする。

【0012】

上記目的を達成するため、本発明に係るプログラムは、

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御プログラムであって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、をコンピュータに実行させることを特徴とする。

【発明の効果】

【0013】

本発明によれば、拡張精度演算回路と単・倍精度演算回路とにより単精度同士/倍精度同士の並列演算を実現し、演算処理を高速化して演算実行時間を短縮できる。

【図面の簡単な説明】

【0014】

【図1】本発明の第1実施形態の浮動小数点演算回路の構成を示すブロック図である。

【図2A】本発明の第2実施形態に係る浮動小数点演算回路を含むコンピュータの構成を示すブロック図である。

【図2B】本発明の第2実施形態に係る浮動小数点演算回路を含むコンピュータの演算処理手順を示すフローチャートである。

【図3】本発明の第2実施形態に係る浮動小数点演算回路に含まれる浮動小数点加減算回路の構成を示すブロック図である。

【図4】本発明の第2実施形態に係る浮動小数点加減算回路に含まれる拡張精度データ幅演算回路の構成を示すブロック図である。

【図5】本発明の第2実施形態に係る浮動小数点加減算回路に含まれる単精度・倍精度データ幅演算回路の構成を示すブロック図である。

【図6】本発明の第2実施形態に係る科学演算データ形式の一例を示す図である。

【図7】本発明の第2実施形態に係る演算命令生成の論理を示す図である。

【図8】本発明の第2実施形態に係る符号データ選択の論理を示す図である。

【図9】本発明の第2実施形態に係る指数データ選択の論理を示す図である。

【図10】本発明の第2実施形態に係る仮数データ選択の論理を示す図である。

【図11】本発明の第2実施形態に係る指数大小比較信号生成の論理を示す図である。

【図12】本発明の第2実施形態に係る基準指数選択の論理を示す図である。

【図13】本発明の第2実施形態に係る仮数選択回路の構成を示すブロック図である。

【図14】本発明の第2実施形態に係る被加算仮数データ選択の論理を示す図である。

【図15】本発明の第2実施形態に係る加算仮数と反転データ選択の論理を示す図である。

【図16】本発明の第2実施形態に係る加算仮数データ選択の論理を示す図である。

【図17】本発明の第2実施形態に係る中間符号生成の論理を示す図である。

【図18】本発明の第2実施形態に係る符号生成の論理を示す図である。

【図19】本発明の第2実施形態に係る拡張精度データ幅演算回路における拡張精度加算時の各レジスタのデータ値例を示す図である。

【図20】本発明の第2実施形態に係る拡張精度データ幅演算回路における拡張精度加算時の各信号線のデータ値例を示す図である。

【図21】本発明の第2実施形態に係る拡張精度データ幅演算回路における倍精度加算時の各レジスタのデータ値例を示す図である。

【図22】本発明の第2実施形態に係る拡張精度データ幅演算回路における倍精度加算時の各信号線のデータ値例を示す図である。

【発明を実施するための形態】

【0015】

以下に、図面を参照して、本発明の実施の形態について例示的に詳しく説明する。ただし、以下の実施の形態に記載されている構成要素はあくまで例示であり、本発明の技術範囲をそれらのみに限定する趣旨のものではない。

【0016】

[第1実施形態]

本発明の第1実施形態としての浮動小数点演算回路100について、図1を用いて説明する。図1において、浮動小数点演算回路100は、第1演算回路101と、第2演算回路102と、休止判定部103と、演算制御部104とを含む。第1演算回路101は、第1ビット幅の数値と第1ビット幅より短い第2ビット幅の数値とのいずれかを選択可能に演算する回路である。第2演算回路102は、第2ビット幅を演算する回路である。休止判定部103は、演算命令を解析して、演算命令が第1演算回路101による第1ビット幅の数値の演算を休止することを判定する。演算制御部104は、休止判定部103からの判定が第1ビット幅の数値の演算を休止することを示す場合に、第2ビット幅の数値を第1演算回路101に入力すると共に、第1演算回路101を第2ビット幅の数値の演算を行なうようする。

【0017】

本実施形態によれば、第1演算回路101による第1ビット幅の数値の演算が休止している時には、第1ビット幅より短い第2ビット幅の数値の演算を第1演算回路101と第2演算回路102で並列して実行できる。したがって、演算処理を高速化して演算実行時間が短縮される。

【0018】

[第2実施形態]

第2実施形態は、本実施形態の浮動小数点演算回路の回路構成と、この浮動小数点演算回路を使用した科学演算回路及びコンピュータの構成を示す。本実施形態では、たとえば、スーパーコンピュータのベクトル演算において、演算処理を高速化して演算実行時間を短縮することで、業務の効率化とコンピュータシステムの消費電力が抑制できる。

【0019】

〈第2実施形態の浮動小数点演算回路を使用したコンピュータの構成〉

図2Aは、第2実施形態の浮動小数点演算回路41、第2実施形態の浮動小数点演算回路41を使用した科学演算回路40、第2実施形態の浮動小数点演算回路41を使用したコンピュータ200のそれぞれの構成を示すブロック図である。

【0020】

(コンピュータの概略構成)

図2Aにおいて、コンピュータ200は、科学演算回路40と、主記憶装置43と、入出力制御装置44と、外部記憶装置45とを含む。主記憶装置43は、科学演算プログラムと図6に標準指数データ方式で示した単精度601/倍精度602/拡張精度603の3種の科学演算データ及び科学演算命令を記憶する。主記憶装置43は、演算結果の一時記憶としても使用される。科学演算回路40は、主記憶装置43より科学演算プログラムを読み出し、命令を解析し、命令を実行し、前記実行結果を主記憶装置43へ出力する。入出力制御装置44は、科学演算回路40が解析した命令により外部記憶装置45への科学演算結果の入出力を制御する。外部記憶装置45は、入出力制御装置44から送られてくるデータを命令にしたがって保存し、入出力制御装置44へ記憶しているデータを送る。ここで、信号線L110は科学演算回路40と主記憶装置43との間の入出力信号のための信号線である。また、信号線L111は科学演算回路40と入出力制御装置44との間の入出力信号、L112は入出力制御装置44と外部記憶装置45との間の入出力信号である。

【0021】

(科学演算回路の構成)

図2Aにおいて、科学演算回路40は、浮動小数点演算回路41と命令発行制御回路42とを含む。命令発行制御回路42は、主記憶装置43から読み込んだ科学演算データ及び科学演算命令を解析する。そして、浮動小数点演算回路41に、演算精度と演算種類とを示す演算命令と、被演算データ、演算データを発行し、浮動小数点演算回路41による演算結果を受け取って主記憶装置43又は外部記憶装置45に記憶する。たとえば、演算がベクトル演算のように同じ演算を繰り返す場合は、科学演算回路40で繰り返される。ここで、信号線L100〜L106は命令発行制御回路42から浮動小数点演算回路41への入力信号用の信号線、信号線L400とL401は浮動小数点演算回路41から命令発行制御回路42への出力信号用の信号線である。信号線L100は、演算命令である。信号線L101〜L106のうち、信号線L101〜L103は、単・倍精度又は拡張精度の演算をシーケンスに実行する場合に入力される数値の符号、指数及び仮数である。信号線L104〜L106は、単・倍精度の演算を並列して(パラレルに)実行する場合に、信号線L101〜L103と並列に入力される単・倍精度の数値の符号、指数及び仮数である。L400には単精度・倍精度データ幅演算回路からの演算結果が出力され、信号線L401には拡張精度データ幅演算回路からの演算結果が出力される。本実施形態では、信号線L100の演算命令が拡張精度データ幅演算回路を休止する命令であった場合には、信号線L400とL401の両方から2つの単・倍精度の演算結果が並列に出力される。

【0022】

(命令発行制御回路の動作手順)

図2Bは、命令発行制御回路42の動作手順を示すフローチャートである。なお、かかる命令発行制御回路42の動作は、ハードウェア、ソフトウェア、ファームウエア、マイクロプログラムなど、どのように構成されてもよい。したがって、図2Bのフローチャートは、プログラムの流れを示すのみではなく、ハードウェアの処理をも含むものである。また、実際には命令発行制御回路42から信号線L101〜L106に被演算データと演算データとが順次出力されてそれぞれのレジスタに保持されるが、ここでは煩雑であるのでその詳細な説明は省いている。また、本例では信号線L100上の演算命令のデータ幅が2ビットとして、拡張精度演算休止の命令と単・倍精度の演算命令とを別個に発行している。しかし、信号線L100のデータ幅が3ビット以上であれば、拡張精度演算休止の命令と単・倍精度の演算命令とを組み合わせて信号線L100に同時に出力できる。

【0023】

まず、ステップS201において、主記憶装置43から演算プログラムを読み出す。次に、ステップS203において、演算プログラムの命令を解析する。ステップS205において、解析の結果が単・倍精度演算か/拡張精度演算かの演算判定を行なう。

【0024】

判定結果が単・倍精度演算である場合は、拡張精度演算回路は休止すると判断してステップS207に進む。ステップS207において、信号線L100に拡張精度演算休止を示す命令を提供する。ステップS209においては信号線L100に単・倍精度演算命令を発行して、信号線L104〜L106に信号線L101〜L103と並列に単・倍精度データを提供する。ステップS211においては、信号線L400とL401とから2つの単・倍精度演算結果を取得する。ステップS213においては繰り返し演算か否かを判定し、繰り返しならばステップS209に戻ってステップS209からS213を繰り返す。繰り返しで無ければステップS221に進む。

【0025】

一方、ステップS205の判定で判定結果が拡張精度演算であれば、ステップS215においては信号線L100に拡張精度演算命令を発行して、信号線L101〜L103に拡張精度データを出力する。ステップS217においては、信号線L401から1つの拡張精度演算結果を取得する。ステップS219においては繰り返し演算か否かを判定し、繰り返しならばステップS215に戻ってステップS215からS219を繰り返す。繰り返しで無ければステップS221に進む。

【0026】

ステップS221において演算結果を主記憶装置43に記憶する。あるいは入出力制御装置44を介して外部記憶装置45に記憶してもよい。ステップS223においては演算プログラムの終了か否かを判定し、終了でなければステップS203に戻って次の命令を処理する。演算プログラムの終了であれば処理を終了する。そして、次の演算プログラムの主記憶装置43からの読出しに始まる一連の流れが続く。

【0027】

なお、図2Bの手順は一例であって、これに限定されない。

【0028】

(浮動小数点演算回路の構成)

図2Aにおいて、浮動小数点演算回路41は、浮動小数点加減算回路46と、浮動小数点乗算回路47と、浮動小数点除算回路48と、浮動小数点演算結果選択回路49とを含む。浮動小数点加減算回路46は、命令発行制御回路42が浮動小数点演算回路41に出力する命令のうち加減算命令を実行する。浮動小数点乗算回路47は、命令発行制御回路42が浮動小数点演算回路41に出力する命令のうち乗算命令を実行する。浮動小数点除算回路48は、命令発行制御回路42が浮動小数点演算回路41に出力する命令のうち除算命令を実行する。浮動小数点演算結果選択回路49は、各演算回路からの演算結果を選択して命令発行制御回路42に出力する。ここで、信号線L300〜L305とL310は、それぞれの回路を接続する信号線を表している。信号線L300,L302,L304は単・倍精度の演算回路の演算結果を出力する信号線であり、信号線L301,L303,L305は拡張精度の演算回路の演算結果を出力する信号である。信号線L310は、信号線L100の演算命令を解析して得られた拡張精度の演算回路が休止するか否かを出力する信号線である。本例では、拡張精度の演算回路が休止する場合に信号線L310に"1(ハイ)"が出力され、拡張精度の演算回路が演算する場合に信号線L310に"0(ロー)"が出力される。浮動小数点演算結果選択回路49により演算結果が選択されて信号線L400とL401に出力される。浮動小数点演算結果選択回路49においては、拡張精度の演算回路が休止して信号線L310が"1"である場合、信号線L400には信号線L300,L302,L304からの単・倍精度の演算結果が出力される。同時に、信号線L401には信号線L301,L303,L305からの単・倍精度の演算結果が並列に出力される。一方、拡張精度の演算回路が演算を実行する信号線L310が"0"である場合、信号線L401に信号線L301,L303,L305からの拡張精度の演算結果が出力される。

【0029】

(浮動小数点加減算回路の構成)

図3は、第2実施形態に係る浮動小数点演算回路41に含まれる浮動小数点加減算回路46の構成を示すブロック図である。なお、本実施形態では、以下浮動小数点加減算回路46の構成と動作を代表して説明する。しかし、浮動小数点乗算回路47及び浮動小数点除算回路48においても、単精度・倍精度データ幅用と拡張精度データ幅用との2つの演算回路を備えている。そして、拡張精度データ幅用の演算回路が拡張精度演算の休止中に単精度・倍精度データ幅の演算を並列に行なうことは同様であり、演算の種類が異なるのみで構成の特徴は変わらない。従って、本明細書では、浮動小数点加減算回路46などをも浮動小数点演算回路と総称している。

【0030】

図3の浮動小数点加減算回路46は、単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12とを有する。図2Aに示したように、浮動小数点加減算回路46には、単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12とがそれぞれの加減算を行なう場合は、信号線L100に"00"や"11"でないそれぞれの演算命令が入力される。本例では、演算命令の"00"や"11"は、拡張精度データ幅演算回路12の休止を示す命令である。その場合には、信号線L101〜L103を使って、それぞれの被演算データと演算データとが入力される。単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12との演算結果は、それぞれ信号線L300又はL301から出力される。信号線L310からは信号線L100に"00"や"11"が入力されなかったことを示す"0(ロー)"が出力される。

【0031】

一方、拡張精度データ幅演算回路12が拡張精度演算を休止する場合は、信号線L100に"00"又は"11"(拡張精度データ幅演算回路12の休止を示す命令)が入力される。その場合には、信号線L101〜L103を使って、単精度・倍精度データ幅演算回路11に単精度・倍精度の被演算データと演算データとが入力される。同時に、信号線L104〜L106を使って、拡張精度データ幅演算回路12に単精度・倍精度の被演算データと演算データとが入力される。単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12との単精度・倍精度データの演算結果は、信号線L300及びL301から並列に出力される。信号線L310からは信号線L100に"00"又は"11"が入力されたことを示す"1(ハイ)"が出力される。この信号線L310の"1(ハイ)"は、図2Aの浮動小数点演算結果選択回路49に対して、信号線L400とL401に単精度・倍精度データ幅演算回路11と拡張精度データ幅演算回路12とが並列に演算した演算結果を出力させる。

【0032】

(拡張精度データ幅演算回路の構成)

図4は、第2実施形態に係る浮動小数点加減算回路46に含まれる拡張精度データ幅演算回路12の構成を示すブロック図である。拡張精度データ幅演算回路12は、図6の603に示すフォーマットの拡張精度演算データの演算を行なうが、図6の601や602に示すフォーマットの単精度・倍精度演算データの演算を行なうことも可能である。従って、図4の拡張精度データ幅演算回路12の各レジスタや各回路は、拡張精度演算データの演算と単精度・倍精度演算データの演算とを実行可能に構成されており、その詳細は省略する。なお、以下の説明では、各回路の機能及び動作順を考慮している。また、拡張精度データ幅演算回路12の減算における動作は加算と符号を変えれば実質的に同様であるので、以下の説明は加算を中心に説明する。すなわち、以下で使用する文言「加算」は、特に図7〜図17において「加減算」を意味する。従って、本明細書では、特徴的な構成を有する拡張精度データ幅演算回路12をも浮動小数点演算回路と総称している。

【0033】

(A:入力データ用レジスタと出力データ用レジスタ)

拡張精度データ幅演算回路12は、命令発行制御回路42から信号線L100〜L106によって入力された信号を保持するレジスタ群を有する。レジスタ1は、信号線L100からの演算命令を保持する演算命令レジスタである。レジスタ2〜13は、信号線L101〜L106からの被演算データ及び演算データを保持するレジスタである。このうち、信号線L101〜L103に接続されたレジスタ2,4,6,8,10,12は、拡張精度データ幅演算回路12が拡張精度幅の加算を行なう場合に、拡張幅データを保持する第1レジスタ群である。第1レジスタ群は、さらに、被加算データの符号、指数、仮数を保持するレジスタ2,6,10と、加算データの符号、指数、仮数を保持するレジスタ4,8,12からなる。一方、信号線L104〜L106に接続されたレジスタ3,5,7,9,11,13は、拡張精度データ幅演算回路12が単精度・倍精度幅の加算を行なう場合に、単精度・倍精度幅データを保持する第2レジスタ群である。第2レジスタ群は、さらに、被加算データの符号、指数、仮数を保持するレジスタ3,7,11と、加算データの符号、指数、仮数を保持するレジスタ5,9,13からなる。

【0034】

一方、拡張精度データ幅演算回路12は、浮動小数点演算結果選択回路49に対して信号線L301,L310から出力する信号を保持するレジスタ14と15とを有する。レジスタ14は、演算結果の符号、指数、仮数を保持する演算結果格納レジスタである。レジスタ15は、信号線L100から入力されてレジスタ1に保持された演算命令から、演算実行中フラグ生成回路16によって生成された演算実行中フラグを保持する演算実行中フラグ格納レジスタである。この演算実行中フラグ生成回路16における、信号線L200のレジスタ1からの演算命令を入力とし、信号線L257の演算実行フラグを出力とする論理を含む、演算命令に基づく論理700を図7に示す。図7の演算命令701に基づいて演算実行フラグ702が生成される。図7に示すように、演算命令が"00"又は"11"の場合は演算実行フラグに"1"が出力されて、拡張精度データ幅演算回路12における拡張精度の演算休止が示される。したがって、レジスタ15は演算実行フラグ格納レジスタとして機能する。

【0035】

(B:単・倍精度/拡張精度の入力選択回路)

演算実行中フラグ生成回路16から出力する信号線L257の演算実行中フラグは、演算符号選択回路17、演算指数選択回路18及び演算仮数選択回路19に入力される。演算符号選択回路17、演算指数選択回路18及び演算仮数選択回路19は、信号線L257の演算実行中フラグに従って入力された符号、指数、仮数を選択して演算回路群に伝達する。

【0036】

演算符号選択回路17には、レジスタ2〜5からそれぞれ信号線L240〜L243に出力された被加算データ符号と加算データ符号とが入力される。演算符号選択回路17は、信号線L257の演算実行中フラグによる図8に示す論理800に従って、入力された符号を選択して信号線L253とL254とに出力する。演算実行中フラグが"0"の場合は、801で示すように、レジスタ2及び4からそれぞれ信号線L240及びL241に出力された拡張精度の被加算データ符号と加算データ符号とを選択して、信号線L253とL254に出力する。一方、演算実行中フラグが"1"の場合は、802で示すように、レジスタ3及び5からそれぞれ信号線L242及びL243に出力された単精度・倍精度の被加算データ符号と加算データ符号とを選択して、信号線L253とL254に出力する。

【0037】

演算指数選択回路18には、レジスタ6〜9からそれぞれ信号線L244〜L247に出力された被加算指数データと加算指数データとが入力される。演算指数選択回路18は、信号線L257の演算実行中フラグによる図9に示す論理900に従って、入力された指数データを選択して信号線L255とL256とに出力する。演算実行中フラグが"0"の場合は、901で示すように、レジスタ6及び8からそれぞれ信号線L244及びL245に出力された拡張精度の被加算指数データと加算指数データとを選択して、信号線L255とL256に出力する。一方、演算実行中フラグが"1"の場合は、902で示すように、レジスタ7及び9からそれぞれ信号線L246及びL247に出力された単精度・倍精度の被加算指数データと加算指数データとを選択して、信号線L255とL256に出力する。

【0038】

演算仮数選択回路19には、レジスタ10〜13からそれぞれ信号線L248〜L251に出力された被加算仮数データと加算仮数データとが入力される。演算仮数選択回路19は、信号線L257の演算実行中フラグによる図10に示す論理1000に従って、入力された仮数データを選択して信号線L258とL259とに出力する。演算実行中フラグが"0"の場合は、1001で示すように、レジスタ10及び12からそれぞれ信号線L248及びL249に出力された拡張精度の被加算仮数データと加算仮数データとを選択して、信号線L258とL259に出力する。一方、演算実行中フラグが"1"の場合は、1002で示すように、レジスタ11及び13からそれぞれ信号線L250及びL251に出力された単精度・倍精度の被加算仮数データと加算仮数データとを選択して、信号線L258とL259に出力する。

【0039】

(C:演算命令解析回路)

レジスタ1に保持された演算命令は、信号線L200により演算命令解析回路20に入力される。演算命令解析回路20は、図7の論理700に従って、信号線L200の演算命令と信号線L253の被加算データ符号と信号線L254の加算データ符号とに基づいて、演算命令解析結果を信号線L207から出力する。図7に示すように、演算命令解析結果の"0"は加算、"1"は減算であり、仮数選択回路25の制御に使用される。

【0040】

(D:指数選択回路と指数調整回路)

指数大小比較回路21は、演算指数選択回路18から信号線L255とL256に出力された被加算指数データと加算指数データとの大小を比較する。図11は、指数大小比較回路21における指数データと信号線L211に出力される値との論理1100を示す図である。信号線L255に出力された被加算指数データが信号線L256に出力された加算指数データよりも大きければ、信号線L211に"1"が出力される。信号線L255に出力された被加算指数データが信号線L256に出力された加算指数データよりも大きく無ければ、信号線L211に"0"が出力される。信号線L211の値は、基準指数選択回路22の選択と、中間符号生成回路24の中間符号生成と、仮数選択回路25の制御に使用される。

【0041】

基準指数選択回路22は、被加算仮数データと加算仮数データとの桁合わせをどちらに合わせて行なうかを決定する。図12は、基準指数選択回路22における信号線L211に出力される値に対応して信号線L209に出力される指数データの論理1200を示す図である。指数大小比較回路21からの信号線L211の出力値が"0"の場合は、被加算指数データが基準となり被加算指数データが信号線L209に出力される。指数大小比較回路21からの信号線L211の出力値が"1"の場合は、加算指数データが基準となり加算指数データが信号線L209に出力される。

【0042】

シフト量算出回路23は、演算指数選択回路18が選択したより大きい指数と選択されなかったより小さい指数の差を求めて、小さい仮数データを右シフトして桁合わせする右シフト量を求めて、信号線L210により桁合わせ右シフト回路27に送る。

【0043】

(E:仮数演算回路)

仮数選択回路25には、演算仮数選択回路19で選択されて信号線L258とL259に出力された被加算仮数と加算仮数とが入力されて、被加算仮数と加算仮数とを信号線L212とL213のいずれに出力するかを選択する。仮数選択回路25の選択は、指数大小比較回路21から信号線L211に出力された被加算指数と加算指数との大小比較結果と、演算命令解析回路20から信号線L207に出力された演算命令解析結果とに基づいて、行なわれる。すなわち、指数の小さい方を桁合わせが必要な仮数として出力し、他方を桁合わせが必要ない仮数として出力する。

【0044】

図13は、仮数選択回路25の内部構成を示す図である。仮数選択回路25は、仮数A選択回路50と、仮数B選択回路51と、仮数B反転選択回路52とからなる。

【0045】

仮数A選択回路50は、信号線L212に出力する仮数を、信号線L211の被加算指数と加算指数との大小比較結果に基づいて被加算仮数と加算仮数とのうち指数の小さい仮数を選択する。図14は、仮数A選択回路50の論理1400を示す図である。仮数B選択回路51と仮数B反転選択回路52とは、信号線L213に出力する仮数を、信号線L211の被加算指数と加算指数との大小比較結果と、信号線L207の演算命令解析結果とに基づいて被加算仮数と加算仮数とのうち指数の大きい仮数を選択する。図15は、仮数B選択回路51の論理1500を示す図である。仮数B選択回路51から出力される信号線L280には選択された仮数がそのまま出力され、信号線L281には選択された仮数を反転したデータが出力される。仮数B反転選択回路52は、仮数B選択回路51から出力された信号線L280の仮数と信号線L281の反転仮数とを信号線L211の演算命令解析結果に基づいて選択し、信号線L213に出力する。図16は、仮数B反転選択回路52の論理1600を示す図である。演算命令解析結果が"0"(加算)の場合は信号線L280の反転しない仮数を信号線L213に出力し、演算命令解析結果が"1"(減算)の場合は信号線L280の反転した仮数を信号線L213に出力する。

【0046】

桁合わせ右シフト回路27は、信号線L212から入力された指数の小さな仮数を、シフト量算出回路23から信号線L210に出力された大小指数の差だけ右シフトして、加減算回路29で演算する仮数の桁合わせを行なう。加減算回路29は、桁合わせ右シフト回路27の桁合わせした信号線L215の仮数データと桁合わせが必要ない信号線L213の仮数データとを加算した加減算結果を、信号線L216に出力する。同時に、指数が同じ数値で、小さい被加算仮数から大きい加算仮数を減算した場合を検出して、信号線L220にその結果を出力する。指数が同じ数値で、小さい被加算仮数から大きい加算仮数を減算した場合に、"1"が出力される。

【0047】

0桁数チェック回路28は、加減算回路29が信号線L216に出力する演算結果の上位における"0"データの有無を検出して信号線L217に出力する。そして、正規化左シフト回路31は、0桁数チェック回路28が信号線L217出力した数値分を左シフトして演算結果の仮数を正規化し、演算結果の仮数として信号線L218に出力する。信号線L218の正規化された演算結果の仮数は、レジスタ14に送られて保持される。

かかる正規化左シフト回路31と0桁数チェック回路28は、演算結果の仮数と指数とを整合する整合回路として機能する。

【0048】

(F:指数生成回路)

指数生成減算回路30は、基準指数選択回路22から信号線L209に出力された大きな指数を入力する。そして、0桁数チェック回路28が信号線L217に出力した数値分だけ演算結果が正規化左シフト回路31で左シフトされるのに合わせて、信号線L209の指数から信号線L217の数値を減算して、演算結果の指数として信号線L219に出力する。信号線L219の生成符号は、レジスタ14に送られて保持される。

【0049】

(G:符号生成回路)

演算符号選択回路17から信号線L253とL254に出力された被加算データ符号と加算データ符号とは、中間符号生成回路24に入力される。中間符号生成回路24は、指数大小比較回路21からの信号線L211の値に基づいて、信号線L253とL254から入力された被加算データ符号と加算データ符号とのいずれかを選択して、信号線L208に出力する。図17は、中間符号生成回路24の論理1700を示す図である。中間符号生成回路24は、大きなデータの符号を選択して出力する。すなわち、信号線L211の値が"0"(加算指数データが被加算指数データ以上)の場合は、加算データ符号を信号線L208に出力する。一方、信号線L211の値が"1"(加算指数データが被加算指数データより小さい)の場合は、被加算データ符号を信号線L208に出力する。

【0050】

符号生成回路26は、中間符号生成回路24が出力した信号線L208の中間符号を入力する。そして、加減算回路29の指数が同じ数値で、小さい被加算仮数から大きい加算仮数を減算した場合を検出して信号線L220に出力した結果に基づいて、中間符号を調整する。図18は、符号生成回路26の論理1800を示す図である。信号線L220の符号反転信号が"1"の場合に、中間符号が反転されて生成符号となる。符号生成回路26は、生成した生成符号を演算結果の符号として信号線L214に出力する。信号線L214の生成符号は、レジスタ14に送られて保持される。

【0051】

図4の拡張精度データ幅演算回路12の構成により、拡張精度データ幅演算回路12で拡張精度演算が休止中に単・倍精度演算が実行可能となる。すなわち、信号線L100から入力された演算命令が拡張精度演算であれば、信号線L101〜L103から入力された拡張精度データ幅の数値データが演算される。そして、レジスタ14に拡張精度の演算結果が保持され、レジスタ15に拡張精度演算を示す"0"が保持されて、信号線L301とL310から出力される。一方、信号線L100から入力された演算命令が拡張精度演算でなければ、信号線L104〜L106から入力された他・倍精度データ幅の数値データが演算される。そして、レジスタ14に単・倍精度の演算結果が保持され、レジスタ15に単・倍精度演算を示す"1"が保持されて、信号線L301とL310から出力される。

【0052】

(単精度・倍精度データ幅演算回路11の構成)

図5は、第2実施形態に係る浮動小数点加減算回路46に含まれる単精度・倍精度データ幅演算回路11の構成を示すブロック図である。図5の単精度・倍精度データ幅演算回路11は、図4の拡張精度データ幅演算回路12の構成とは以下の点が異なっている以外は、データ幅の違いはあるが同じ名称の構成要素の機能は同様であるので、詳細な説明は省く。各レジスタ、指数演算に係る回路及び仮数演算に係る回路のデータ幅が、図6に示す単精度・倍精度演算データのフォーマットに適応されるのみである。

【0053】

図5のレジスタ70は図4のレジスタ1に相当する。図5のレジスタ71〜76は、図4のレジスタ2,4,6,8,10,12に相当する。図5の演算命令解析回路77は、図4の演算命令解析回路20に相当する。図5の指数大小比較回路81は、図4の指数大小比較回路21に相当する。図5の基準指数選択回路79は、図4の基準指数選択回路22に相当する。図5のシフト量算出回路80は、図4のシフト量算出回路23に相当する。図5の仮数選択回路82は、図4の仮数選択回路25に相当する。図5の桁合わせ右シフト回路84は、図4の桁合わせ右シフト回路27に相当する。図5の加減算回路86は、図4の加減算回路29に相当する。図5の0桁数チェック回路85は、図4の0桁数チェック回路28に相当する。図5の正規化左シフト回路88は、図4の正規化左シフト回路31に相当する。図5の指数生成減算回路87は、図4の指数生成減算回路30に相当する。図5の中間符号生成回路78は、図4の中間符号生成回路24に相当する。図5の符号生成回路83は、図4の符号生成回路26に相当する。図5のレジスタ89は図4のレジスタ14に相当する。

【0054】

単精度・倍精度データ幅演算回路11は、拡張精度データ幅演算回路12の信号線L104〜L106の入力データを保持するレジスタ群、入力データを選択する演算符号選択回路17、演算指数選択回路18及び演算仮数選択回路19を有していない。また、選択信号である演算実行中フラグを生成する演算実行中フラグ生成回路16とそれを保持するレジスタ15を有していない。

【0055】

図4の拡張精度データ幅演算回路12と図5の単精度・倍精度データ幅演算回路11とを含む構成により、図3の浮動小数点加減算回路46は以下のように動作する。拡張精度演算であれば、拡張精度データ幅演算回路12の信号線L301から拡張精度の演算結果が出力される。一方、単・倍精度演算であれば、単・倍精度データ幅演算回路11の信号線L300から1つの単・倍精度演算結果が出力される。さらに並列に、拡張精度データ幅演算回路12の信号線L301からもう1つの単・倍精度の演算結果が出力される。拡張精度演算か単・倍精度演算かは信号線L310の信号により示される。

【0056】

図3の浮動小数点加減算回路46を含む構成により、図2Aの科学演算回路40は以下のように動作する。拡張精度演算か単・倍精度演算かは信号線L310の信号により示される。拡張精度演算であれば、拡張精度データ幅演算回路12の信号線L301から出力された拡張精度の演算結果が浮動小数点演算結果選択回路49で選択されて、信号線L401により命令発行制御回路42に戻される。一方、単・倍精度演算であれば、単・倍精度データ幅演算回路11の信号線L300から出力された1つの単・倍精度演算結果が信号線L400により命令発行制御回路42に戻される。さらに並列に、拡張精度データ幅演算回路12の信号線L301から出力されたもう1つの単・倍精度の演算結果が信号線L401により命令発行制御回路42に戻される。

【0057】

〈第2実施形態の拡張精度データ幅演算回路を有する浮動小数点演算回路の動作手順〉

以下、第2実施形態の浮動小数点演算回路の具体的動作として、浮動小数点加減算回路46の処理例を説明する。本実施形態では、拡張精度データ幅演算回路12が休止中であることを条件に、命令発行制御回路42から拡張精度データ幅演算回路12に単精度・倍精度演算命令と単精度・倍精度の32ビット幅又は64ビット幅のデータとを転送する。これにより、拡張精度データ幅演算回路12において単精度・倍精度の演算結果を得ることができる。なお、単精度・倍精度データ幅演算回路11の動作と拡張精度データ幅演算回路12の単精度・倍精度演算は類似であるので、拡張精度データ幅演算回路12の拡張精度演算と単精度・倍精度演算について説明する。

【0058】

(拡張精度データ幅演算回路12の拡張精度演算時における動作手順)

以下、拡張精度データ幅の演算、"1000000000000000000000000000×162"(被加算データ)+"7FFFFFFFFFFFFFFFFFFFFFFFFFFF×164"(加算データ)、を1回加算する動作を説明する。なお、取り扱う浮動小数点演算データは、所謂、標準指数データ形式と拡張指数データ形式とIEEE指数データ形式との内、図6に示す標準指数データ形式(符号データ1ビット、指数データ7ビットを2桁の16進数表記、仮数データ112ビットを28桁の16進数表記)を用いて説明する。

【0059】

図19と図20は、かかる動作の説明における各レジスタ値1900と各信号線の数値2000とを示す図である。

【0060】

命令発行制御回路42からの信号線L100の加算命令として、レジスタ1に加算命令の数値"01"が格納される。また、前述の拡張精度データ幅の被加算データと加算データとより、レジスタ2に被加算データの符号数値"0"(正符号)が、レジスタ4に加算データの符号数値"0"(正符号)が格納される。また、レジスタ6に被加算データの指数値"02"が、レジスタ8に加算データの指数値"04"が格納される。また、レジスタ10に被加算仮数データ値"1000000000000000000000000000"が、レジスタ12に加算仮数データ値"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"がそれぞれ格納される。

【0061】

演算実行中フラグ生成回路16は、図7の演算命令生成論理700からレジスタ1からの信号線L200の信号が"01"の拡張精度データ幅の加算命令であることから、演算テータ選択信号として"0"を信号線L257に出力する。信号線L257の"0"を条件として、演算符号選択回路17は、図8の符号データ選択論理800から信号線L240とL242の拡張精度データ幅の被加算符号データを選択して、信号線L253とL254に共に"0"(正符号)を出力する。演算指数選択回路18は、図9の指数データ選択論理900から信号線L244とL245の拡張精度データ幅の指数データを選択して、信号線L255に"02"、信号線L256"04"を出力する。演算仮数選択回路19は、図10の仮数データ選択論理1000から信号線L248とL249の拡張精度データ幅の仮数データを選択する。そして、それぞれ信号線L258に"1000000000000000000000000000"、信号線L259に"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"を出力する。

【0062】

演算命令解析回路20は、信号線L200の演算命令の数値"01"(加算命令)と、信号線L253の数値"0"(正符号)と、信号線L254の数値"0"(正符号)との条件から、図7の演算命令生成論理700から加算命令となることを解析し、信号線L207に数値"0"(加算命令)を出力する。

【0063】

指数大小比較回路21は、信号線L255の被加算指数データの数値"02"と信号線L256の加算指数データの数値"04"とを大小比較する。比較結果として、図11の指数大小比較論理1100から信号線L256の指数データを大きいと判定して、指数大小比較結果信号として信号線L211に数値"0"を出力する。基準指数選択回路22は、信号線L211の指数大小比較結果の数値"0"の条件から、図12の基準指数選択論理1200から大きい加算指数データである信号線L256の数値"04"を選択して、信号線L209に出力する。シフト量算出回路23は、信号線L255の被加算データの指数の数値"02"と、信号線L256の加算データの指数の数値"04"との差を求め、桁合わせのための右シフト量として信号線L210に数値"2"を出力する。

【0064】

仮数選択回路25は、信号線L211の指数大小比較結果信号が"0"で加算データの指数が大きいので、図10の被加算仮数データ選択結果論理1400から被加算データの仮数と加算データの仮数との入れ替えは必要ないと判断する。従って、信号線L258の被加算仮数データを選択し、信号線L212に被加算仮数データ"1000000000000000000000000000"を出力する。一方、図15の加算仮数データと加算反転仮数データの選択論理1500から、信号線L259の加算仮数データの数値、"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L280に出力する。また、信号線L259の補数、"1000000000000000000000000000"を信号線L281に出力する。そして、信号線L207の演算命令解析結果信号の"0(加算)"を条件に、図16の加算仮数データ選択論理1600から、信号線L280の加算仮数データ、"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L213の仮数選択信号として選択して出力する。桁合わせ右シフト回路27は、信号線L210の右シフト量信号の数値"2"に基づいて2桁右シフトをすることから、被加算データの仮数の数値として"0010000000000000000000000000"を信号線L215に出力する。加減算回路29は、信号線L215の数値"0010000000000000000000000000"と、信号線L213の数値"7FFFFFFFFFFFFFFFFFFFFFFFFFFF"とを加算する。そして、加算結果の数値、"800FFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L216に出力する。

【0065】

0桁数チェック回路28は、信号線L216の加算結果信号の数値"800FFFFFFFFFFFFFFFFFFFFFFFFF"の"8"を先頭に上の桁に数値"0"の有無をチェックする。信号線L216の数値の先頭が"8"で先頭データに"1"の数値が存在することを確認すると、信号線L217に0桁数チェック信号の数値"0"を出力する。信号線L217の"0"は、正規化のための左シフトが不要であることから正規化左シフト回路31は正規化のための左シフトは行わず、結果として数値"800FFFFFFFFFFFFFFFFFFFFFFFFF"を信号線L218に出力する。

【0066】

指数生成減算回路30は、信号線L209の基準指数選択結果の数値"04"から信号線L217の0桁数チェック信号の数値"0"を減算して、信号線L219に指数データの数値"04"を出力する。

【0067】

中間符号生成回路24は、信号線L211の指数大小比較結果信号の数値"0"と、信号線L253の被加算符号テータ及び信号線L254の加算符号データの"0"の条件から、図17の中間符号生成論理1700から、信号線L254の大きい指数の符号の数値"0"(正符号)を信号線L208に出力する。そして、符号生成回路26は、演算を実行する被加算仮数と加算仮数の数値から小さい被加算仮数データから大きい加算仮数データを減算することはないので、信号線L220に"0"を出力する。信号線L220の"0"の条件に基づき、図18の符号生成論理1700から符号を反転することなく信号線L214に数値"0"(正符号)を出力する。

【0068】

レジスタ14は、符号生成回路26で生成した信号線L214の符号値"0"(正符号)を格納する。また、指数生成減算回路30で求めた信号線L219の指数データ"04"と、正規化左シフト回路31が信号線L218に出力した仮数データ"800FFFFFFFFFFFFFFFFFFFFFFFFF"とを格納する。そして、演算結果として信号線L301により出力する。また、レジスタ15は、演算実行中フラグ生成回路16の信号線L257への出力"0"を格納し、信号L310により出力する。

【0069】

以上で、"1000000000000000000000000000×162"+"7FFFFFFFFFFFFFFFFFFFFFFFFFFF×164"の加算が完了し、この結果を、図2Aの浮動小数点加減算回路46から浮動小数点加減算結果を信号線L301により出力する。浮動小数点演算結果選択回路49は、信号線L301の拡張精度の加算結果を信号線L401により命令発行制御回路42に出力して、拡張精度の1回の演算が完了する。

【0070】

この加算の解は、"800FFFFFFFFFFFFFFFFFFFFFFFFF×164"である。このように、信号線L219の指数の数値が"04"であり、信号線L218に仮数の数値が"800FFFFFFFFFFFFFFFFFFFFFFFFF"であることから一致する。

【0071】

同様に、図2に示す浮動小数点演算回路41の浮動小数点乗算回路47は信号線L303に拡張精度の演算結果を、浮動小数点除算回路48は信号線L305に拡張精度の演算結果を出力する。これらの拡張精度の演算結果は、浮動小数点演算結果選択回路49から命令発行制御回路42に戻されて、加減算と乗算と除算の拡張精度の1回の演算は完了する。

【0072】

(拡張精度データ幅演算回路12の単・倍精度演算時における動作手順)

以下、倍精度データ幅の演算、"10000000000000xxxxxxxxxxxxxx×162"(被加算データ)"(被加算データ)+"7FFFFFFFFFFFFFxxxxxxxxxxxxxx×164"(加算データ)、を1回加算する動作を説明する。なお、取り扱う浮動小数点演算データは、所謂、標準指数データ形式と拡張指数データ形式とIEEE指数データ形式との内、図6に示した標準データ形式(符号データ1ビット、指数データ7ビットを2桁の16進数表記、仮数データ56ビットを14桁の16進数表記)を用いて説明する。なお、単精度の演算も同様であり、説明は省略する。

【0073】

図21と図22は、かかる動作の説明における各レジスタ値2100と各信号線の数値2200とを示す図である。

【0074】

まず、命令発行制御回路42からの信号線L100の演算命令として、レジスタ1に数値"00"または"11"が格納される。レジスタ1からの信号線L200は演算実行中フラグ生成回路16に入力され、図7の論理700に従って信号線L257には演算実行中フラグが"1"で出力される。この演算実行中フラグの"1"で信号線L104〜L106から入力される倍精度データが演算符号、演算指数、演算仮数として選択される。また、演算実行中フラグの"1"は、レジスタ15に格納されて信号線L310から出力され、図2Aに図示の浮動小数点演算結果選択回路49における演算結果の選択に使用される。

【0075】

次に、命令発行制御回路42からの信号線L100の加算命令として、レジスタ1に加算命令の数値"01"が格納される。また、前述の倍精度データ幅の被加算データと加算データとより、レジスタ2に被加算データの符号数値"0"(正符号)が、レジスタ4に加算データの符号数値"0"(正符号)が格納される。また、レジスタ10に被加算仮数データ値"10000000000000xxxxxxxxxxxxxx"が、レジスタ12に加算仮数データ値"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"がそれぞれ格納される。

【0076】

演算命令解析回路20は、拡張精度の演算時と同様に、信号線L200の演算命令の数値"01"(加算命令)と、信号線L253の数値"0"(正符号)と、信号線L254の数値"0"(正符号)との条件から、図7の演算命令生成論理700から加算命令となることを解析し、信号線L207に数値"0"(加算命令)を出力する。

【0077】

指数の処理も拡張精度の演算時と同様である。指数大小比較回路21は、信号線L255の被加算指数データの数値"02"と信号線L256の加算指数データの数値"04"とを大小比較する。比較結果として、図11の指数大小比較論理1100から信号線L256の指数データを大きいと判定して、指数大小比較結果信号として信号線L211に数値"0"を出力する。基準指数選択回路22は、信号線L211の指数大小比較結果の数値"0"の条件から、図12の基準指数選択論理1200から大きい加算指数データである信号線L256の数値"04"を選択して、信号線L209に出力する。シフト量算出回路23は、信号線L255の被加算データの指数の数値"02"と、信号線L256の加算データの指数の数値"04"との差を求め、桁合わせのための右シフト量として信号線L210に数値"2"を出力する。

【0078】

仮数選択回路25は、信号線L211の指数大小比較結果信号が"0"で加算データの指数が大きいので、図10の被加算仮数データ選択結果論理1400から被加算データの仮数と加算データの仮数との入れ替えは必要ないと判断する。 従って、信号線L258の被加算仮数データを選択し、信号線L212に被加算仮数データ"10000000000000xxxxxxxxxxxxxx"を出力する。

【0079】

一方、図15の加算仮数データと加算反転仮数データの選択論理1500から、信号線 L259の加算仮数データの数値、"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L280に出力する。また、信号線L259の補数、"10000000000000xxxxxxxxxxxxxx"を信号線L281に出力する。そして、信号線L207の演算命令解析結果信号の"0(加算)"を条件に、図16の加算仮数データ選択論理1600から、信号線L280の加算仮数データ、"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L213の仮数選択信号として選択して出力する。桁合わせ右シフト回路27は、信号線L210の右シフト量信号の数値"2"に基づいて2桁右シフトをすることから、被加算データの仮数の数値として"00100000000000xxxxxxxxxxxxxx"を信号線 L215に出力する。加減算回路29は、信号線L215の数値"00100000000000xxxxxxxxxxxxxx"と、信号線L213の数値"7FFFFFFFFFFFFFxxxxxxxxxxxxxx"とを加算する。そして、加算結果の数値、"800FFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L216に出力する。

【0080】

0桁数チェック回路28のチェックは、拡張精度の場合と倍精度の場合で異なっている。0桁数チェック回路28は、信号線L216の加算結果信号の数値"800FFFFFFFFFFFxxxxxxxxxxxxxx"の"8"を先頭に上の桁に数値"0"の有無をチェックする。信号線L216の数値の先頭が"8"で先頭データに"1"の数値が存在することを確認すると、信号線L217に0桁数チェック信号の数値"0"を出力する。信号線L217の"0"は、正規化のための左シフトが不要であることから正規化左シフト回路31は正規化のための左シフトは行わず、結果として数値"800FFFFFFFFFFFxxxxxxxxxxxxxx"を信号線L218に出力する。

【0081】

指数生成減算回路30は、信号線L209の基準指数選択結果の数値"04"から信号線L217の0桁数チェック信号の数値"0"を減算して、信号線L219に指数データの数値"04"を出力する。

【0082】

中間符号生成回路24は、信号線L211の指数大小比較結果信号の数値"0"と、信号線L253の被加算符号テータ及び信号線L254の加算符号データの"0"の条件から、図17の中間符号生成論理1700から、信号線L254の大きい指数の符号の数値"0"(正符号)を信号線L208に出力する。そして、符号生成回路26は、演算を実行する被加算仮数と加算仮数の数値から小さい被加算仮数データから大きい加算仮数データを減算することはないので、信号線L220に"0"を出力する。信号線L220の"0"の条件に基づき、図18の符号生成論理1700から符号を反転することなく信号線L214に数値"0"(正符号)を出力する。

【0083】

レジスタ14は、符号生成回路26で生成した信号線L214の符号値"0"(正符号)を格納する。また、指数生成減算回路30で求めた信号線L219の指数データ"04"と、正規化左シフト回路31が信号線L218に出力した仮数データ"800FFFFFFFFFFFxxxxxxxxxxxxxx"とを格納する。そして、演算結果として信号線L301により出力する。また、レジスタ15は、演算実行中フラグ生成回路16の信号線L257への出力"0"を格納し、信号L310により出力する。

【0084】

以上で、倍精度の"00100000000000xxxxxxxxxxxxxx×162"+"7FFFFFFFFFFFFFxxxxxxxxxxxxxx×164"の加算が完了し、この結果を、図2Aの浮動小数点加減算回路46から浮動小数点加減算結果を信号線L301により出力する。

【0085】

同様に、図2に示す浮動小数点演算回路41の浮動小数点乗算回路47は信号線L302とL303に並列に2つの倍精度の演算結果を、浮動小数点除算回路48は信号線L304とL305に並列の2つの倍精度の演算結果を出力する。これらの倍精度の2つの演算結果は、浮動小数点演算結果選択回路49から命令発行制御回路42に信号線L400とL401により並列に戻されて、加減算と乗算と除算の倍精度のそれぞれ2回の演算は完了する。

【0086】

以上、拡張精度データ幅演算回路12の拡張精度演算時または倍精度演算時における動作手順を示した。単精度・倍精度データ幅演算回路11の動作手順は、拡張精度演算の中止と演算データの選択が無い場合の拡張精度データ幅演算回路12の倍精度演算時における動作手順と類似である。

【0087】

本実施形態によれば、128ビットの拡張精度のデータ幅の演算回路で32ビットの単精度データ幅と64ビットの倍精度データ幅の演算が実行できる。従って、既存の単精度・倍精度データ幅の演算回路と同時に拡張精度の演算回路との2つの演算回路で並列に演算ができることで、演算時間が1/2に短縮できることにある。その理由は、拡張演算回路が演算実行中又は未使用であることを検出する回路を設けている。そして、拡張データ幅の演算回路が未使用である場合に単精度倍精度と拡張精度データ幅の演算データを拡張演算回路に振り向けて実行できる回路を設けていることにある。本実施形態は、特にスーパーコンピュータなどでのベクトル演算における多回数の繰り返し演算において、より顕著な効果を発揮する。

【0088】

[他の実施形態]

以上、本発明の実施形態について詳述したが、それぞれの実施形態に含まれる別々の特徴を如何様に組み合わせたシステム又は装置も、本発明の範疇に含まれる。

【0089】

また、本発明は、複数の機器から構成されるシステムに適用しても良いし、単体の装置に適用しても良い。さらに、本発明は、実施形態の機能を実現する演算制御プログラムが、システムあるいは装置に直接あるいは遠隔から供給される場合にも適用可能である。したがって、本発明の機能をコンピュータで実現するために、コンピュータにインストールされる演算制御プログラム、あるいはその演算制御プログラムを格納した記憶媒体、その演算制御プログラムをダウンロードさせるWWWサーバも、本発明の範疇に含まれる。

【0090】

[実施形態の他の表現]

上記の実施形態の一部又は全部は、以下の付記のようにも記載されうるが、以下には限られない。

(付記1)

第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、

演算命令に基づいて、前記第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定手段と、

前記休止判定手段が前記第1演算回路が休止すると判定した場合に、前記第1演算回路を前記第2ビット幅の数値の演算を行なうよう制御し、前記第2ビット幅の数値の演算を、前記第1演算回路と前記第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御手段と、

を備えることを特徴とする浮動小数点演算回路。

(付記2)

前記第1ビット幅の数値及び前記第2ビット幅の数値を前記休止判定手段の判定結果に応じて、前記第1演算回路に選択可能に入力する入力手段を有することを特徴とする付記1に記載の浮動小数点演算回路。

(付記3)

前記演算制御手段において前記第1演算回路が前記第2ビット幅の数値を演算した演算結果と前記第2演算回路が前記第2ビット幅の数値を演算した演算結果とを選択して出力する出力手段を含むことを特徴とする付記1又は2に記載の浮動小数点演算回路。

(付記4)

前記第1演算回路は、

前記第1演算回路への演算命令が、前記第1ビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合は、前記第1ビット幅の数値に対して浮動小数点演算を実行し、前記演算判定手段が前記第1ビット幅の数値に対する演算でないと判定した場合は、前記第2ビット幅の数値に対して浮動小数点演算を実行する演算実行手段と、

を有することを特徴とする付記1乃至3のいずれか1項に記載の浮動小数点演算回路。

(付記5)

前記演算判定手段は、

演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて前記第1演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記第1演算回路を休止するか否かの前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記第1ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記第2ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から得た浮動小数点演算結果を格納する演算結果格納レジスタと、を有することを特徴とする付記1乃至4のいずれか1項に記載の浮動小数点演算回路。

(付記6)

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

当該浮動小数点演算回路への演算命令が、拡張されたビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が拡張されたビット幅の数値に対する演算であると判定した場合は、前記拡張されたビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が拡張されたビット幅の数値に対する演算でないと判定した場合は、前記拡張されたビット幅より短いビット幅の数値の浮動小数点演算を実行する演算実行手段と、

を備えることを特徴とする浮動小数点演算回路。

(付記7)

前記演算判定手段は、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記拡張されたビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記拡張されたビット幅より短いビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から浮動小数点演算結果を格納する演算結果格納レジスタと、

を有することを特徴とする付記6に記載の浮動小数点演算回路。

(付記8)

前記浮動小数点演算回路が行なう演算が、加算又は減算である場合に、

前記演算実行手段は、

前記演算実行中フラグに基づいて指数のデータ幅に合った指数を選択する基準指数選択回路と、

前記演算実行中フラグに基づいて指数の差を求めて桁合わせ右シフト量を求めるシフト量算出回路と、

第1データの仮数が格納される第1レジスタと、

第2データの仮数が格納される第2レジスタと、

前記第1データの仮数及び前記第2データの仮数のうち、前記演算実行中フラグに基づいて指数の小さい方を桁合わせが必要な仮数として出力し、他方を桁合わせが必要ない仮数として出力する仮数選択回路と、

前記仮数選択回路から出力された桁合わせが必要な仮数を、前記第1データの仮数及び前記第2データの前記演算実行中フラグに基づく指数の差に応じたシフト量だけ右シフトして、シフトした結果を出力する桁合わせ右シフト回路と、

前記桁合わせ右シフト回路から出力される前記桁合わせが必要な仮数のシフトした結果と前記仮数選択回路から出力される桁合わせが必要ない仮数との加減算を行って、加減算結果を出力する加減算回路と、

前記加減算回路から出力された前記加減算結果を正規化する正規化左シフト回路と、

を備えることを特徴とする付記7に記載の浮動小数点演算回路。

(付記9)

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止するか否かを検出して、演算実行中フラグを生成する演算実行中フラグ生成回路と、

前記演算実行中フラグ生成回路が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、

入力される拡張されたビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第1レジスタ群と、

入力される拡張されないビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第2レジスタ群と、

前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を実行することを示す場合には前記第1レジスタ群を選択し、前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止することを示す場合には前記第2レジスタ群を選択する符号、指数及び仮数選択回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、演算結果の符号を生成する符号生成回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、被演算データの指数と演算データの指数とを調整して演算結果の指数を生成する指数生成回路と、

前記指数生成回路における前記被演算データの指数と演算データの指数との調整に対応して、被演算データの仮数と演算データの仮数との桁合わせを行なって演算結果の仮数を生成する仮数演算回路と、

前記演算結果の指数と仮数とを整合する整合回路と、

前記演算結果の符号と、前記整合回路で整合された前記演算結果の指数と仮数とを格納する演算結果格納レジスタとを備え、

前記実行中フラグ格納レジスタに格納された前記実行中フラグと、前記演算結果格納レジスタに格納された前記演算結果の符号、指数及び仮数とを、浮動小数点演算結果として出力することを特徴とする浮動小数点演算回路。

(付記10)

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータであって、

第1演算回路が、

当該第1演算回路への演算命令が、第1ビット幅の数値に対する演算であるか前記第1ビット幅より短い第2ビット幅の数値に対する演算であるかを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合に、前記第1ビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が前記第2ビット幅の数値に対する演算であると判定した場合に、前記第2ビット幅の数値の浮動小数点演算を実行する演算実行手段と、を有し、

第2演算回路が、前記第2ビット幅の数値の浮動小数点演算を実行する回路であって、

前記浮動小数点演算回路への演算命令が前記第1ビット幅の数値に対する演算が休止することを示す場合には、前記第2ビット幅の数値の浮動小数点演算を前記第1演算回路と前記第2演算回路とにより並列に実行することを特徴とするコンピュータ。

(付記11)

前記第1ビット幅の数値及び前記第2ビット幅の数値を前記休止判定手段の判定結果に応じて、前記第1演算回路に選択可能に入力する入力手段と、

前記演算制御手段において前記第1演算回路が前記第2ビット幅の数値を演算した演算結果と前記第2演算回路が前記第2ビット幅の数値を演算した演算結果とを選択して出力する出力手段とを含むことを特徴とする付記10に記載のコンピュータ。

(付記12)

前記コンピュータは、前記第1ビット幅の数値に対する演算が休止する場合に、前記第2ビット幅の数値に対する演算であることを示す演算命令を少なくとも前記第1演算回路に対して発行し、前記第2ビット幅の数値を前記第1演算回路及び前記第2演算回路に対して提供する命令発行制御手段をさらに有することを特徴とする付記10又は11に記載のコンピュータ。

(付記13)

前記命令発行制御手段に接続されて、前記演算命令と、前記浮動小数点演算回路において演算すべき前記第1ビット幅の数値及び前記第2ビット幅の数値とを前記命令発行制御手段に対して提供し、前記浮動小数点演算回路において演算した演算結果を一時記憶する主記憶手段と、

データの入出力を制御する入出力制御手段を介して前記命令発行制御手段に接続されて、前記浮動小数点演算回路において演算した演算結果を保存する外部記憶手段とを有することを特徴とする付記10乃至12のいずれか1項に記載のコンピュータ。

(付記14)

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御方法であって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、

を含むことを特徴とする演算制御方法。

(付記15)

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御プログラムであって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、をコンピュータに実行させることを特徴とする演算制御プログラム。

【特許請求の範囲】

【請求項1】

第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、

演算命令に基づいて、前記第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定手段と、

前記休止判定手段が前記第1演算回路が休止すると判定した場合に、前記第1演算回路を前記第2ビット幅の数値の演算を行なうよう制御し、前記第2ビット幅の数値の演算を、前記第1演算回路と前記第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御手段と、

を備えることを特徴とする浮動小数点演算回路。

【請求項2】

前記第1演算回路は、

前記第1演算回路への演算命令が、前記第1ビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合は、前記第1ビット幅の数値に対して浮動小数点演算を実行し、前記演算判定手段が前記第1ビット幅の数値に対する演算でないと判定した場合は、前記第2ビット幅の数値に対して浮動小数点演算を実行する演算実行手段と、

を有することを特徴とする請求項1に記載の浮動小数点演算回路。

【請求項3】

前記演算判定手段は、

演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて前記第1演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記第1演算回路を休止するか否かの前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記第1ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記第2ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から得た浮動小数点演算結果を格納する演算結果格納レジスタと、を有することを特徴とする請求項1または2に記載の浮動小数点演算回路。

【請求項4】

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

当該浮動小数点演算回路への演算命令が、拡張されたビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が拡張されたビット幅の数値に対する演算であると判定した場合は、前記拡張されたビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が拡張されたビット幅の数値に対する演算でないと判定した場合は、前記拡張されたビット幅より短いビット幅の数値の浮動小数点演算を実行する演算実行手段と、

を備えることを特徴とする浮動小数点演算回路。

【請求項5】

前記演算判定手段は、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記拡張されたビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記拡張されたビット幅より短いビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から浮動小数点演算結果を格納する演算結果格納レジスタと、

を有することを特徴とする請求項4に記載の浮動小数点演算回路。

【請求項6】

前記浮動小数点演算回路が行なう演算が、加算又は減算である場合に、

前記演算実行手段は、

前記演算実行中フラグに基づいて指数のデータ幅に合った指数を選択する基準指数選択回路と、

前記演算実行中フラグに基づいて指数の差を求めて桁合わせ右シフト量を求めるシフト量算出回路と、

第1データの仮数が格納される第1レジスタと、

第2データの仮数が格納される第2レジスタと、

前記第1データの仮数及び前記第2データの仮数のうち、前記演算実行中フラグに基づいて指数の小さい方を桁合わせが必要な仮数として出力し、他方を桁合わせが必要ない仮数として出力する仮数選択回路と、

前記仮数選択回路から出力された桁合わせが必要な仮数を、前記第1データの仮数及び前記第2データの前記演算実行中フラグに基づく指数の差に応じたシフト量だけ右シフトして、シフトした結果を出力する桁合わせ右シフト回路と、

前記桁合わせ右シフト回路から出力される前記桁合わせが必要な仮数のシフトした結果と前記仮数選択回路から出力される桁合わせが必要ない仮数との加減算を行って、加減算結果を出力する加減算回路と、

前記加減算回路から出力された前記加減算結果を正規化する正規化左シフト回路と、

を備えることを特徴とする請求項5に記載の浮動小数点演算回路。

【請求項7】

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止するか否かを検出して、演算実行中フラグを生成する演算実行中フラグ生成回路と、

前記演算実行中フラグ生成回路が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、

入力される拡張されたビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第1レジスタ群と、

入力される拡張されないビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第2レジスタ群と、

前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を実行することを示す場合には前記第1レジスタ群を選択し、前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止することを示す場合には前記第2レジスタ群を選択する符号、指数及び仮数選択回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、演算結果の符号を生成する符号生成回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、被演算データの指数と演算データの指数とを調整して演算結果の指数を生成する指数生成回路と、

前記指数生成回路における前記被演算データの指数と演算データの指数との調整に対応して、被演算データの仮数と演算データの仮数との桁合わせを行なって演算結果の仮数を生成する仮数演算回路と、

前記演算結果の指数と仮数とを整合する整合回路と、

前記演算結果の符号と、前記整合回路で整合された前記演算結果の指数と仮数とを格納する演算結果格納レジスタとを備え、

前記実行中フラグ格納レジスタに格納された前記実行中フラグと、前記演算結果格納レジスタに格納された前記演算結果の符号、指数及び仮数とを、浮動小数点演算結果として出力することを特徴とする浮動小数点演算回路。

【請求項8】

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータであって、

第1演算回路が、

当該第1演算回路への演算命令が、第1ビット幅の数値に対する演算であるか前記第1ビット幅より短い第2ビット幅の数値に対する演算であるかを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合に、前記第1ビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が前記第2ビット幅の数値に対する演算であると判定した場合に、前記第2ビット幅の数値の浮動小数点演算を実行する演算実行手段と、を有し、

第2演算回路が、前記第2ビット幅の数値の浮動小数点演算を実行する回路であって、

前記浮動小数点演算回路への演算命令が前記第1ビット幅の数値に対する演算が休止することを示す場合には、前記第2ビット幅の数値の浮動小数点演算を前記第1演算回路と前記第2演算回路とにより並列に実行することを特徴とするコンピュータ。

【請求項9】

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御方法であって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、

を含むことを特徴とする演算制御方法。

【請求項10】

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御プログラムであって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、

前記浮動小数点演算回路において演算すべき数値が第2ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路と前記第2ビット幅の演算を行なう第2演算回路とに並列の前記第2ビット幅の演算命令と演算すべき数値とを提供して、前記第2ビット幅の演算結果を前記第1演算回路と前記第2演算回路から並列に取得する第2演算ステップと、をコンピュータに実行させることを特徴とする演算制御プログラム。

【請求項1】

第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、

演算命令に基づいて、前記第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定手段と、

前記休止判定手段が前記第1演算回路が休止すると判定した場合に、前記第1演算回路を前記第2ビット幅の数値の演算を行なうよう制御し、前記第2ビット幅の数値の演算を、前記第1演算回路と前記第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御手段と、

を備えることを特徴とする浮動小数点演算回路。

【請求項2】

前記第1演算回路は、

前記第1演算回路への演算命令が、前記第1ビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合は、前記第1ビット幅の数値に対して浮動小数点演算を実行し、前記演算判定手段が前記第1ビット幅の数値に対する演算でないと判定した場合は、前記第2ビット幅の数値に対して浮動小数点演算を実行する演算実行手段と、

を有することを特徴とする請求項1に記載の浮動小数点演算回路。

【請求項3】

前記演算判定手段は、

演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて前記第1演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記第1演算回路を休止するか否かの前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記第1ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記第2ビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から得た浮動小数点演算結果を格納する演算結果格納レジスタと、を有することを特徴とする請求項1または2に記載の浮動小数点演算回路。

【請求項4】

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

当該浮動小数点演算回路への演算命令が、拡張されたビット幅の数値に対する演算であるか否かを判定する演算判定手段と、

前記演算判定手段が拡張されたビット幅の数値に対する演算であると判定した場合は、前記拡張されたビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が拡張されたビット幅の数値に対する演算でないと判定した場合は、前記拡張されたビット幅より短いビット幅の数値の浮動小数点演算を実行する演算実行手段と、

を備えることを特徴とする浮動小数点演算回路。

【請求項5】

前記演算判定手段は、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路を休止するか否かを検出して演算実行中フラグを生成する演算実行中フラグ生成手段と、

前記演算実行中フラグ生成手段が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、を有し、

前記演算実行手段は、

前記演算実行中フラグが演算実行中であることを示す場合に、前記拡張されたビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達し、前記演算実行中フラグが演算実行中でないことを示す場合に、前記拡張されたビット幅より短いビット幅の数値に含まれる符号、指数及び仮数を選択して浮動小数点演算を実現する回路群に伝達する選択手段と、

前記浮動小数点演算を実現する回路群から浮動小数点演算結果を格納する演算結果格納レジスタと、

を有することを特徴とする請求項4に記載の浮動小数点演算回路。

【請求項6】

前記浮動小数点演算回路が行なう演算が、加算又は減算である場合に、

前記演算実行手段は、

前記演算実行中フラグに基づいて指数のデータ幅に合った指数を選択する基準指数選択回路と、

前記演算実行中フラグに基づいて指数の差を求めて桁合わせ右シフト量を求めるシフト量算出回路と、

第1データの仮数が格納される第1レジスタと、

第2データの仮数が格納される第2レジスタと、

前記第1データの仮数及び前記第2データの仮数のうち、前記演算実行中フラグに基づいて指数の小さい方を桁合わせが必要な仮数として出力し、他方を桁合わせが必要ない仮数として出力する仮数選択回路と、

前記仮数選択回路から出力された桁合わせが必要な仮数を、前記第1データの仮数及び前記第2データの前記演算実行中フラグに基づく指数の差に応じたシフト量だけ右シフトして、シフトした結果を出力する桁合わせ右シフト回路と、

前記桁合わせ右シフト回路から出力される前記桁合わせが必要な仮数のシフトした結果と前記仮数選択回路から出力される桁合わせが必要ない仮数との加減算を行って、加減算結果を出力する加減算回路と、

前記加減算回路から出力された前記加減算結果を正規化する正規化左シフト回路と、

を備えることを特徴とする請求項5に記載の浮動小数点演算回路。

【請求項7】

拡張されたビット幅の数値の浮動小数点演算を行なう浮動小数点演算回路であって、

入力される演算命令を格納する演算命令レジスタと、

前記演算命令レジスタの出力信号の値に基づいて当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止するか否かを検出して、演算実行中フラグを生成する演算実行中フラグ生成回路と、

前記演算実行中フラグ生成回路が生成した前記演算実行中フラグを格納する実行中フラグ格納レジスタと、

入力される拡張されたビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第1レジスタ群と、

入力される拡張されないビット幅の被演算データの符号、指数及び仮数と演算データの符号、指数及び仮数とを格納する第2レジスタ群と、

前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を実行することを示す場合には前記第1レジスタ群を選択し、前記演算実行中フラグが当該浮動小数点演算回路による拡張されたビット幅の浮動小数点演算を休止することを示す場合には前記第2レジスタ群を選択する符号、指数及び仮数選択回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、演算結果の符号を生成する符号生成回路と、

演算命令と被演算データの符号と演算データの符号とに基づいて、被演算データの指数と演算データの指数とを調整して演算結果の指数を生成する指数生成回路と、

前記指数生成回路における前記被演算データの指数と演算データの指数との調整に対応して、被演算データの仮数と演算データの仮数との桁合わせを行なって演算結果の仮数を生成する仮数演算回路と、

前記演算結果の指数と仮数とを整合する整合回路と、

前記演算結果の符号と、前記整合回路で整合された前記演算結果の指数と仮数とを格納する演算結果格納レジスタとを備え、

前記実行中フラグ格納レジスタに格納された前記実行中フラグと、前記演算結果格納レジスタに格納された前記演算結果の符号、指数及び仮数とを、浮動小数点演算結果として出力することを特徴とする浮動小数点演算回路。

【請求項8】

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータであって、

第1演算回路が、

当該第1演算回路への演算命令が、第1ビット幅の数値に対する演算であるか前記第1ビット幅より短い第2ビット幅の数値に対する演算であるかを判定する演算判定手段と、

前記演算判定手段が前記第1ビット幅の数値に対する演算であると判定した場合に、前記第1ビット幅の数値の浮動小数点演算を実行し、前記演算判定手段が前記第2ビット幅の数値に対する演算であると判定した場合に、前記第2ビット幅の数値の浮動小数点演算を実行する演算実行手段と、を有し、

第2演算回路が、前記第2ビット幅の数値の浮動小数点演算を実行する回路であって、

前記浮動小数点演算回路への演算命令が前記第1ビット幅の数値に対する演算が休止することを示す場合には、前記第2ビット幅の数値の浮動小数点演算を前記第1演算回路と前記第2演算回路とにより並列に実行することを特徴とするコンピュータ。

【請求項9】

異なるビット幅の数値に対してそれぞれ浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路を備えたコンピュータの演算制御方法であって、

演算プログラムを記憶手段から読み出す読出ステップと、

前記演算プログラムの命令を解析して、前記浮動小数点演算回路において演算すべき数値が第1ビット幅か前記第1ビット幅より短い第2ビット幅かを判定する判定ステップと、

前記浮動小数点演算回路において演算すべき数値が第1ビット幅の場合に、前記第1ビット幅の演算を行なう第1演算回路に前記第1ビット幅の演算命令と演算すべき数値とを提供して、前記第1ビット幅の演算結果を前記第1演算回路から取得する第1演算ステップと、