Fターム[5B016CD01]の内容

位取り記数法を用いた四則演算 (704) | 小数点 (33) | 浮動小数点 (33)

Fターム[5B016CD01]に分類される特許

1 - 20 / 33

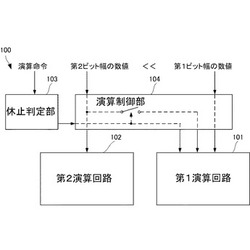

浮動小数点演算回路、浮動小数点演算回路を備えたコンピュータ及びその演算制御方法と演算制御プログラム

【課題】拡張精度演算回路と単・倍精度演算回路とにより単精度同士/倍精度同士の並列演算を実現し、演算処理を高速化して演算実行時間を短縮できること。

【解決手段】第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、演算命令に基づいて、第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定部と、休止判定部が前記第1演算回路が休止すると判定した場合に、第1演算回路を第2ビット幅の数値の演算を行なうよう制御し、第2ビット幅の数値の演算を、第1演算回路と第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御部と、を備えることを特徴とする。

(もっと読む)

車載制御装置

【課題】浮動小数点形式のデータの演算結果が非数となった場合でも、当該制御および他の制御における制御不良を防止する。

【解決手段】CPUは、吸気制御初期化処理(ステップS1301)において、非数が発生した変数を初期化するとともに、同変数を参照して算出される変数など、非数が発生した変数によって影響を受ける変数を一括して初期化する。本処理で初期化する変数は、必ずしも吸気制御処理内で用いられる全ての変数でなくともよい。非数が発生した変数によって影響を受ける変数、例えばある変数が非数となると派生的に非数となる変数などを初期化することもできる。その他の任意の変数を初期化対象としてもよい。

(もっと読む)

浮動小数点除算器、及びそれを用いた情報処理装置

【課題】演算TATを短縮して、性能向上と消費電力低減効果を実現できる浮動小数点除算器を提供する。

【解決手段】浮動小数点除算器は、2進数の減算シフト型である。この浮動小数点除算器は、仮数繰り返し処理部250と、演算実行制御部200とを具備する。仮数繰り返し処理部250は、入力オペランドにおける被除数の仮数の減算シフト処理により商と部分剰余とを生成する。演算実行制御部200は、部分剰余に関して、演算実行処理における基数によって一意に決定される特定の位置のビット値を判定する。仮数繰り返し処理部250は、演算実行制御部200の判定結果に基づいて、減算シフト処理の1回につき生成される商のビット数と部分剰余の左シフトビット数に対して、それぞれ2倍の商生成及び部分剰余の左シフト処理を行うことで、減算シフト処理回数を削減する。

(もっと読む)

積和演算装置及び積和演算装置の制御方法

【課題】積和演算処理と、異なる命令の加算処理と乗算処理との並列実行処理とを切り替えることができる積和演算装置及び積和演算装置の制御方法を提供すること。

【解決手段】本発明にかかる積和演算装置は、入力された第1及び第2のオペランドを乗算する乗算処理と、外部からの積和演算の有無を示す指示に応じて、入力された第3のオペランドを用いた所定の演算処理とを行う演算部と、演算部の処理結果を出力する出力部とを備え、演算部は、指示が積和演算有を示す場合に、乗算処理による乗算結果に第3のオペランドを加算して積和演算結果を求める積和演算処理と、指示が積和演算無を示す場合に、さらに入力された第4のオペランドに第3のオペランドを加算して加算結果を求める加算処理とを行い、出力部は、演算部により積和演算処理が行われた場合に、積和演算結果を出力し、演算部により加算処理が行われた場合に、乗算結果及び加算結果を出力する。

(もっと読む)

演算装置及び演算方法

【課題】 浮動小数点積和演算あるいは固定小数点乗算がそれぞれ実行される場合に、無効な電力消費が発生するという問題点がある。

【解決手段】 通知された演算命令に基づいて選択した入力データを構成する複数の部分データそれぞれについて最上位ビットから連続している0の数を計数して第1のリーディングゼロカウントとし、第1のリーディングゼロカウントに基づいて入力データについて最上位ビットから連続している0の数を計数して第2のリーディングゼロカウントを出力するリーディングゼロ手段と、第1のリーディングゼロカウントを入力して演算命令に基づいた演算を行うとともに、第2のリーディングゼロカウントを入力して演算命令に基づいた演算を行う第1の演算手段と、第1の演算手段及びリーディングゼロ手段と連携して演算命令に基づいた演算を行う第2の演算手段とを有する。

(もっと読む)

浮動小数点演算を用いた組込み制御装置

【課題】バックアップメモリに格納する浮動小数点数形式のデータの非数の有無の判定及び初期化を、演算負荷を増加させることなく実行できる組込み制御装置を提供する。

【解決手段】マイクロコンピュータへの動作電源遮断時、組込み制御装置は、バックアップメモリに格納する浮動小数点数形式のデータの非数の有無を判定し、非数を有すると判定した場合、非数を有する浮動小数点数形式のデータを初期化する。マイクロコンピュータへの動作電源投入時、組込み制御装置は、動作電源遮断時にバックアップメモリに格納した浮動小数点数形式のデータのサム値と、動作電源遮断時にバックアップメモリに格納した浮動小数点数形式のデータのサム値とを比較することにより非数の有無を判定し、非数を有すると判定したとき、非数を有する浮動小数点数形式のデータを初期化する。

(もっと読む)

ベクトル乗算処理装置および方法ならびにプログラム

【課題】オペランドのシフトを要することなく消費電力の削減をはかる。

【解決手段】高速化回路(固定小数点オーバーフロー先見回路5、スティッキービット先見回路6)を備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、高速化回路を使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路4(部分積生成回路41、部分積制御回路42)、を備える。

(もっと読む)

演算装置、演算方法及び演算プログラム

【課題】浮動小数点演算でアンダーフロー例外及びオーバーフロー例外が発生した場合に消費電力を抑えることができる演算装置を提供する。

【解決手段】指数演算手段81は、浮動小数点数の指数に対して演算を行う。仮数演算手段82は、浮動小数点数の仮数に対して演算を行う。演算例外検知手段83は、指数演算手段81が演算を実行したときに、その演算結果がオーバーフロー又はアンダーフローを示す演算例外であることを検知する。演算停止手段84は、演算例外検知手段83が演算例外を検知したときに、仮数演算手段82の演算を停止させる。

(もっと読む)

SIMD演算器、SIMD演算器の演算方法、演算処理装置及びコンパイラ

【課題】Dekkerの方法をSIMD方式の演算において高速に実行すること。

【解決手段】演算処理装置は、加算誤差を使用するプログラムをコンパイルするコンパイラと、コンパイラからの複数の命令を格納する記憶手段と、記憶手段から読み出した命令に基づき、複数の演算を単一の命令(SIMD)で実行する演算器とを有し、演算器は、複数のレジスタからなる第1のレジスタ群及び第2のレジスタ群を有するSIMD用レジスタと、第1のレジスタ群及び第2のレジスタ群から入力される2つの入力値をSIMD方式に基づいて演算する演算手段とを有し、演算手段は、2つの入力値の絶対値を比較し、絶対値の大きい値又は等しい値を第1の値として出力する第1の演算手段と、2つの入力値の絶対値を比較し、絶対値の小さい値又は等しい値を第2の値として出力する第2の演算手段と、第1の値及び第2の値を使用した加減算を実行する第3の演算手段とを有する。

(もっと読む)

計算機

【課題】SIMD型計算機やベクトル型計算機に適用可能な、特定の初期値を検出して別処理を行うことを不要とする、ソフトウェアシーケンスによる高性能な除算を実行する。

【解決手段】符号および仮数と、指数とを分解し、2者を別々に計算する除算用の計算機において、符号および仮数を取り出す演算器と、2つの数の指数の差を取り出す演算器を設ける。

(もっと読む)

浮動小数点実行ユニットを用いる回路装置、集積回路装置、プログラム製品、および方法(動的値域調整浮動小数点実行ユニット)

【課題】浮動小数点実行ユニットを提供する。

【解決手段】浮動小数点実行ユニットは、浮動小数点計算のために拡張された値域を動的に提供するために浮動小数点値の仮数ビットの部分集合を付加的な指数ビットして選択的に再利用することができる。浮動小数点オペランドの仮数フィールドは第1および第2部分を含むと考えられることができ、その第1部分は、浮動小数点値の仮数を表すように第2部分と連結されることができ、あるいは、拡張された値域を提供するために、浮動小数点値の指数を表すように浮動小数点オペランドの指数フィールドと連結されることができる。

(もっと読む)

SIMD演算器、SIMD演算器の演算方法、演算処理装置及びコンパイラ

【課題】Dekkerの方法をSIMD演算器を用いて高速に実行することを可能とする。

【解決手段】演算処理装置10は、加算誤差を使用するプログラム1をコンパイルするコンパイラ2と、コンパイラ2からの複数の命令を格納する主記憶部4と、主記憶部4から読み出した命令に基づき、複数の演算を一の命令で実行するシングル命令マルチデータ(SIMD)方法の演算で計算誤差を求めるSIMD命令実行部6を有する。SIMD命令実行部6は、複数のレジスタからなる第1のレジスタ群171及び第2のレジスタ群172を有するSIMD用レジスタ177と、第1のレジスタ群171及び第2のレジスタ群172から入力される2つの入力の絶対値を比較する処理をSIMD方式で実行し、絶対値の大きい方を第1の値、小さい方を第2の値とする演算部18とを有し、演算部18は、第1の値及び第2の値を使用した加減算をSIMD方式で実行する。

(もっと読む)

浮動小数点演算装置

【課題】本発明は、従来の浮動小数点積和演算を可能としながら、2つの浮動小数点A、Bの加算(A+B)及び減算(A-B)を並列処理する事ができる浮動小数点演算装置を提供する。

【解決手段】本発明は、2つの浮動小数点A、Bに対する加算(A+B)及び減算(A-B)を並列実行するために、従来の浮動小数点積和演算器(FMA)に加え、浮動小数点加算器を一つ備え、加算(A+B)または減算(A-B)のうちで、いずれかが2ビット以上の左シフト正規化が必要であるかを判定する手段を有し、加算(A+B)または減算(A-B)のうちで、2ビット以上の左シフト正規化が必要でない方の正規化論理を省く事で、性能を2倍に向上し回路規模は2倍未満に抑える。

(もっと読む)

浮動小数点演算のための再構成アレイプロセッサ

【課題】既存の整数演算用PEを利用している従来の再構成アレイプロセッサとほぼ類似したハードウェアのサイズを有しつつも、浮動小数点演算(floating point operation)を比較的速く行うことができ、低電力であり、かつ性能対価格の高特性を有する再構成アレイ(reconfigurable array)プロセッサ、及びそのプロセッサを含んだマルチメディア・プラットホームである。

【解決手段】浮動小数点演算を行うためのプロセッサは浮動小数点演算を行うことができるように配されたプロセッシング要素アレイを含む。各プロセッシング要素は、2つの入力値を受け、入力値に対する整数演算を行う演算装置を含む。該アレイ内のプロセッシング要素は、浮動小数点演算のために、2つ以上のグループに共に連結される。

(もっと読む)

自明な算術演算を利用するプロセッサ

【課題】本出願はプロセッサ分野、特に算術演算の実行に関する。

【解決手段】プロセッサによって実行される計算の多くは、多数の単純な演算を含む。その結果、乗算演算は、非常に多数のクロックサイクルをかけて終了する場合がある。本出願は、自明なオペランド・レジスタを有するプロセッサを提供し、これはデータストアに格納されるデータ値に対する算数又は格納演算の実行に使用される。

(もっと読む)

演算回路及び演算方法並びに情報処理装置

【課題】より少ない回路量で数値的に大きな誤差をもつエラーを効率的に検出する浮動小数点演算回路を提供する。

【解決手段】上記課題を解決するために、浮動小数点演算回路に、第1の演算結果を出力する第1の演算器101と、第2の演算結果を出力する第2の演算器102と、第1の演算結果と第2の演算結果とについて所定ビット幅の比較を行う比較回路103と、を備える。

(もっと読む)

3項入力の浮動小数点加減算器

【課題】演算過程で無限の精度をもって演算した後丸めを行った場合と同一の結果を得ることができる3項入力の浮動小数点加減算器を提供する。

【解決手段】入力される3項の指数の大きさが最大の仮数、中間の仮数、最小の仮数に振り分け、指数の大きさが中間の仮数と最小の仮数とをそれぞれ2n+3ビット幅で右シフトして桁合わせを行った仮数と最大の仮数とを出力する前処理回路100と、前処理回路100からの3項の仮数を2項に減らす桁上げ保存加算器(CSA)101と、2項になった仮数の加算を行う桁上げ先見加算器(CLA)102と、最上位ビットが1になるように左シフトする正規化回路103と、上位からn+3ビット目を新たなStickyビットとし、それより下位のビットとの論理和を取って丸めを行う丸め処理回路104と、最終的な指数を出力する指数演算器100とを備える。

(もっと読む)

命令に応じた丸め処理の実行

ある実施形態では、本発明は、プロセッサにおいて丸め命令および直接値を受領し、前記直接値の丸めモード・オーバーライド指標がアクティブであるかどうかを判定し、もしアクティブであれば、前記丸め命令に応答して、前記直接オペランドに記述されている丸めモードに従って前記プロセッサの浮動小数点ユニットにおいてソース・オペランドに対して丸め処理を実行することを含む方法を含む。他の実施形態も記載され、特許請求される。  (もっと読む)

(もっと読む)

マルチステージ浮動小数点アキュームレータ

マルチステージ浮動小数点アキュームレータは、少なくとも2つのステージを有し、より速い速度で動作することができる。ある設計では、浮動小数点アキュームレータは、第1及び第2のステージを有する。第1のステージは、3つのオペランドアライメントユニット、2つの乗算器及び3つのラッチを有する。3つのオペランドアライメントユニットは、現在の浮動小数点値、以前の浮動小数点値及び以前の累積値で動作する。第1の乗算器は、ゼロ或いは以前の浮動小数点値を第2のオペランドアライメントユニットに供給する。第2の乗算器は、ゼロ或いは以前の以前の累積値を第3のオペランドアライメントユニットに供給する。3つのラッチは3つのオペランドアライメントユニットに接続している。第2のステージは、3つのオペランドアライメントユニット、ラッチ及びポストアライメントユニットによって生成されたオペランドを加算する3−オペランド加算器を有する。  (もっと読む)

(もっと読む)

非正規化オペランドのためのモードベース乗算−加算プロセッサ

非正規化サポートモードでは、浮動小数点加算器の正規化回路は、浮動小数点乗算器の出力を正規化、あるいは、非正規化するために使用される。各浮動小数点乗算命令は、強制的にゼロにされる加数で、乗算−加算命令へ推論的に変換される。浮動小数点加算器の正規化回路を利用して積を正規化、あるいは、非正規化する一方で、これは積の値を保存する。乗算処理のオペランドが利用可能である場合、それらは検査される。オペランドがアンノーマル中間積、あるいは、非正規化最終積を生成しない場合には、たとえば、オペランド・フォワーディングによって、その加算演算は抑制される。さらに、各融合なしの浮動小数点乗算−加算命令は、ゼロの加数を持つ乗算−加算命令で置き換えられる。そして、元の乗算−加算命令の加数を持つ浮動小数点加算命令は、命令ストリームに挿入される。演算の検査に応じて、アンノーマル中間結果、あるいは、非正規化最終結果が生じない場合には、その加数は乗算−加算命令に戻され、そして加算命令はNOPに変換される。  (もっと読む)

(もっと読む)

1 - 20 / 33

[ Back to top ]