Fターム[5B022AA03]の内容

Fターム[5B022AA03]に分類される特許

1 - 11 / 11

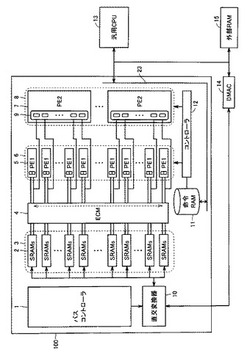

データ処理装置およびそのデータ処理方法

【課題】可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能なデータ処理装置を提供すること。

【解決手段】データ処理装置100は、SIMD方式の複数のPE1(5)と、複数のPE1(5)のそれぞれに対応して設けられる複数のSRAMs2と、複数のPE2(7)とを含む。複数のPE1(5)のそれぞれは、対応する1つのSRAMs2に格納されるデータに対して演算を行なう。また、複数のPE2(7)のそれぞれは、対応する複数個のSRAMs2に格納されるデータに対して演算を行なう。したがって、複数のSRAMs2を共有することができ、可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能となる。

(もっと読む)

浮動小数点演算回路、浮動小数点演算回路を備えたコンピュータ及びその演算制御方法と演算制御プログラム

【課題】拡張精度演算回路と単・倍精度演算回路とにより単精度同士/倍精度同士の並列演算を実現し、演算処理を高速化して演算実行時間を短縮できること。

【解決手段】第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、演算命令に基づいて、第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定部と、休止判定部が前記第1演算回路が休止すると判定した場合に、第1演算回路を第2ビット幅の数値の演算を行なうよう制御し、第2ビット幅の数値の演算を、第1演算回路と第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御部と、を備えることを特徴とする。

(もっと読む)

プロセッサおよびそれを用いた画像処理システム

【課題】演算結果の信頼性と並列度との最適化を図ることが可能なプロセッサを提供すること。

【解決手段】通常モードが設定されている場合に、PE群11〜26のデータレジスタに別個の演算対象のデータが書き込まれ、エラー検出モードが設定されている場合に、PE群11〜18のデータレジスタと、PE群19〜26のデータレジスタとに同じ演算対象のデータが書き込まれる。通常モードが設定されている場合に、マルチプレクサ40〜42が、PE群11〜26から出力される演算結果を別個の演算結果として選択的に出力し、エラー検出モードが設定されている場合に、判定回路43がPE群11〜18と、PE群19〜26とから出力される演算結果を比較し、一致するときにマルチプレクサ40〜42がその演算結果を出力し、一致しないときに判定回路43が外部にエラー検出を通知する。したがって、演算結果の信頼性と並列度との最適化を図ることが可能となる。

(もっと読む)

算術演算のためにマグニチュード検出を実行するための装置および方法

処理回路と、1つまたは複数のレジスタと、制御回路とを備える装置および方法が提供される。この制御回路は、結合マグニチュード検出算術命令に応答して、少なくとも1つのデータエレメント上で算術演算を実行するように、さらに、マグニチュード検出演算を実行するように、処理回路を制御するように構成される。マグニチュード検出演算は、算術演算のマグニチュードの最上位ビットのポジションが、少なくとも1つのデータエレメントのデータエレメント幅を超えるかどうかにかかわらず、最上位ビットのポジションを表示するマグニチュード表示結果を計算する。  (もっと読む)

(もっと読む)

浮動小数点演算のための再構成アレイプロセッサ

【課題】既存の整数演算用PEを利用している従来の再構成アレイプロセッサとほぼ類似したハードウェアのサイズを有しつつも、浮動小数点演算(floating point operation)を比較的速く行うことができ、低電力であり、かつ性能対価格の高特性を有する再構成アレイ(reconfigurable array)プロセッサ、及びそのプロセッサを含んだマルチメディア・プラットホームである。

【解決手段】浮動小数点演算を行うためのプロセッサは浮動小数点演算を行うことができるように配されたプロセッシング要素アレイを含む。各プロセッシング要素は、2つの入力値を受け、入力値に対する整数演算を行う演算装置を含む。該アレイ内のプロセッシング要素は、浮動小数点演算のために、2つ以上のグループに共に連結される。

(もっと読む)

信号処理

【課題】信号を処理する方法を提供すること。

【解決手段】信号データ値および畳み込みフィルタ係数値を、畳み込み値を計算するために使用される一組のプロセッサ(cutil)中の対象プロセッサ(ct)にロードするためのプロセス。係数値はcutilにマッピング(150)される。データ値と係数値のインターリーブ(160)がctについて決定される。係数値がctにロードされ、データ値がctにロードされ、それによって畳み込み値の計算(170)に参加するようctを準備する。

(もっと読む)

アレイ型プロセッサ

【課題】パスの構成の変更に伴って生じるグリッチの発生及び伝播を低減して、消費電力を削減する。

【解決手段】複数のプロセッサエレメントを備え、プロセッサエレメント間のデータ送受に係るパスの構成をクロックサイクル毎に変更することが可能なアレイ型プロセッサであって、各プロセッサエレメントは、パスの構成に係る構成情報指示信号を記憶する構成情報メモリ11と、クロックサイクル毎に構成情報メモリ11から出力される構成情報指示信号Pinのタイミングを調整する遅延調整回路12と、タイミングが調整された構成情報指示信号Poutに基づいて他のプロセッサエレメント(PE)または機能ユニット(レジスタファイルユニット14および演算器15)とのパスを変更する配線接続回路13と、を備える。

(もっと読む)

SIMD演算処理装置及び並列演算方法

【課題】演算処理に要する時間を短縮することでスループットを向上させる。

【解決手段】SIMD演算処理装置は、2つの単位プロセッサ演算ブロックX,Yを備える。制御部1は、プログラムメモリ2に格納される汎用関数を読み出して演算ブロックX,Yに設定する。これと共に、制御部1は、データメモリ3に格納される引数1(0),引数2(0),引数3(0)を演算ブロックXに,引数1(1),引数2(1),引数3(1)を演算ブロックYにそれぞれ供給する。演算ブロックX,Yは、上記汎用関数に基づいて上記供給されたデータに対する演算を並列に実行する。

(もっと読む)

回路および回路接続方法

【課題】閉塞ネットワークを利用した回路において、従来よりも多くのアプリケーションを実装する。

【解決手段】入力されるデジタルデータに対して数値演算または論理演算を実行し、数値演算または論理演算の出力信号を出力する、そのような1以上の演算素子と、前記の演算素子の入力側に接続されるネットワーク出力端子と、前記演算素子の出力信号または前記演算素子の出力信号以外の外部信号が入力されるネットワーク入力端子と、前記入力端子を出力端子に接続するネットワーク部と備え、ネットワーク出力端子のうちの2つのネットワーク出力端子が同時に接続することができないネットワーク入力端子の組に含まれるネットワーク入力端子数として定義される制約強度について、同一の演算素子に入力される複数の出力端子間の制約強度が最小となるように、前記演算素子とネットワーク出力端子とを接続した。

(もっと読む)

演算装置

【課題】用途に応じて高い自由度をもってデータフロー型の演算を行うことが可能で、高速な演算処理を実現することが可能な演算装置を提供する。

【解決手段】演算装置1は、各演算器OP1〜OP16の各々が、複数の入力ポートおよび複数の出力ポートを含み、各入力ポートが演算データの入力ラインまたは前段の演算器の出力ポートに接続され、入力ポートから入力した演算データに対する演算結果が、出力ポートを通して後段に位置する演算器に順次流れていくようなデータフローを形成するように構成されている。

(もっと読む)

データ処理システムとその方法

【課題】ファジー論理,ニューラル・ネットワークやその他の並行なアレイ準拠アプリケーションに関しては、ベクタ命令およびスケーラ命令の両方に関してデータのコヒーレンシを確認するデータ・コヒーレンシ技術およびメカニズムが必要になり、それにはソフトウェア経費が最小限で済み、最小限の回路構成を用いて実現できることが必要とされる。

【解決手段】

データ処理システムおよびその方法は、1つ以上のデータ・プロセッサを含む。データ・プロセッサは、ベクトル動作とスカラー動作の両方を行うことができる。1台のマイクロシーケンサ22を用いて、データ・プロセッサ10はベクトル命令とスカラー命令の両方を実行することができる。またデータ・プロセッサはベクトル・オペランドとスカラー・オペランドの両方を記憶することのできるメモリ回路を有する。

(もっと読む)

1 - 11 / 11

[ Back to top ]