Fターム[5B018KA18]の内容

記憶装置の信頼性向上技術 (13,264) | エラー処理 (1,086) | 障害回復 (704) | 領域単位の切替え (112)

Fターム[5B018KA18]に分類される特許

1 - 20 / 112

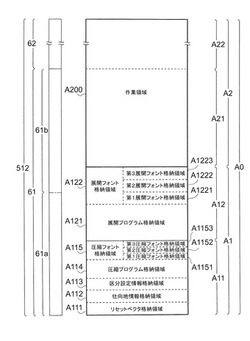

情報処理装置、画像形成装置およびプログラム

【課題】プログラムの誤動作の発生を抑制する。

【解決手段】動作制御部は、プログラムを実行するCPUと、プログラムを格納するとともにプログラムの実行に伴って発生するデータを格納するメインメモリ512とを有している。メインメモリ512は、読み書き可能であって、電源を供給しなくても、記憶している情報を保持することが可能なMRAM61と、電源を供給しないと、記憶している情報を保持することができないDRAM62とを備えており、MRAM61の一部領域にはプログラム等が格納されるROM領域A1が設けられ、MRAM61の残りの領域およびDRAM62のすべての領域にはデータ等が格納されるRAM領域A2が設けられる。CPUがリセットされると、ROM領域A1の記憶内容をそのままとする一方でRAM領域A2の記憶内容を消去し、ROM領域A1から読み出したプログラムを実行する。

(もっと読む)

自動車用電子制御装置

【課題】不揮発性メモリの記憶領域に故障が発生しても、情報の蓄積に支障がないようにする。

【解決手段】イグニッションスイッチがOFFになったことを契機として、不揮発性メモリに故障情報を書き込むときに、故障が発生していない記憶領域を選定し(S1)、記憶領域の全領域に消去データを書き込み(S2,S3)、消去データの確認により消去できたか否かを判定する(S4,S5)。記憶領域が消去できなかった場合、故障が発生していない他の記憶領域に素子異常情報を書き込む(S16)。また、イグニッションスイッチがONになったことを契機として、不揮発性メモリから故障情報を読み込むときに、チェックサムを利用して異常を検知し、故障が発生していない他の記憶領域に素子異常情報を書き込む。そして、素子異常情報を計数した計数値が所定の閾値以上である記憶領域は、故障が発生していると判定し、その使用を禁止する。

(もっと読む)

メモリシステム

【課題】フラッシュメモリに記録されたデータの信頼性を向上させることができる技術を提供することを課題とする。

【解決手段】メモリ4,6は、NANDフラッシュメモリである。メモリコントローラ3は、ホストシステム1の要求に応じてメモリ4からデータ45Mを読み出し、データ45Mをホストシステム1へ出力する。メモリコントローラ5は、バックアップ用のメモリ6の各ブロックに格納されたデータを検査する。メモリコントローラ5は、メモリ6のページの中から検査対象のブロックを決定し、検査対象のブロックからデータ45Cを読み出す。ECC回路51は、データ45Cのエラーを検出する。データ45Cからエラーが検出された場合、エラー訂正されたデータ45Cが、検査対象のブロックに書き戻される。メモリコントローラ3は、所定の切り替え条件が満たされた場合、アクセス対象をメモリ4からメモリ6へ切り替える。

(もっと読む)

フラッシュメモリに対してデータの読み出しおよび書き込みを行う制御装置

【課題】記録先のブロック中に順次データを記録していき、当該記録先のブロックがデータで満杯になると、次のブロックのデータを消去して新たな記録先のブロックとし、前回の記録先のブロックのデータのうち、一部の必要なデータを現在の記録先のブロックにコピーし、その後、現在の記録先のブロックに順次データを記録していくというフラッシュメモリの書き込み制御において、ブロックの故障に起因してブロック間のデータのコピー頻度が増大するのを防ぐ。

【解決手段】現在の記録先のブロックが満杯状態になって次のブロックの消去を試みたときに(ステップ150)、消去が失敗したか否かを判定し(ステップ160)、消去に失敗したと判定したことに基づいて、次のブロックが故障したと判定し、使用対象から除外する(ステップ175)。

(もっと読む)

半導体メモリ装置および半導体メモリシステム

【課題】製品寿命の長いメモリカード2を提供する。

【解決手段】実施形態のメモリカード2は、SLC領域22Aと、MLC領域22Bと、を有するメモリ部22と、MLC領域22Bに記憶されたデータの誤りを訂正する誤り訂正部20と、誤り訂正部20が誤りを検出したデータを記憶していた多値メモセルの位置情報をSLC領域22Aに記憶し前記位置情報にもとづき消失訂正を行う消失訂正部21と、を具備する。

(もっと読む)

制御装置、制御モジュールおよび制御方法

【課題】情報管理の信頼性を高めること。

【解決手段】記憶装置2は、データの書き込みが複数回可能な複数のブロックを有する第1の記憶領域2aと、データの書き込みが1回だけ可能な第2の記憶領域2bとを有する。フラグ管理情報作成部1bは、第1の記憶領域2aに記憶されているフラグに基づいて、記憶装置2のブロック毎にデータが記憶可能か否かを示す管理テーブル(フラグ管理情報)1b1を作成する。管理情報制御部1cは、フラグ管理情報作成部1bにより作成された管理テーブル1b1を第2の記憶領域2bに記憶させる。

(もっと読む)

記憶装置

【課題】フラッシュメモリへのデータ書き込みの際に、代替ブロックの残量を的確に通知する。

【解決手段】メモリへのデータの書き込みを制御すると共に、代替ブロックの残量が記憶された閾値情報で指定される閾値以下になると通信手段により外部機器に通知する制御手段を備えた記憶装置において、制御手段は通信手段により外部機器から受信した閾値情報を用いて制御手段が通知のために使用する閾値情報を更新する。

(もっと読む)

不揮発性記憶装置および不揮発性メモリコントローラ

【課題】特に高いデータ保持信頼性が要求される読み出し専用のデータに対し、データ保持信頼性向上のためのリフレッシュ処理が適用された場合に、データ保持信頼性を維持する。

【解決手段】論理アドレスを複数の領域に分割し、分割された領域のデータに対しレベリング処理の適用を許可/禁止を示す領域指定テーブル112と、読み出し専用の物理ブロックのデータのリフレッシュ時に使用する物理ブロックのアドレスを登録した無劣化ブロックテーブル113と、アドレス変換テーブル109と、制御部108とECC回路107を有する不揮発性記憶装置101において、レベリング処理を禁止する領域の読み出し時に、ECC訂正ビット数が所定ビット数以上であることを検出した場合は、無劣化ブロックテーブルの物理ブロックを選択してデータをコピーするリフレッシュ処理を行う。

(もっと読む)

メモリシステム

【課題】高優先書き込みの際のブロック並列度の低下を防止する。

【解決手段】通常優先度でフリーブロックを取得する際に、フリーブロック数が第1の閾値より多く存在するフリーブロック管理リストからフリーブロックを取得するよう動作する第1のフリーブロック選択部と、高優先度でフリーブロックを取得する際に、フリーブロック数が第1の閾値より多く存在するフリーブロック管理リストおよびフリーブロック数が第1の閾値より多く存在しないフリーブロック管理リストからフリーブロックを取得するよう動作する第2のフリーブロック選択部とを備える。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

記録装置、読出装置、および、記録再生装置

【課題】フラッシュメモリに対してリアルタイムデータを記録する機器において、書き込みエラーが発生したときに、書き込みを継続するための手段が、ファイルシステムとは無関係な独自形式であるため、ファイルシステムによりデータを記録するシステムには適合できない。

【解決手段】複数のアクセスユニットで構成されるメモリを有する記録装置であって、前記メモリにデータをアクセスユニット単位で記録する記録手段と、前記記録手段で前記データを前記メモリに書き込んでいるときに、書き込みエラーを検出する書き込みエラー検出手段とを備え、前記記録手段は、前記書き込みエラー検出手段で書き込みエラーが検出されたときに、ファイルの書き込みを終了する。

(もっと読む)

電動パワーステアリング装置

【課題】電動パワーステアリング装置の安全性を向上させること。

【解決手段】CPU101、ROM102、RAM103は、電動パワーステアリング装置の制御に用いられる。RAM103は、電動パワーステアリング装置の複数の機能の内の電動パワーステアリング装置の安全性に関する機能で使用される第1の領域と、複数の機能の内の電動パワーステアリング装置の安全性に関しない機能で使用される第2の領域と、に分割されている。CPU101は、第1の領域及び第2の領域を領域毎に診断する。

(もっと読む)

フラッシュメモリ制御装置及び方法

【課題】データ書き換え回数を増加させると共に、フラッシュメモリを有効活用する。

【解決手段】フラッシュメモリ制御装置は、演算部と、フラッシュメモリとを具備している。フラッシュメモリは、複数の領域DA1〜DA3、PA1〜PA3を有している。複数の領域DA1〜DA3、PA1〜PA3は、演算部により実行されるプログラムが格納され、データの書き換えが行われないプログラム領域PA1〜PA3と、データが格納され、データの書き換えが行われるデータ領域DA1〜DA3とを含んでいる。演算部は、データ領域DA3/DA1/DA2として割り当てられた第1領域に対して、データが書き込まれた累積回数が最大書き換え回数に達したときに、入れ替え処理を実行する。入れ替え処理では、第1領域と、プログラム領域PA3/PA2/PA1として割り当てられた第2領域とを入れ替える。

(もっと読む)

記録装置及びその制御方法

【課題】代替ブロックを有する記録媒体において、ファイルシステム情報の正常な更新をより確実に行えるようにする。

【解決手段】記録装置は、不良ブロックのための代替ブロックを含む複数のブロックを有する記録媒体に対し、所定のファイルシステムに従ってデータをファイルとして記録するとともに、前記ファイルを管理するためのファイルシステム情報を記録する。記録媒体に記録されたデータは所定のファイルシステムに従って管理される。記録装置は、ファイルシステム情報を更新するのに必要なデータサイズに基づいて閾値を設定し、記録媒体における代替ブロックの残量が閾値以下の場合に当該記録媒体に対するデータの記録を禁止する。上記閾値は、前記ファイルシステム情報を更新するのに必要なデータサイズ以上の代替ブロックの残量が確保されるように設定される。

(もっと読む)

情報処理装置、メモリ管理方法、およびメモリ管理プログラム

【課題】データを効率的に冗長化し、システムの安定化を図ることが可能な情報処理装置、メモリ管理方法、およびメモリ管理プログラムを提供する。

【解決手段】情報処理装置は、データを記憶するための記憶装置を用いる。情報処理装置は、記憶装置よりも高速にアクセス可能であり、複数の記憶領域を論理的に設けることが可能なメモリ102と、メモリ102を管理するためのメモリ管理部151とを備える。メモリ管理部151は、複数の記憶領域の中で使用状態が遷移する対象記憶領域が、記憶装置に対象記憶領域のデータのコピーが格納される第1の使用状態へ遷移するか記憶装置に対象記憶領域のデータのコピーが格納されない第2の使用状態へ遷移するかに基づいて、対象記憶領域に他の記憶領域を冗長記憶領域として割り当てて対象記憶領域のデータのコピーを格納するか否かを決定する。

(もっと読む)

記録装置及び方法

【課題】代替ブロックを有する記録媒体において、正常なデータ記録をより確実に行えるようにする。

【解決手段】所定数のバイトからなるブロックを単位としてデータの書き込みが可能なフラッシュメモリを有し、全ブロックのうちの一部を正常なデータの書き込みができなくなった不良ブロックの代替ブロックとして用いる機能を有する記録媒体のためのデータ記録装置は、所定数のブロックに対応するデータ量を書き込み単位として、データファイルの一部としてデータを記録媒体へ送信する。そして、次に送信されるデータの全てが代替ブロックに記録された場合にファイルシステムがデータファイルを管理するための管理情報の記録に必要なブロック数の代替ブロックを確保できなくなると判定されると、以降のデータの書き込みを禁止し、管理情報を更新する。

(もっと読む)

記憶装置

【課題】揮発性メモリからアドレステーブルが消失された場合であっても、予備ブロックに対してデータのアクセスを行うことができる記憶装置を提供すること。

【解決手段】データブロック領域と予備ブロック領域とを備える不揮発性メモリ44bと、不良ブロックの先頭アドレスと当該不良ブロックを代替する予備ブロックの先頭アドレスとを対応させて構成されるアドレス対を記憶する揮発性メモリ44aと、アドレス対を参照することによって不良ブロックに代替された予備ブロックにアクセスする制御部45と、を備える。制御部45は、揮発性メモリ44aからアドレス対が消失している場合、予備ブロック領域へアクセスし、予備ブロックの先頭アドレスと当該予備ブロックに記憶されている不良ブロックの先頭アドレスを読み出し、予備ブロックの先頭アドレスと不良ブロックの先頭アドレスのアドレス対を生成し、生成したアドレス対を揮発性メモリ44aに記憶する。

(もっと読む)

電子機器

【課題】アプリケーションプログラムがバッドブロックを意識せずにデータの書き込みや読み出しを効率的に行うことができる電子機器を提供すること。

【解決手段】不揮発性メモリ44bと、不揮発性メモリ44bの所定のブロックに対してアクセスを行う複数のアクセス制御部45aと、不良ブロックの先頭アドレスと、当該不良ブロックを代替する正常なブロックの先頭アドレスとが対応付けて構成されるアドレス対を記憶する揮発性メモリ44aと、複数のアクセス制御部45aのいずれかによって所定のアドレスが指定されて不揮発性メモリ44bの所定のブロックに対してアクセスが行われたときに、当該ブロックが不良ブロックであった場合、アドレス対を参照して当該ブロックに代替する正常なブロックのアドレスを取得し、取得した当該アドレスが付されているブロックにアクセスを実行するアクセス実行部45bを備える。

(もっと読む)

メモリ障害処理システム、および、メモリ障害処理方法

【課題】予備メモリ切替とページ閉塞とを効率的に連動させてシステムダウンを防止するメモリ障害処理システムを提供すること。

【解決手段】メモリチップ21および予備メモリチップ22を有するメモリ装置2と、メモリチップ21の障害の発生回数総和をカウントする発生回数総和カウント部31と、発生回数総和が総和閾値を超えると故障したメモリチップ21を予備メモリチップ22に切り替える予備メモリチップ切替部32と、切替後の障害の発生回数をキャッシュライン単位でカウントするキャッシュライン単位カウント部33と、切替後の発生回数総和が総和閾値を超える前にキャッシュライン単位発生回数がキャッシュライン単位閾値を超えるとメモリページを閉塞し、キャッシュライン単位発生回数がキャッシュライン単位閾値を超える前に切替後の発生回数総和が総和閾値を超えた以降は障害発生毎にメモリページを閉塞するページ閉塞部34とを有する。

(もっと読む)

記憶装置、及び記憶装置の制御方法

【課題】冗長系を持ちつつ、なお、データ転送速度の要求と書換回数に抗した信頼性の維持が可能とする。

【解決手段】複数のバス(バス0〜3)の各々に接続される複数の不揮発性半導体素子(NAND−Flash7)で構成される系をA系とB系の両方の系を有し、A系の不揮発性半導体素子(NAND−Flash7)が接続されるバス(バス0〜3)が異なるとB系の不揮発性半導体素子が接続されるバス(バス4〜7)が異なるように対応づけ、書込要求或いは読出要求に対して、同じバスに接続された不揮発性半導体素子(NAND−Flash7)が続けて選択されないようにA系とB系の一方の系における不揮発性半導体素子(NAND−Flash7)を選択し、選択された不揮発性半導体素子(NAND−Flash7)に対して前記対応付けに基づいて他方の系における不揮発性半導体素子(NAND−Flash7)を選択する。

(もっと読む)

1 - 20 / 112

[ Back to top ]