Fターム[5B018QA15]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | ライト動作時 (491)

Fターム[5B018QA15]に分類される特許

1 - 20 / 491

半導体記憶装置

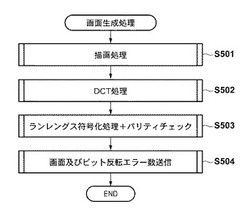

描画サーバ、センタサーバ、符号化装置、制御方法、符号化方法、及びプログラム

【課題】符号化処理を利用した効率的なメモリ検査を行う。

【解決手段】検査対象のメモリについてパリティ情報を付加したデータをメモリに書き込んだ後、該データをメモリから読み出してランレングス符号化処理を行って符号化データを生成する。符号化装置は、書き込まれたデータについてビット列を参照して符号化データを生成する際に、該ビット列と付加されているパリティ情報とを比較してビット反転エラーを検出する。

(もっと読む)

不揮発性メモリにおける書き込み欠陥からのデータ保護

【課題】メモリ装置の書き込み欠陥からデータを保護するための方法及びシステムを提供する。

【解決手段】この方法は、データアイテムのセットにわたる冗長情報を計算し、データアイテムを、メモリに記憶するために送信することを含む。冗長情報は、データアイテムがメモリに首尾良く書き込まれるまでの間のみ保持され、次いで、破棄される。データアイテムは、それをメモリに書き込むのに欠陥が生じたとき、冗長情報を使用して回復される。

(もっと読む)

ICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等

【課題】適切な保護機能によってデータを保護することにより、データの保護機能による処理時間の短縮を図るICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等を提供する。

【解決手段】CPU6は、「カードOSによる非更新領域の保護機能」と、「トランザクションによる更新領域の保護機能」とを備え、「トランザクションによる更新領域の保護機能」は、更新前の更新領域が属するページの全ての領域を更新領域として、当該ページに記憶される全てのデータを前記バックアップ領域に書き込み、当該ページに非更新領域が存在しないものとしてカードOSに通知して、「カードOSによる非更新領域の保護機能」を機能させない。

(もっと読む)

メモリコントローラ、半導体記憶システムおよびメモリ制御方法

【課題】パリティデータデータの増大を抑えることができるメモリコントローラを得ること。

【解決手段】各しきい値分布に対して、3ビットのデータが割り当てられ、第1のビットが第1ページのデータを表現し、第2のビットが第2ページのデータを表現し、第3のビットが第3ページのデータを表現する3ビット/セルのメモリセルを有する不揮発性半導体メモリを制御するメモリコントローラであって、不揮発性半導体メモリの第1のメモリ領域に、第1〜第3の3ページ分のデータを書き込む場合に、第1のメモリ領域の各メモリセルに書き込まれるデータの第1のビット及び第2のビットから、隣接するしきい値分布への移動によりエラーとなるビットを抽出して仮想ページを生成する制御部と、仮想ページに対する第1の誤り訂正符号を生成する符号化部と、3ページ分のデータと第1の誤り訂正符号とを不揮発性半導体メモリへ書き込むインターフェイス部とを備える。

(もっと読む)

メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品

【課題】メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品を提供する。

【解決手段】メモリの寿命を縮める動作を遅延させるシステム500は、複数のストレージデバイス530、540を含むストレージシステム503が含まれている。コマンドの少なくとも一部は、寿命を縮めるコマンドであり、少なくとも一つのモジュール又はブロック531、532、533、541、542、543への悪影響を有する。使用中に、装置510は、そのような寿命を縮めるコマンドに拠らず、ストレージデバイス530、540の寿命を延ばすように働く。使用時に、メモリの寿命に関連する少なくとも一つの特徴が、特定される。このために、メモリの寿命を縮める少なくとも一つの動作が、当該特徴に基づいて遅延される。

(もっと読む)

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

プログラム、情報処理システム、情報処理装置、および情報処理方法

【課題】他のデータに対するアクセスにより生じるエラーから特定のデータを保護できるプログラム、情報処理システム、情報処理装置、および情報処理方法を提供する。

【解決手段】例示的な実施の形態は、コンピュータで実行される、1つのメモリセルに複数ビットを記憶可能な半導体記憶手段に対してデータを書き込むためのプログラムを提供する。プログラムは、コンピュータに、第1のデータを記憶するための第1の領域を半導体記憶手段の記憶領域内に割り当てる割当ステップと、第1のデータの書込要求に応答して、第1の領域の境界から所定のサイズを保護領域とし、残りの領域を使用領域として、第1のデータを使用領域のみに書き込む書込ステップとを実行させる。

(もっと読む)

メモリコントローラ

【課題】半導体メモリを効率的に利用可能なメモリコントローラを提供すること。

【解決手段】実施形態のメモリコントローラ20は、第1インターフェイス21と、第2インターフェイス23と、制御部24とを備える。第1インターフェイス21は、ホスト10との間で信号を送受信する。第2インターフェイス23は、不揮発性の半導体メモリ30との間で信号を送受信する。制御部24は、第1インターフェイス21で受信した第1コマンドに応答して半導体メモリ30に予備領域を確保し、半導体メモリ30に保持されるデータの更新時には予備領域に更新データを書き込む。予備領域のサイズは、第1コマンドに応じて可変である。

(もっと読む)

メモリシステムとその制御方法

【課題】 データを確実且つ高速に書き込むことが可能なメモリシステムとその制御方法を提供する。

【解決手段】 メモリシステムは、第1、第2のディストリクト31a、31bと、制御部21を含んでいる。第1、第2のディストリクト31a、31bは、それぞれメモリセルアレイ32を有する。制御部21は、第1、第2のディストリクト31a、31bへ同時に第1のデータを書き込むための書き込みコマンド及びアドレスを受け、第1、第2のディストリクト31a、31bに同時に第1のデータを書き込む。

(もっと読む)

情報処理装置および情報処理方法

【課題】複数の半導体メモリをストレージとして用いる場合のトータル的な応答性の向上を図ることのできる情報処理装置を提供する。

【解決手段】この情報処理装置は、複数の半導体メモリそれぞれの物理的特性を評価して、評価結果に見合った用途属性を、少なくとも一部の半導体メモリに割り当てる割当部と、データのライト命令に対して当該データのライト先として最適な用途属性の前記半導体メモリを判定する判定部とを具備する。複数の半導体メモリの物理的特性に個体差がある場合に、その半導体メモリの物理的特性が活かされるようにデータのライト先が判定部にて判定される。これにより、複数の半導体メモリを1つのストレージとして用いた場合のストレージのトータル的な応答性の向上を期待できる。

(もっと読む)

情報処理装置および方法、並びに記録媒体

【課題】データの記録方式などが用途に応じて最適になるようにする。

【解決手段】記録媒体に記録されるデータの特性であって、当該データの保持期間を表す寿命値および当該データを読み出したときに発生すると想定されるエラーの割合を表すエラーレートを含む特性に基づいて、前記記録媒体により構成される論理デバイスの記録領域を複数生成するとともに、前記記録領域のそれぞれに適用される記録方式を決定する記録方式決定部と、前記決定された記録方式に基づいて、前記論理デバイスの記録領域のそれぞれを初期化する論理デバイス初期化部とを備える。

(もっと読む)

ICチップ、ICチップにおける処理方法、及びICチップ用処理プログラム

【課題】処理中断によりトランザクションが行われた場合であっても、処理時間制約が厳しい方のインターフェイスを用いた処理を正常に行うことが可能なICチップ、ICチップにおける処理方法、及びICチップ用処理プログラムを提供する。

【解決手段】ICチップは複数のインターフェイスに対応した処理手段と、データを記憶するデータ記憶領域と前記データをバックアップするためのバックアップ領域と、を有する不揮発性メモリと、第1の前記インターフェイスを用いた処理により受信されたデータを前記データ記憶領域に書き込む際に前記データ記憶領域に記憶されているデータを前記バックアップ領域にバックアップし、前記第1の前記インターフェイスを用いた処理が中断された場合には、前記バックアップ領域にバックアップされている前記データを前記記憶領域に書き戻す処理を行う制御手段と、を備える。

(もっと読む)

車両用電子制御装置

【課題】別の処理により使用されるメモリ領域に誤ってデータが書き込まれてしまう可能性を抑える。

【解決手段】電子制御装置が備えるCPUは、燃料噴射制御、点火制御及び電子スロットル制御処理を含む複数種類の制御処理を実行する。このCPUは、ベースレジスタが記憶する基準アドレスに、指定された相対アドレスを加算して実効アドレスを算出し、この実効アドレスに基づき、ストア命令及びロード命令に対応するRAMへのアクセスを行う構造を備える。各制御処理では、命令の発行時に、相対アドレスにより、アクセス先のメモリアドレスを指定する。また、各制御処理に対しては、異なる基準アドレスが割り当てられ、各制御処理の実行開始前には、ベースレジスタの値が、これから実行される制御処理に割り当てられた基準アドレスに更新される。この動作により、各制御処理に対しては、重複しない独立性の高いメモリ領域が割り当てられる。

(もっと読む)

メモリコントローラ、不揮発性記憶装置

【課題】不揮発性メモリにおいて第1の誤り訂正符号の訂正能力を超えるエラーが発生した場合でも、格納したデータを正しく読み出すことが可能で、かつ、小さいサイズの書き込みが効率的な不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置1は、データを記憶する不揮発性メモリ12と、不揮発性メモリ12の制御を行うメモリコントローラ11とを備え、メモリコントローラ11は、データと同一ページに格納する第1の誤り訂正符号とは別に、第2の誤り訂正符号をも格納する。第2の誤り訂正符号の単位となるパリティグループよりもサイズの小さい書き込みにおいては、パリティグループとは別の領域に暫定的な第2の誤り訂正符号を格納する。データの読み出し時にはデータに付与された第1及び/または第2の誤り訂正符号を用いてエラー訂正を行う。

(もっと読む)

メモリコントローラ及び不揮発性記憶装置

【課題】不揮発性メモリにてワード線不良によるバースト誤りが発生した場合も、格納したデータを正しく読み出せる不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置は、データを記憶する不揮発性メモリと、不揮発性メモリの制御を行うメモリコントローラとを備え、不揮発性メモリは、ブロックを複数含み、ブロックは、ページを複数含み、ブロック内には、一つのワード線を共有する2以上のページからなるページの組が少なくとも一つ存在し、メモリコントローラは、データを格納するページであるデータページと、データページの誤り訂正演算のための符号を格納する誤り訂正符号ページとを、夫々一つ以上含む、誤り訂正グループを複数構成し、同一の誤り訂正グループにおける、データページと誤り訂正ページの夫々に対してワード線の異なるページを割り当てる。

(もっと読む)

データ記憶制御装置、データ記憶制御方法およびプログラム

【課題】画像データをバックアップとして保存する際に不揮発性記憶手段に対する書き換え回数を低減し、不揮発性記憶手段の長寿命化を図る。

【解決手段】データ記憶制御装置2は、所定容量の記憶領域を有する1次メモリ11と、1次メモリ11よりも大容量であり、その記憶領域が複数のブロックに分割されると共に、ブロック単位でデータが消去され、データの消去されたブロックに対してデータの書き込みが可能な2次メモリ12とを備える。制御部23は、画像データ取得部21によって取得される画像データのうち、2次メモリ12における1ブロックの整数倍となるデータ部分を2次メモリに記憶すると共に、残余のデータ部分を1次メモリ11に記憶し、バックアップデータ取得部22によって取得されるバックアップデータを1次メモリ11に記憶させた残余のデータ部分と組み合わせて2次メモリ12の1つのブロックに記憶する。

(もっと読む)

不揮発性半導体記憶装置およびメモリ管理方法

【課題】より少ないステータス情報領域で、ステータス異常に対応することができる不揮発性半導体記憶装置およびメモリ管理方法を提供する。

【解決手段】不揮発性メモリに対し、メモリセルブロック単位での一括消去処理、予め定められたアドレス数の記憶領域単位またはビット単位での書き込み処理、および、メモリセルブロック単位で、データ更新元メモリセルブロックからデータ更新先メモリセルブロックへ予め定められたデータを転送するデータ更新処理の制御を行うメモリ制御部と、を備え、複数のメモリセルブロックは、それぞれ、該メモリセルブロックの使用状態に関する情報を含むステータス情報を記憶するためのステータス情報記憶領域と、該メモリセルブロックのデータ更新処理における更新履歴を含む更新履歴情報を記憶する更新履歴情報記憶領域と、を備え、ステータス情報および更新履歴情報に基づいて、現在使用中のメモリセルブロックを特定する。

(もっと読む)

フラッシュメモリにデータの書き込みを行う制御装置

【課題】 フラッシュメモリにデータを記録する技術において、記憶しているデータが消失する可能性をより低減させる。

【解決手段】ブロック1のデータ消去時に、データの最新値が保存されているブロック2のブロックIDを、管理ブロックに書き込み、その後、ブロック1のデータ消去を行う。制御装置がリセットから復帰した後、使用中である旨のブロックステータスとなっているブロックが2個あった場合、当該2個のブロックのうち、管理ブロック中の上記ブロックIDを有するブロック(ブロック2)とは異なるブロック(ブロック1)のデータ消去を行う。

(もっと読む)

1 - 20 / 491

[ Back to top ]