Fターム[5B022FA06]の内容

Fターム[5B022FA06]の下位に属するFターム

可変精度 (2)

Fターム[5B022FA06]に分類される特許

1 - 19 / 19

ルートi(√i)演算の保持を特徴とする基数8固定小数点FFT論理回路

【課題】 高速フーリエ変換(FFT)演算の丸め誤差を軽減させること。

【解決手段】 バタフライ演算(8p)に含まれる複素平面上の回転因子のうちで、無理数(√、平方根)として現れるデータを意図的に計算することなく、多段にパイプライン化されているFFTの複数の段のうちの1つの段に設けられているメモリに保持(preserve)しておき、後段において再度現れたきたら、2つの回転因子を掛け合わせる演算を行う。このことによって、基数8 (radix-8)のバタフライ演算8p中の丸め誤差を無くすることができる。基数2 (radix-s)または基数4 (radix-4)のバタフライ演算によって、さらなる段を被せるように応用することもできる。

(もっと読む)

浮動小数点数演算回路と浮動小数点演算方法及びサーボ制御装置

【課題】単精度演算を行う回路で切り捨てられるガードビットを有効に利用して、ゲート数が少なく、コスト面、高速性に優れ、また、特に累算において精度の高い浮動小数点数演算回路を提供する。

【解決手段】仮数演算部4に付加ビット列を生成する付加ビット生成器9を備え、余りビット列から余り仮数と指数調整値を生成する余り仮数生成部12と、指数と指数調整値から余りビット列の余り指数を生成する余り指数生成部11とを有する余り正規化部7と、余り正規化部7で生成された余り指数と余り仮数を用いて余りの丸めを行い余り出力を生成する余り丸め部8とを浮動小数点演算部1に備えると共に、余り出力を記憶する余り記憶部13を備える。

(もっと読む)

半導体集積回路

【課題】累積加算又は積和演算等を行う場合にビット精度を向上させ、無駄なリソースの発生を防止することができる半導体集積回路を提供することを課題とする。

【解決手段】第1のビット幅のデータを入力し演算を行う複数の再構成可能な第1の論理ブロック(111)と、前記複数の第1の論理ブロック間を動的再構成可能に接続する第1のネットワーク(112)と、前記第1のビット幅とは異なる第2のビット幅のデータを入力し演算を行う複数の第2の論理ブロック(121)と、前記複数の第2の論理ブロックの出力に接続される第2のネットワーク(122)と、前記第1の論理ブロックに含まれる演算器のキャリビット出力を、前記第2の論理ブロックに含まれる演算器の入力に動的再構成可能に接続する第3のネットワーク(120)とを有することを特徴とする半導体集積回路が提供される。

(もっと読む)

組み込み制御装置

【課題】浮動小数点数形式のデータによる演算精度を確保し、且つ、記憶装置の記憶領域の不足を回避することができる組み込み制御装置を提供する。

【解決手段】本発明による組込み制御装置によると、浮動小数点数形式の離散的データを読み取り専用記憶装置に格納するとき、浮動小数点数形式の離散的データを、仮数部短縮型浮動小数点数形式のデータに変換してから格納する。ここに、仮数部短縮型浮動小数点数とは、浮動小数点数の仮数部のうち下位ビットを削除したものである。更に、離散的データから補間演算を行うとき、読み取り専用記憶装置に格納された仮数部短縮型浮動小数点数形式の離散的データを浮動小数点数形式の離散的データに戻してから、補間演算を行う。

(もっと読む)

単精度浮動小数点データの格納方法およびプロセサ

【課題】単精度浮動小数点データおよび倍精度浮動小数点データを扱うプロセサにおいて、新しい単精度浮動小数点データの格納方式を提案し、バイパス機能のための依存関係検出回路を構成するハードウェア量を可能な限り低減すること。

【解決手段】倍精度浮動小数点データを格納可能な大きさを有する、倍精度浮動小数点データと単精度浮動小数点データとが格納されるレジスタを備えるプロセサにおいて、単精度浮動小数点データ処理が指定された場合、前記レジスタの上位半分に入力した単精度浮動小数点データを書き込むとともに、前記レジスタの下位半分にオールゼロを書き込む、単精度浮動小数点データ格納方式。

(もっと読む)

半導体装置

【課題】圧縮された設定情報から遅延を生じることなく設定情報を復号し、実行回路を構築して演算を行えるようにする。

【解決手段】 第1設定ビットよりもビット長が短い第1符号情報を記憶しており、各符号情報に対応する各設定ビットを表す辞書情報を受信し、前記第1符号情報に対応する設定ビットを前記辞書情報から読み出すことにより前記第1設定ビットを求め、該第1設定ビットに従い設定を変更することにより複数の演算のいずれかを行って演算結果を得る第1の演算ユニットと、第2設定ビットよりもビット長が短い第2符号情報を記憶しており、前記辞書情報を前記第1の演算ユニットから受信し、前記第2符号情報に対応する設定ビットを前記辞書情報から読み出すことにより前記第2設定ビットを求め、該第2設定ビットに従い設定を変更することにより前記演算結果に対して前記複数の演算のいずれかを行う第2の演算ユニットとを具備する。

(もっと読む)

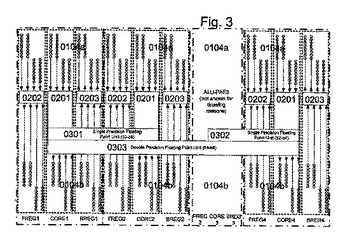

リコンフィギュラブルな浮動小数点レベルおよびビットレベルのデータ処理ユニット

リコンフィギュラブルなデータ処理ユニットの複数の固定小数点ユニットのブロックが、該ブロック内に固定実装された共通の同じハードウェアによって、浮動小数点数を効率的に演算する機能を支援する。  (もっと読む)

(もっと読む)

計算装置及び計算プログラム

【課題】従来と比較して装置の大型化を防ぎつつ、計算誤差の有無を判断する。

【解決手段】関数電卓1は、演算桁数「n」を記憶する演算桁数格納領域62と、ユーザ操作に基づいて数値計算式を入力する入力部20と、数値計算式を演算桁数「n」で計算する十進演算器70と、入力された数値計算式に含まれる各計算数値の仮数部の桁数が演算桁数「n」以下であるか否かに基づいて、当該各計算数値中の誤差の有無を判別し、何れかの計算数値が誤差有りと判別された場合に、十進演算器70による計算結果が誤差有りであると判別するCPU40と、十進演算器70による計算結果及びCPU40による判別結果を表示する表示部30と、を備える。

(もっと読む)

演算プログラム変換装置、演算プログラム変換プログラム、演算プログラム変換方法

【課題】演算プログラムにおける浮動小数点演算を、所望精度を確保しながら固定小数点演算に変換する演算プログラム変換装置、演算プログラム変換プログラム、演算プログラム変換方法を提供する。

【解決手段】浮動小数点演算を行う演算プログラムにおける浮動小数点型の変数を対象変数とし、演算プログラムの実行時に対象変数の値の変化が履歴として出力されるように、演算プログラムの変更を行って実行を行い、該実行により得られる履歴に基づいて対象変数の値の範囲を検出するプロファイル部と、プロファイル部により検出された対象変数の値の範囲に基づいて、対象変数を固定小数点型に変換するように、演算プログラムの変更を行って実行を行い、該実行により得られる実行結果の精度が予め設定された所望精度を満たすか否かの判断を行う変換部とを備えた。

(もっと読む)

選択可能な副精度に対して、低減された電力要求を有する浮動小数点プロセッサ

所定の精度を有する浮動小数点プロセッサにより浮動小数点演算を実行する方法および装置を開示する。1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度が選択される。副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらす。さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから、電力を取り除くことができ、浮動小数点演算は、1つ以上のコンポーネントから電力を取り除いた状態で実行される。 (もっと読む)

電子制御装置、非数判定方法及びプログラム

【課題】 非数の発生箇所を正確に特定し、非数の発生に伴う制御不良を未然に防止することを目的とする。

【解決手段】 制御ECU1は、関数の演算を行う演算手段と、関数の演算の処理過程で導出された変数が非数であるか否かを判定する非数判定手段と、関数又は関数内の所定演算ごとの非数判定結果を、関数又は所定演算の識別情報に関連付けてRAM30に書き込む書込み手段とを備えている。従って、非数の発生箇所を正確に特定し、非数の発生に伴う制御不良を未然に防止することができる。

(もっと読む)

選択可能な下位精度を有する浮動小数点プロセッサ

選択可能な下位精度を有する浮動小数点プロセッサ

選択可能な下位精度を有する浮動小数点プロセッサは浮動小数点フォーマット内の複数のビットを蓄積するように構成されたレジスタ、コントローラ、および浮動小数点数学演算子を含む。コントローラは、ユーザ入力に応じて、浮動小数点演算子のための下位精度を選択するように構成される。コントローラは、選択された下位精度に従って、ビットのサブセットを決定するように構成される。浮動小数点演算子はビットのサブセットのみを使用して浮動小数点演算を実行するように構成される。浮動小数点演算子内で使用されない過剰ビットは低漏洩状態内に押し込まれてもよい。浮動小数点演算に起因する出力値は選択された下位精度に切り詰められるかまたはまるめられる。  (もっと読む)

(もっと読む)

演算処理装置および情報処理装置

【課題】倍精度演算に比べて、演算回数が少なく、タスクの切替え時間を増加させずに、かつ演算精度が向上した演算処理装置を提供する。

【解決手段】演算処理装置は、演算処理に関するデータを保持する汎用レジスタと、演算処理装置の状態に関する情報を保持するプログラムステータスレジスタ10とを含み、割込み処理やタスクを切り換える際に、データおよび情報は退避される。プログラムステータスレジスタ10は領域C1〜Cnに、演算処理の結果得られたデータの一部を保持する。保持されるデータは、演算処理の結果得られたデータのうち、汎用レジスタに保持されない下位桁のデータの上位nビットである。このデータを、演算に利用する。

(もっと読む)

データプロセッサ、データ処理方法及び演算制御プログラム

【課題】 演算装置による有効な演算ビット数を拡張することなく関数の近似多項式による演算精度を向上させる。

【解決手段】 データ処理ユニット(20)は、演算制御プログラムに従って所定の関数の値を演算するとき、近似多項式F(x)を分解した和の多項式F1(x)+F2(x)を用いる。前記式F1(x)は前記データ処理ユニットの演算精度に対して正確に計算可能な次数と係数を有しF1(x)=BIG+SMALLとして表現可能である。F1(x)の絶対値はF2(x)の絶対値よりも大きい。BIGの絶対値はSMALLの絶対値よりも大きい。前記多項式F1(x)+F2(x)を用いた演算において、F(x)=BIG+SMALL+F2(x)を求めるとき、BIG+(SMALL+F2(x))の演算を行う。これにより、絶対値の小さいもの同士の加算で生じた丸め誤差はBIGに対して1度だけ作用する。丸め誤差が累積して大きな演算誤差を生ずる方向に最終解が丸められる可能性を低減することができる。

(もっと読む)

演算装置および型変換装置

【課題】 IEEE754規格よりも短い語長で同じ指数範囲を表現した数値形式を用いつつ、IEEE754規格の数値形式の処理フローで演算処理が行なえる演算装置を提供すること。

【解決手段】 ソース型変換部0(1)およびソース型変換部1(2)は、可変長の指数部および仮数部を含んだ浮動小数点の数値形式を、IEEE754規格の浮動小数点の数値形式に変換する。指数・仮数固定長形式浮動小数点演算器3は、ソース型変換部0(1)およびソース型変換部1(2)によって変換された固定長の指数部および仮数部を用いて浮動小数点演算を行なう。デスティネーション型変換部4は、指数・仮数固定長形式浮動小数点演算器3による演算結果を可変長の指数部および仮数部を含んだ浮動小数点の数値形式に変換する。したがって、IEEE754規格よりも短い語長で同じ指数範囲を表現した数値形式を用いつつ、IEEE754規格の数値形式の処理フローで演算処理を行なうことが可能となる。

(もっと読む)

浮動小数点数値のm乗根を演算する浮動小数点演算装置及びコンピュータプログラム

【課題】浮動小数点演算ユニットの演算ビットが固定小数点演算ユニットの演算ビットよりも多いときには、浮動小数点数値の演算精度が低くなってしまう。

【解決手段】演算対象である浮動小数点数値の指数部を0乗値に置き換え、その置き換えた浮動小数点数値のm乗根を演算する。そして、その演算結果と、演算対象である浮動小数点数値の指数部のm乗根を演算した結果とに基づいて、浮動小数点数値のm乗根(m≧2:mは整数)を演算する。さらに、浮動小数点数値のm乗根を演算した後、その浮動小数点数値をp乗することによって、m分のp乗根を演算する。

(もっと読む)

演算処理装置

【課題】 固定小数点型演算処理装置をもとに、演算処理回数及び回路規模をほとんど増加させずに、従来の固定小数点方式と高い互換性を保ちながら浮動小数点型演算処理装置に近い処理を行わせる。

【解決手段】 浮動小数点数の仮数部のみが入力されると、乗算処理を行う乗算回路と、乗算回路の演算結果が入力されると、外部から与えられるシフト命令によるシフト量と乗算回路の入力の一方または両方の指数部の値とに基づき求められるシフト量のシフト演算処理を行うシフト回路と、シフト回路の演算結果と、レジスタおよび/またはメモリに記憶された情報とが入力されると、加算処理を行うことにより、仮数部と指数部とからなる浮動小数点データを固定小数点データに変換した演算空間で固定小数点演算を行う加算回路とを備え、加算回路は、加算処理の結果をレジスタおよび/またはメモリに記憶する。

(もっと読む)

演算制御装置及びプログラム

【課題】入力された演算桁数で演算を行い、求められた演算結果の正確な桁落ち桁数を検出し、その桁落ちを知らしめる演算制御装置を実現すること。

【解決手段】グラフ関数電卓は、ユーザーにより入力された演算桁数で、指定された演算種類の演算を実行する。その際、その演算により桁落ちした桁落ち桁数を検出する。そして、演算結果と共に、検出した桁落ち桁数を表示する。

(もっと読む)

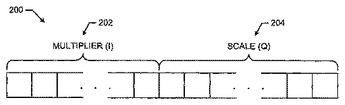

スケールされた整数を用いた浮動小数点演算

複数のスケールされた整数を用いて複数の数学演算を実行するための複数の方法、複数の装置、および複数の製品が開示される。具体的には、一例の方法は、スケールされた整数値を認識し、スケールされた整数値に基づいて、乗数値およびスケール値を決定する。乗数値は、スケールされた整数値に基づいて、ビット領域の第一の部分から情報を抽出することにより決定される。スケール値は、スケールされた整数値に基づいて、ビット領域の第二の部分から情報を抽出することにより決定される。ビット領域の第一の部分および第二の部分は、符号付き整数値を有するように構成することができる。例の方法は、乗数値およびスケール値に基づいて、算術演算を実行する。

(もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]